## **University of Huddersfield Repository**

Haigh, Richard P.

Technology Enhancements for Next Generation Radiation Detectors

#### **Original Citation**

Haigh, Richard P. (2018) Technology Enhancements for Next Generation Radiation Detectors. Masters thesis, University of Huddersfield.

This version is available at http://eprints.hud.ac.uk/id/eprint/34742/

The University Repository is a digital collection of the research output of the University, available on Open Access. Copyright and Moral Rights for the items on this site are retained by the individual author and/or other copyright owners. Users may access full items free of charge; copies of full text items generally can be reproduced, displayed or performed and given to third parties in any format or medium for personal research or study, educational or not-for-profit purposes without prior permission or charge, provided:

- The authors, title and full bibliographic details is credited in any copy;

- A hyperlink and/or URL is included for the original metadata page; and

- The content is not changed in any way.

For more information, including our policy and submission procedure, please contact the Repository Team at: E.mailbox@hud.ac.uk.

http://eprints.hud.ac.uk/

# Technology Enhancements for Next Generation Radiation Detectors

Richard Paul Haigh May 2018

A thesis submitted to the University of Huddersfield in fulfilment of the requirements for the degree of Master of Science by Research

# Copyright

i. The author of this thesis (including any appendices and/ or schedules to this thesis) owns any copyright in it (the "Copyright") and s/he has given The University of Huddersfield the right to use such Copyright for any administrative, promotional, educational and/or teaching purposes.

ii. Copies of this thesis, either in full or in extracts, may be made only in accordance with the regulations of the University Library. Details of these regulations may be obtained from the Librarian. Details of these regulations may be obtained from the Librarian. This page must form part of any such copies made.

iii. The ownership of any patents, designs, trademarks and any and all other intellectual property rights except for the Copyright (the "Intellectual Property Rights") and any reproductions of copyright works, for example graphs and tables ("Reproductions"), which may be described in this thesis, may not be owned by the author and may be owned by third parties. Such Intellectual Property Rights and Reproductions cannot and must not be made available for use without permission of the owner(s) of the relevant Intellectual Property Rights and/or Reproductions.

## Abstract

Portable radiation detectors are becoming widely used across various industries, particularly the security industry to roll out networks of portable detectors for illicit nuclear material detection. The capabilities of modern detectors have rapidly increased in recent years, largely with the use of advancements in photonics technology. This research program demonstrates two versatile methods of maximising the use of state of the art solid state photo multiplier technology and dual gamma neutron scintillation material, by using low power digital and analogue methods where low power consumption in portable devices is essential for longer operation times between battery charges.

A 25 million sample per second analogue to digital converter system is developed and its performance analysed for methods of gamma event energy capture using a basis of well-established principles used in radiation detection. Its architecture flexibility allows the embedding of different applications, where firstly using it similar to a traditional peak capture circuit is evaluated for gamma energy capture. Secondly, the system is evaluated when using continuous or triggered sampling of a silicon photo multiplier array output both with and without prior stages of analogue signal processing, in order to accurately capture the radiation event signal for digital processing of gamma radiation events. The results show 8-bit peak capture accuracy using generated semi – Gaussian input signals simulating scintillation requirements as fast as using a 1  $\mu$ S shaping time at 250,000 events per second. The results also show that the ADC system is able to continuously sample a scintillation event, where the captured data is re-plotted for evaluation, where further on device digital processing methods can yield radiometric information.

A low power analogue based circuit is also developed and evaluated for use with the dual gamma neutron scintillator CLLB. Current pulse shape discrimination methods rely on offline processing of pulse datasets to distinguish between a gamma and a neutron event, where the common method used relies on integration windows. This method when implemented in electronic circuitry as a timer controlled gated integrator can prove challenging to design efficiently and can consume excessive amounts of power which is a disadvantage for a battery powered product. The method used in the implemented analogue circuit relies on a combination of amplitude ratio windowing and pulse height discrimination, where successful discrimination between gamma and neutron events was achieved, and where the circuit depending on configuration and application consumes as low as 14 mW of power.

# Extract Works and Attendances

A summary paper published in the 2017 XXXIInd General Assembly and Scientific Symposium of the International Union of Radio Science (URSI GASS) and presented as part of the URSI 32<sup>nd</sup> GASS conference 19<sup>th</sup> – 25<sup>th</sup> August 2017 was written on works regarding the development of the 25 MSps ADC System and its use in radiation detection methods researched. The paper titled 'Low Power Embedded Processing of Scintillation Events with Silicon Photo Multipliers' explains the benefits of using the developed folding ADC prototype, with the high data conversion benefits and field upgradable firmware for continuous optimal processing of radiation events in a low power solution, intended for battery operated devices and custom applications.

A conference paper accepted for presentation at the 2nd URSI AT-RASC, Gran Canaria, 28 May - 1 June 2018 by D. W. Upton was contributed to as second author. The paper titled 'Low Power High-Speed Folding ADC based Partial Discharge Sensor for Wireless Fault Detection in Substations' explains the analogue architecture and operation of the 25 MSps ADC system in detail, and how the digital control designed and described in this research is implemented in the ADC prototype with the use of the FPGA application written in VHDL. The paper describes how the originally intended application for the ADC was for monitoring potential discharge radio emission occurrences in power grid substations, where the application is similar to that of the ADCs use in a radiation detection application.

The 1st International SPAD Sensor Workshop ISSW 26<sup>th</sup> - 28<sup>th</sup> February 2018 was attended, gaining knowledge of the current and future state of the art in single photon avalanche diode technology, the crucial technology in recent developments in photon capture applications such as in radiation detection and LiDAR imaging.

# Acknowledgements

I would like to acknowledge the following with thanks:

Dr Peter Mather at the University of Huddersfield firstly, for continued support and guidance throughout the research project and writing and secondly, for providing the knowledge base contact throughout the Knowledge Transfer Partnership.

Dr Martin Sibley at the University of Huddersfield for providing a further knowledge base for electronics theory.

Dr Ed Marsden at Kromek Ltd, UK for support with radiation and physics knowledge and providing the company base contact throughout the Knowledge Transfer Partnership.

Dr Alan J Bell, for providing background applicational knowledge from roles at Kromek Ltd and CERN.

Kromek Ltd, UK for contributing resources and knowledge to the research project and participating as the company partner in the Knowledge Transfer Partnership.

Mr David Upton at the University of Huddersfield for collaboration efforts when developing the folding Analogue to Digital converter prototype and initial testing.

Innovate UK, particularly the Knowledge Transfer Network firstly, for the facilitating of the Knowledge Transfer Partnership (KTP) between the University of Huddersfield and Kromek Ltd, UK and secondly, the Masters by Research opportunity provided for myself as the KTP associate of the scheme.

Finally, my parents and partner for their encouragement throughout my undergraduate degree, in to an electronics career and throughout this research.

# Contents

| С                | opyri             | ight | nt                                                         | 1  |  |  |  |  |  |  |

|------------------|-------------------|------|------------------------------------------------------------|----|--|--|--|--|--|--|

| A                | bstra             | ict  |                                                            | 2  |  |  |  |  |  |  |

| E>               | (trac             | t W  | Vorks and Attendances                                      | 3  |  |  |  |  |  |  |

| A                | Acknowledgements4 |      |                                                            |    |  |  |  |  |  |  |

| List of Figures7 |                   |      |                                                            |    |  |  |  |  |  |  |

| Li               | st of             | Tab  | ables                                                      | 10 |  |  |  |  |  |  |

| Li               | st of             | Εqι  | quations                                                   | 10 |  |  |  |  |  |  |

| 1                | Ir                | ntro | oduction                                                   | 11 |  |  |  |  |  |  |

|                  | 1.1               |      | Radiation Monitoring and Radioactive Source Control        | 11 |  |  |  |  |  |  |

|                  | 1.2               |      | Radiation Safety and Monitoring Systems                    | 12 |  |  |  |  |  |  |

|                  | 1.3               |      | Research Aims and Objectives                               | 14 |  |  |  |  |  |  |

|                  | 1.4               |      | Research Structure and Methodology                         | 15 |  |  |  |  |  |  |

| 2                | Li                | iter | rature Review                                              | 17 |  |  |  |  |  |  |

|                  | 2.1               |      | Scintillation overview                                     | 17 |  |  |  |  |  |  |

|                  | 2.2               |      | Scintillation for Neutron Detection                        | 20 |  |  |  |  |  |  |

|                  | 2.3               |      | Dual Gamma Neutron Detection Capable Materials             | 21 |  |  |  |  |  |  |

|                  | 2.4               |      | Discrimination methods                                     | 23 |  |  |  |  |  |  |

|                  | 2                 | .4.1 | 1 Pulse Height Discrimination                              | 23 |  |  |  |  |  |  |

|                  | 2                 | .4.2 | 2 Pulse Shape Discrimination                               | 24 |  |  |  |  |  |  |

|                  | 2                 | .4.3 | 3 Pulse Gradient Detection                                 | 24 |  |  |  |  |  |  |

|                  | 2                 | .4.4 | 4 Evaluating Discrimination Methods and Systems            | 25 |  |  |  |  |  |  |

|                  | 2.5               |      | Radiation Detection Utilising Silicon Photo Multipliers    | 25 |  |  |  |  |  |  |

|                  | 2.6               |      | Scintillation Event Processing Circuitry using SiPMs       | 29 |  |  |  |  |  |  |

|                  | 2.7               |      | Circuitry used for Peak Amplitude Capture                  | 31 |  |  |  |  |  |  |

|                  | 2.8               |      | Spectrum Creation                                          | 34 |  |  |  |  |  |  |

|                  | 2.9               |      | Literature Review Conclusion                               | 36 |  |  |  |  |  |  |

| 3                | Lo                | ow   | Power Digital Solution for Radiation Detection             | 37 |  |  |  |  |  |  |

|                  | 3.1               |      | High Rate Peak Capture                                     | 37 |  |  |  |  |  |  |

|                  | 3.2               |      | Analogue to Digital Conversion Requirements                |    |  |  |  |  |  |  |

|                  | 3.3               |      | Increasing the Sample Rate for Digital Peak Detection      |    |  |  |  |  |  |  |

|                  | 3.4               |      | The High-Speed Pipelined Folding ADC System                |    |  |  |  |  |  |  |

|                  | 3.5               |      | Designing the ADC Data Control Logic using FPGA Technology | 40 |  |  |  |  |  |  |

|                  | 3                 | .5.1 | 1 Clock Control                                            | 41 |  |  |  |  |  |  |

|                  | 3                 | .5.2 | 2 Pipeline Gray Code Data Handling                         | 42 |  |  |  |  |  |  |

|                  | 3.6               |      | Application of the FPGA for ADC Architecture Control       | 44 |  |  |  |  |  |  |

|                  | 3                 | .6.1 | 1 Design of the UART Transmission                          | 45 |  |  |  |  |  |  |

|                  | 3.7               |      | Initial Test Results and Analysis                          | 46 |  |  |  |  |  |  |

|   | 3.8       | Peal                                                                                              | Peak Detection Application47                              |    |  |  |  |  |

|---|-----------|---------------------------------------------------------------------------------------------------|-----------------------------------------------------------|----|--|--|--|--|

|   | 3.9       | Peal                                                                                              | Peak Detection Results and Analysis                       |    |  |  |  |  |

|   | 3.9.      | 1                                                                                                 | Digital Design and FPGA use improvements                  | 51 |  |  |  |  |

|   | 3.10      | Furt                                                                                              | her Implementing Digital Event Processing                 | 51 |  |  |  |  |

|   | 3.10      | D.1                                                                                               | 0.1 Application for Dual Gamma Neutron Scintillators.     |    |  |  |  |  |

|   | 3.11      | Con                                                                                               | Conclusion                                                |    |  |  |  |  |

| 4 | Low<br>55 | ow Power Analogue Solution for Utilising Advanced Dual Gamma Neutron Detection Scintillators<br>5 |                                                           |    |  |  |  |  |

|   | 4.1       | Anal                                                                                              | Analogue Discrimination Method in Principal55             |    |  |  |  |  |

|   | 4.2       | Anal                                                                                              | ogue Discrimination System Design                         | 56 |  |  |  |  |

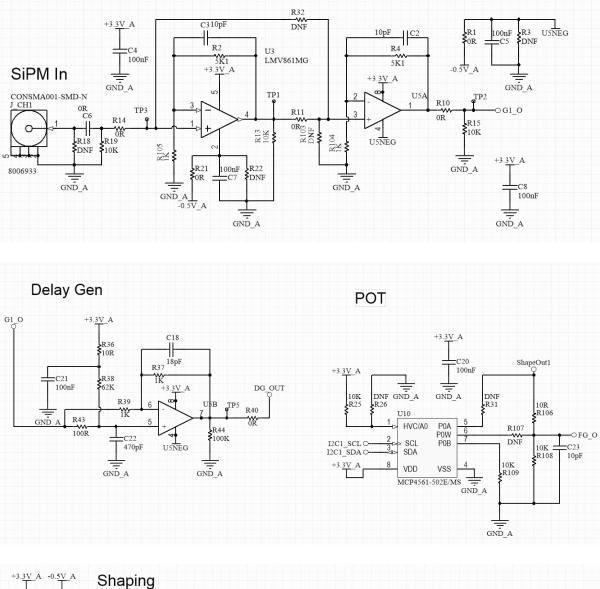

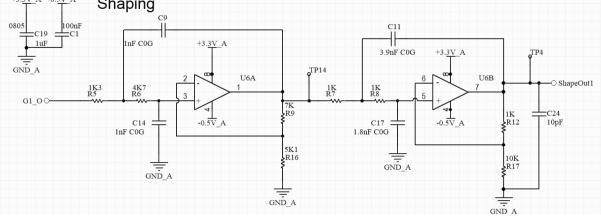

|   | 4.2.      | 1                                                                                                 | Peak Finding                                              | 56 |  |  |  |  |

|   | 4.2.      | 2                                                                                                 | Event Signal Delay Generation                             | 58 |  |  |  |  |

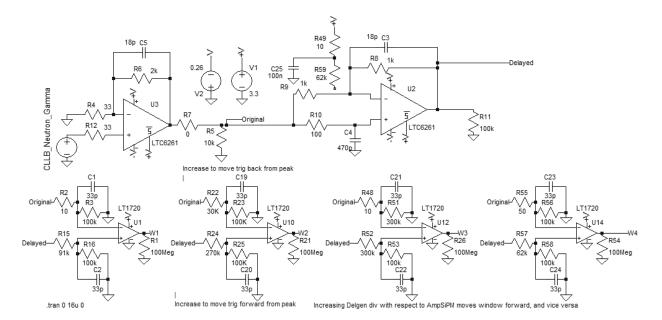

|   | 4.2.      | 3                                                                                                 | Simulating the delay circuit                              | 60 |  |  |  |  |

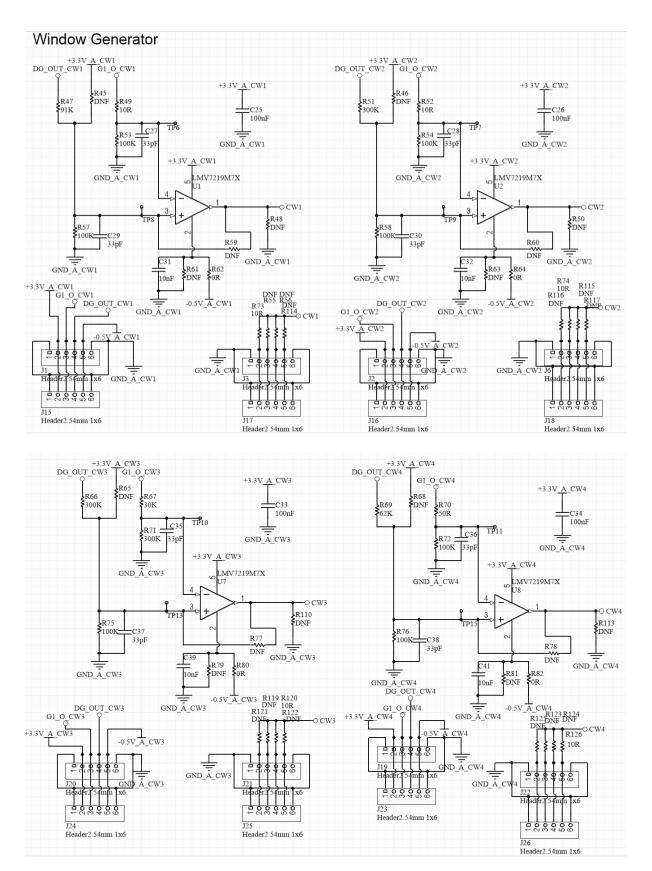

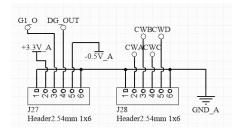

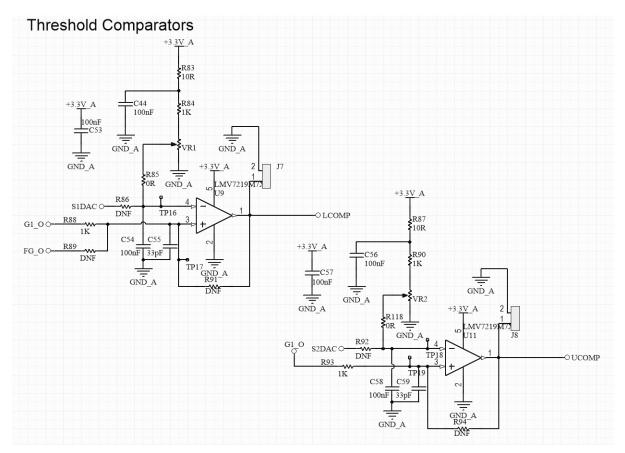

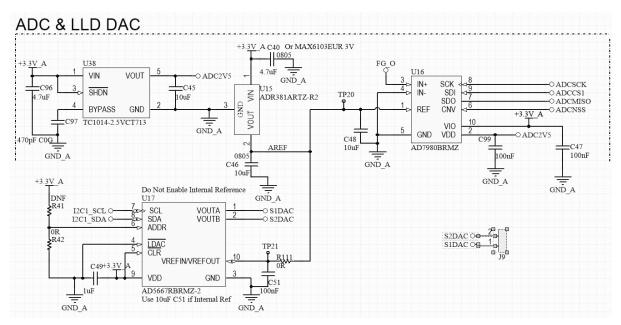

|   | 4.2.      | 4                                                                                                 | Window Generation                                         | 62 |  |  |  |  |

|   | 4.3       | Disc                                                                                              | rimination System Design                                  | 65 |  |  |  |  |

|   | 4.3.      | 1                                                                                                 | FPGA Window Timer and Program Design                      | 65 |  |  |  |  |

|   | 4.3.      | 2                                                                                                 | Simulation of the Discrimination System                   | 66 |  |  |  |  |

|   | 4.4       | Test                                                                                              | ing the Prototype Discrimination Circuit                  | 68 |  |  |  |  |

|   | 4.4.      | 1                                                                                                 | Measuring the Delay Generated                             | 68 |  |  |  |  |

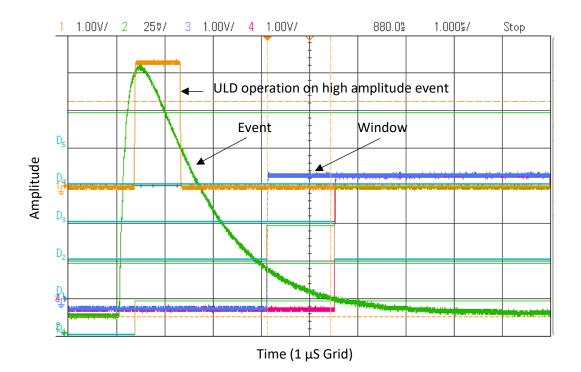

|   | 4.4.      | 2                                                                                                 | Setting the ULD                                           | 68 |  |  |  |  |

|   | 4.5       | Resu                                                                                              | Ilts and Analysis                                         | 69 |  |  |  |  |

|   | 4.5.      | 1                                                                                                 | System Figure of Merit                                    | 71 |  |  |  |  |

|   | 4.5.      | 2                                                                                                 | Power Consumption                                         | 72 |  |  |  |  |

|   | 4.6       | Syst                                                                                              | em Improvements                                           | 72 |  |  |  |  |

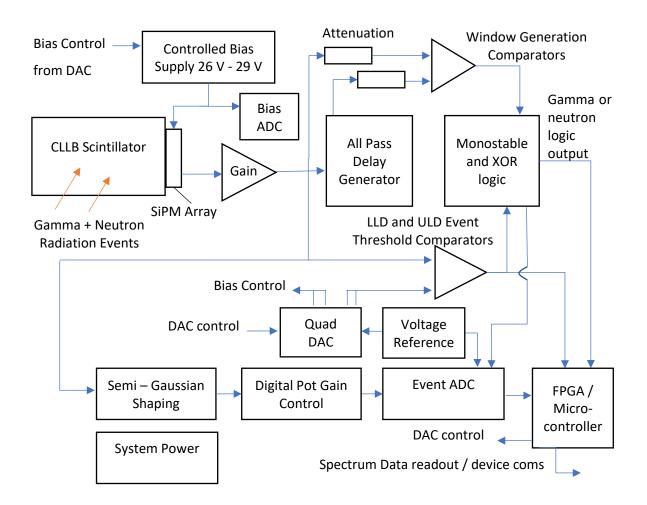

|   | 4.7       | Spec                                                                                              | troscopic System Design with Gamma Neutron Discrimination | 74 |  |  |  |  |

|   | 4.8       | Sect                                                                                              | ion Conclusion                                            | 76 |  |  |  |  |

| 5 | Con       | clusic                                                                                            | n                                                         | 77 |  |  |  |  |

|   | 5.1       | Achi                                                                                              | eving the Research Objectives                             | 78 |  |  |  |  |

|   | 5.2       | Futu                                                                                              | re Work                                                   | 78 |  |  |  |  |

| R | eferend   | ces                                                                                               |                                                           | 80 |  |  |  |  |

| A | opendi    | x                                                                                                 |                                                           | 83 |  |  |  |  |

|   | A. D      | ata C                                                                                             | onstruction Table for the Folding ADC System              | 83 |  |  |  |  |

|   |           |                                                                                                   |                                                           |    |  |  |  |  |

|   | C. S      | . Simulated Discrimination Circuit                                                                |                                                           |    |  |  |  |  |

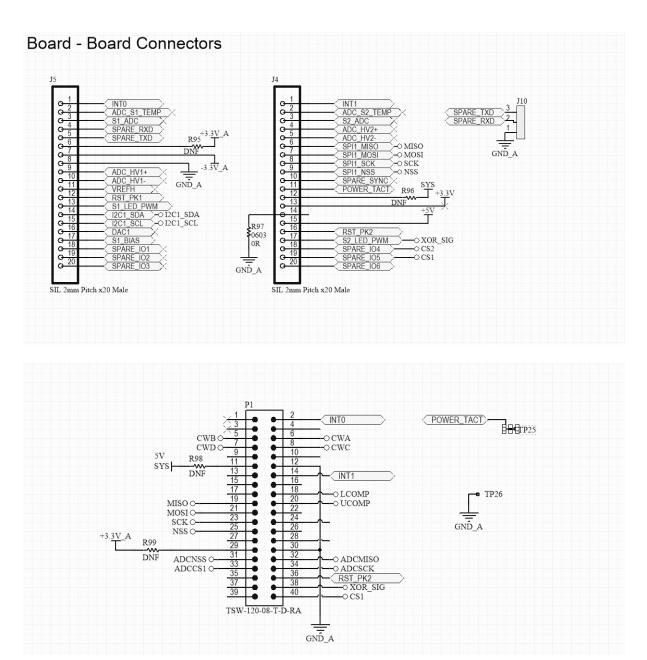

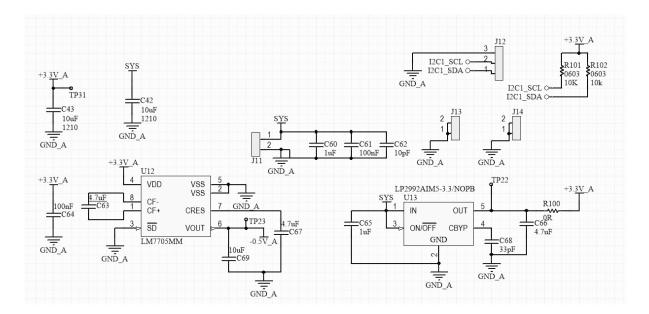

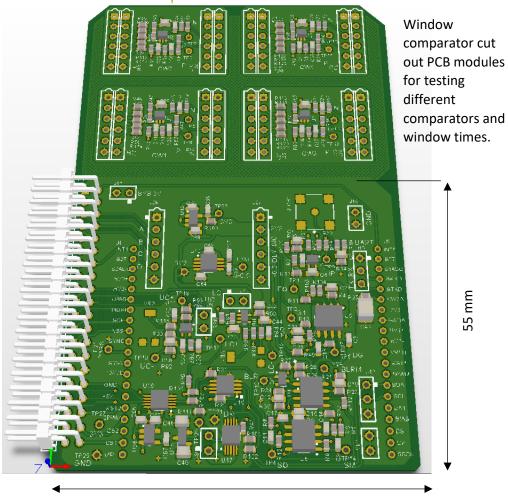

|   | D. P      | rotot                                                                                             | pe Discrimination Circuit Schematic and Manufactured PCB  | 94 |  |  |  |  |

|   |           |                                                                                                   |                                                           |    |  |  |  |  |

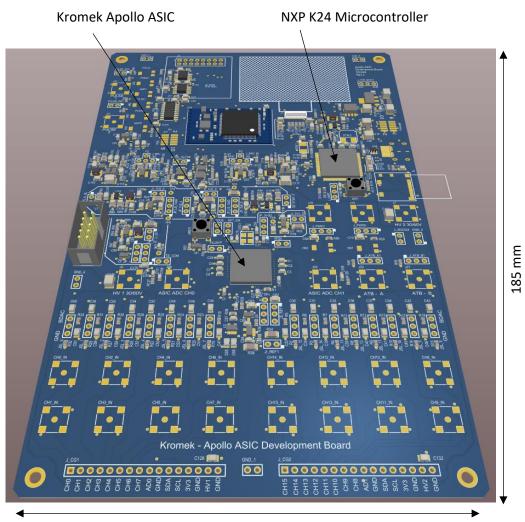

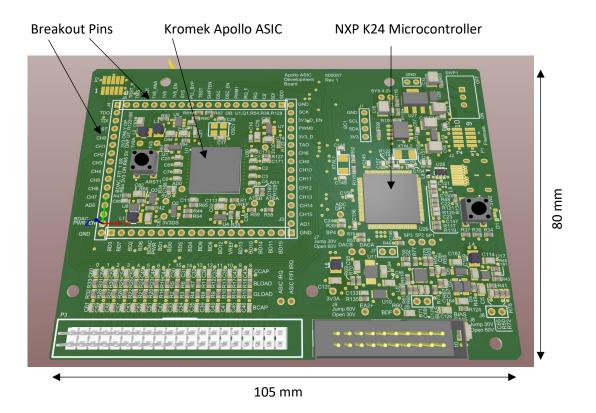

|   |           |                                                                                                   | k Apollo ASIC Development Board1                          |    |  |  |  |  |

# List of Figures

| Figure 1-1 A typical Cs137 spectrum showing energy peak of 0.662 MeV for the Cs137 radioactive isotope             |

|--------------------------------------------------------------------------------------------------------------------|

| Figure 1-2 Example of a lorry radiation screening portal (Shanghai Eastimage Equipment Co Ltd, 2016).              |

| Figure 1-3 The Kromek hand held D3S gamma and neutron detector (Kromek Ltd, 2016)14                                |

| Figure 1-4 Simulated heat map showing radiation levels monitored by a network of portable detectors                |

| in a city (DARPA, 2015)                                                                                            |

| Figure 2-1 Diagram to show a gamma ray interaction with a scintillator and the photon detection                    |

| method used                                                                                                        |

| Figure 2-2 Diagram showing electron movement upon ionization event in an activator doped                           |

| scintillator                                                                                                       |

| Figure 2-3 Emission wavelength of selected inorganic scintillators plotted with the response                       |

| sensitivities of two PMT examples. (Knoll G. F., Scintillation Detector Principles, 1999)                          |

| Figure 2-4 CsI(Tl) Crystal with bonded SiPMs on a PCB (Top), Metal encased Nal(Tl) Crystal with                    |

| attached PMT (Bottom)                                                                                              |

| Figure 2-5 Neutron detector, showing thin Lithium Zinc Sulphide layers and wave guide layers example.              |

| (Southern Scientific Ltd, 2012)                                                                                    |

| Figure 2-6 Normalised CLLB scintillation average output waveforms for gamma, thermal neutron and                   |

| alpha particles. (Mesick, Coupland, & Stonehill, 2016)                                                             |

| Figure 2-7 An energy spectrum acquired using CLLB exposed to gamma, thermal neutrons and alpha                     |

| radiation. (Mesick, Coupland, & Stonehill, 2016)23                                                                 |

| Figure 2-8 Smoothed gamma and neutron scintillation output showing window bars for the window                      |

| integration periods (Glodo, Hawrami, Loef, Shirwadkar, & Shah, 2012).                                              |

| Figure 2-9 APD operation overview showing (a) A single microcell configuration, (b) states of a                    |

| microcell upon photon interaction shown on a current vs voltage graph, (c) Output voltage pulses                   |

| using a load resistor (Jackson, O'Neill, Wall, & McGarvey, 2016).                                                  |

| Figure 2-10 SiPM construction example using 12 microcells (SensL Technologies Ltd, 2017)27                         |

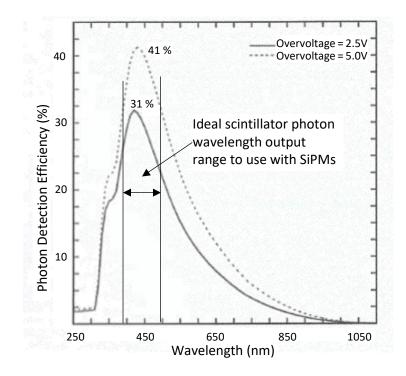

| Figure 2-11 Graph showing optimal wavelength for photon detection efficiency at over-voltages of 2.5               |

| V and 5.0 V (Jackson, O'Neill, Wall, & McGarvey, 2016)28                                                           |

| Figure 2-12 Diagram of a typical detector system, showing the typical electrical signal output at each             |

| stage                                                                                                              |

| Figure 2-13 - Diagram showing basic structure of an (RC) <sup>n</sup> second order shaping filter with gain stages |

| (Noulis, 2016)                                                                                                     |

| Figure 2-14 Operation of a threshold comparator used to detect events                                              |

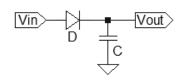

| Figure 2-15 Basic peak detector using passive components                                                           |

| Figure 2-16 Practical implantation of a peak detector circuit based on op-amps and diodes (Pallas-                 |

| Areny & Webster, 1999)                                                                                             |

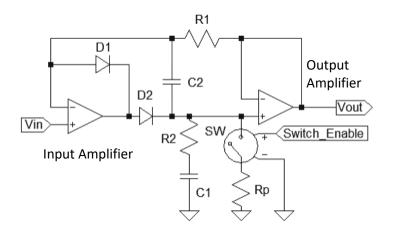

| Figure 2-17 Oscilloscope trace of the analogue signals in a gamma detector, showing the amplified           |

|-------------------------------------------------------------------------------------------------------------|

| SiPM output (blue), the shaping stage output (pink) and the peak capture and hold (green)                   |

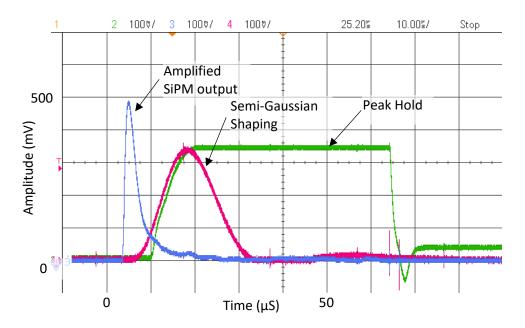

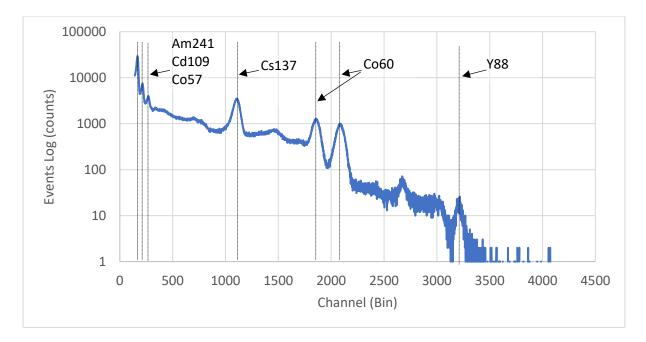

| Figure 2-18 Annotated 12 bit resolution spectrum showing identified isotope peak positions from a           |

| mixed radiation source                                                                                      |

| Figure 2-19 Annotated 7 bit resolution spectrum showing identified isotope peak positions from a            |

| mixed radiation source                                                                                      |

| Figure 3-1 Oscilloscope trace with overlaid trace showing the ideal peak hold reset point                   |

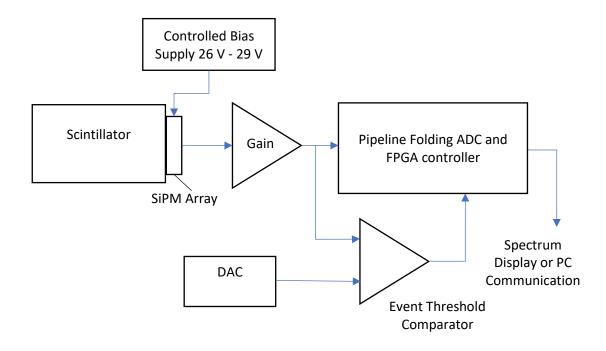

| Figure 3-2 Gamma Detector System using the Pipelined Folding ADC for pulse amplitude capture39              |

| Figure 3-3 Block level diagram of a 4bit Sample and Hold, Folding ADC, with ramp input and associated       |

| typical output signals (over multiple samples)40                                                            |

| Figure 3-4 FPGA Application diagram showing the required components in the design and written               |

| VHDL outline                                                                                                |

| Figure 3-5 Waveform diagram showing the Non Overlapping Clock generation and output                         |

| Figure 3-6 FPGA Input Synchronisation Logic for Metastability Protection (Altera Corporation, 2009).        |

|                                                                                                             |

| Figure 3-7 ADC sample and hold stages showing the ADC stage odd and even output categories 42               |

| Figure 3-8 ADC Data Control Logic Table showing the first 4 conversions ripple through the control          |

| logic of the ADC as in operation at the time of the 4 <sup>th</sup> sample + 1 PLL clock                    |

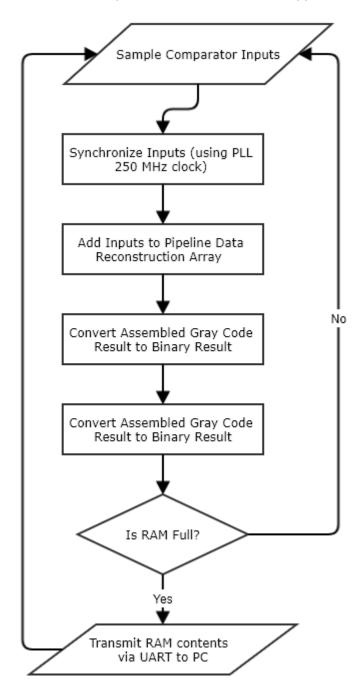

| Figure 3-9 Flow diagram showing the data processing system implemented in the FPGA for result               |

| reconstruction and transmission                                                                             |

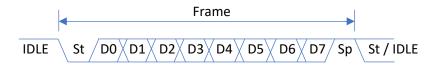

| Figure 3-10 Logic diagram showing a single UART frame at configured in the design                           |

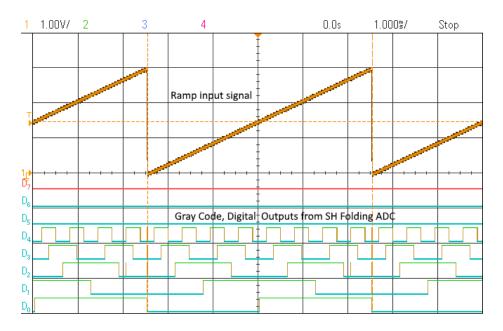

| Figure 3-11 Oscilloscope trace showing the verification of the Gray code outputs from the S&H Folding       |

| ADC                                                                                                         |

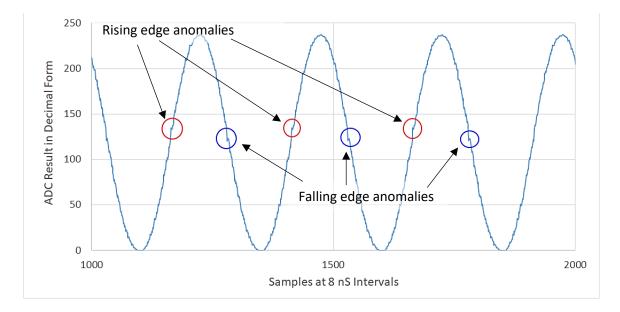

| Figure 3-12 Results obtained by using the ADC system with a 100 kHz sine wave input, re-plotted from        |

| the captured data, with circled anomalies46                                                                 |

| Figure 3-13 Annotated oscilloscope trace showing a generated shaped pulse with a 2.5 $\mu$ S shaping        |

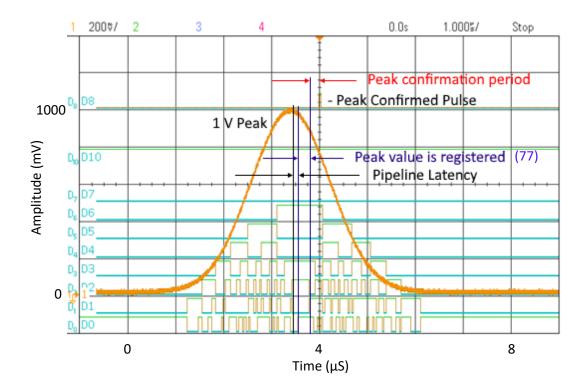

| time, and binary logic representation from the ADC system                                                   |

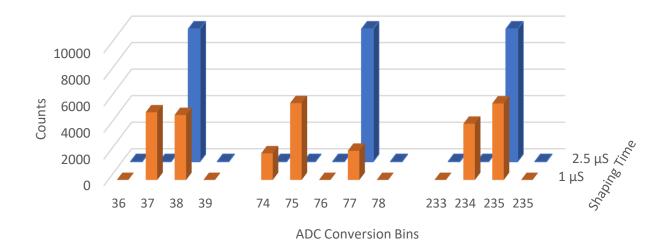

| Figure 3-14 Graph showing 10,000 acquired peak values using the generated 2.5 $\mu$ S and 1 $\mu$ S shaping |

| time inputs for 3 discrete amplitudes49                                                                     |

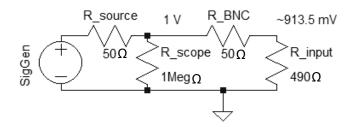

| Figure 3-15 Circuit representation of the measurement and test setup                                        |

| Figure 3-16 Folding ADC System applied to sample an amplified SiPM signal directly                          |

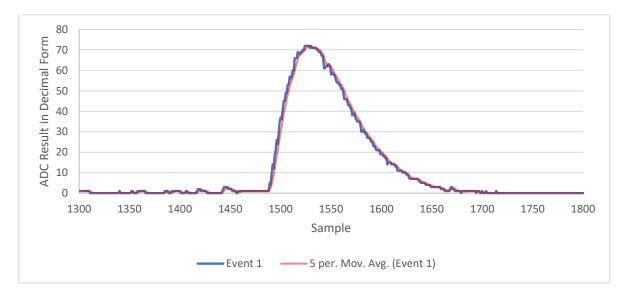

| Figure 3-17 Mid ADC input range captured gamma radiation event extracted from continuous                    |

| sampling an amplified SiPM output coupled to a CsI(Ti) crystal using the ADC system and applied             |

| moving average                                                                                              |

| Figure 3-18 Low-end ADC input range captured gamma radiation event extracted from continuous                |

| sampling an amplified SiPM output coupled to a CsI(Ti) crystal using the ADC system and applied             |

| moving average                                                                                              |

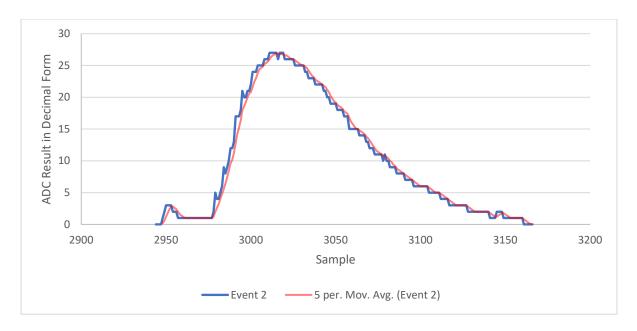

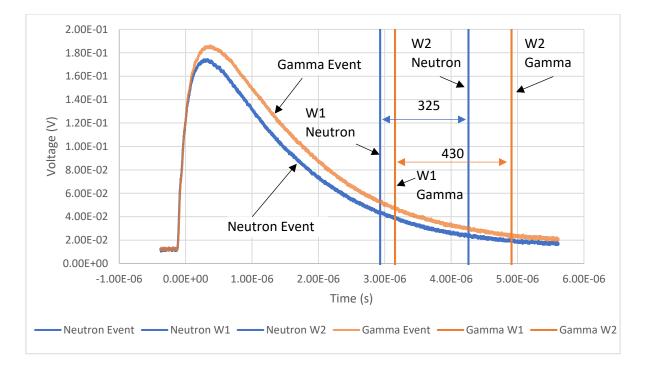

| Figure 4-1 Implemented method for pulse shape discrimination of normalised typical CLLB scintillation       |

| outputs for a gamma and neutron event                                                                       |

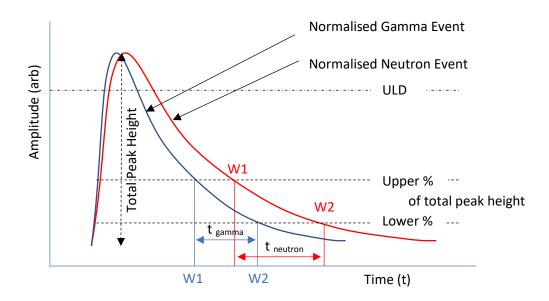

| Figure 4-2 Diagram of the peak finding method using a delayed repeat of the scintillation event signal |

|--------------------------------------------------------------------------------------------------------|

| using a comparator to compare both signals57                                                           |

| Figure 4-3 Diagram showing peak error correction by attenuation of the original event signal           |

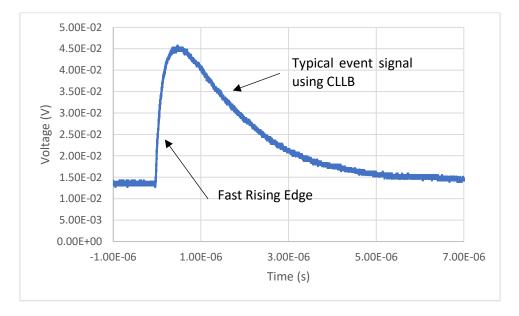

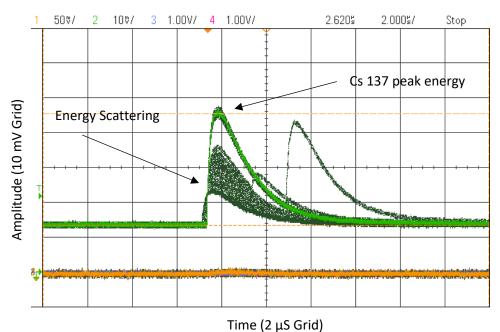

| Figure 4-4 Event signal output of a Cs137 scintillation event using CLLB and a 4x4 array of SensL J-   |

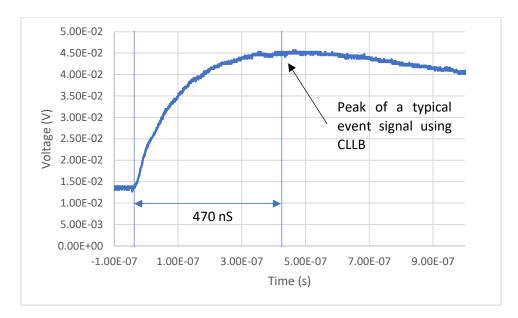

| Series SiPMs                                                                                           |

| Figure 4-5 Leading edge rise time measurement of 470 nS based on the event in Figure 4-460             |

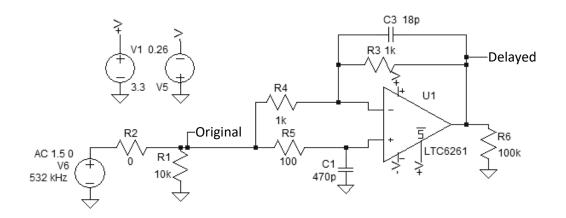

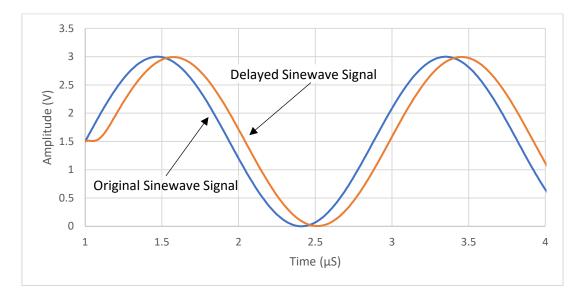

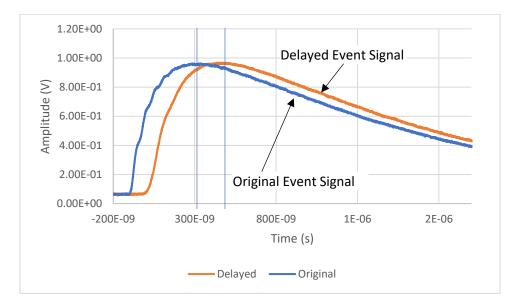

| Figure 4-6 Simulated All Pass circuit used to generate the signal time delay                           |

| Figure 4-7 Simulated results of using the circuit in Figure 4-6, showing a delayed output of the input |

| waveform of 99 nS61                                                                                    |

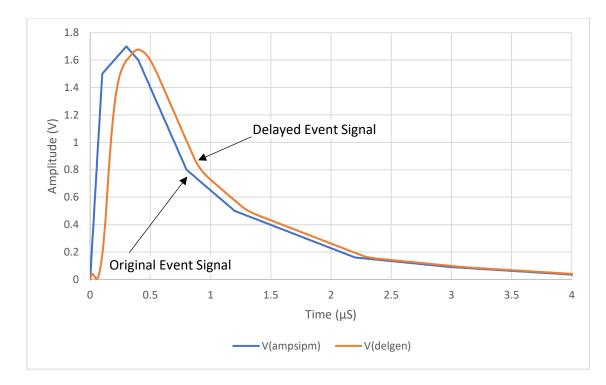

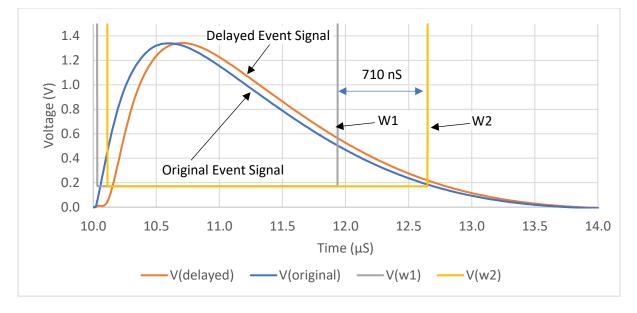

| Figure 4-8 Simulating the All Pass delay circuit with a typical scintillation event signal62           |

| Figure 4-9 Diagram showing the adjustment of the original and delayed event signals to adjust the      |

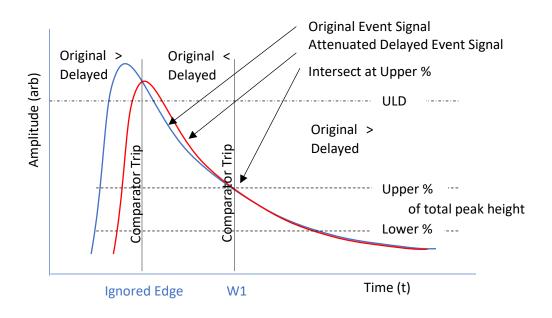

| intersect time point to generate W163                                                                  |

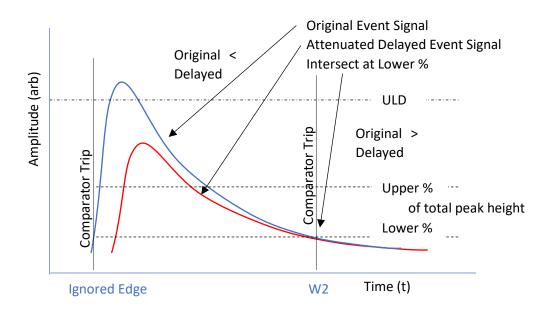

| Figure 4-10 Diagram showing the adjustment of the original and delayed event signals to adjust the     |

| intersect point to generate W264                                                                       |

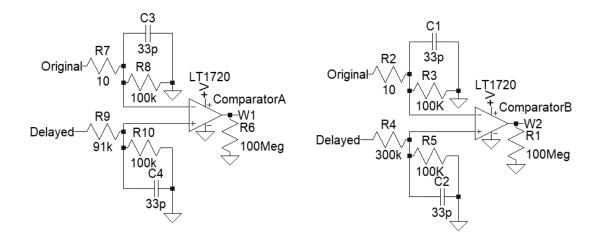

| Figure 4-11 Discrimination window generation using two comparators                                     |

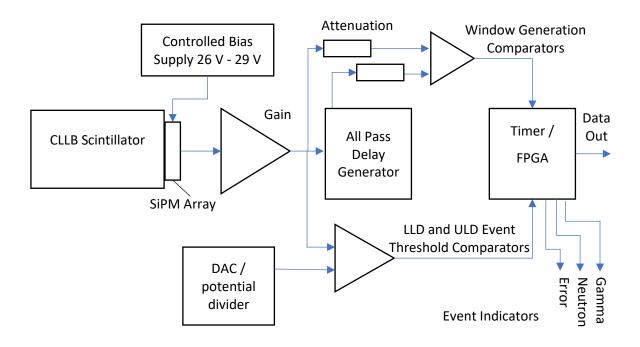

| Figure 4-12 Designed gamma neutron discrimination system                                               |

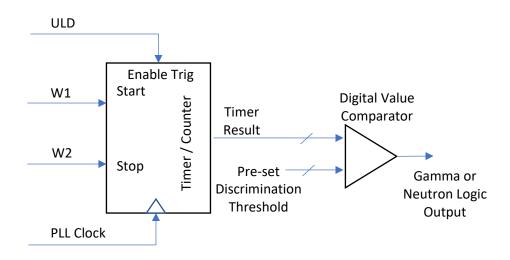

| Figure 4-13 Timer unit diagram implemented in the FPGA for window time measurement                     |

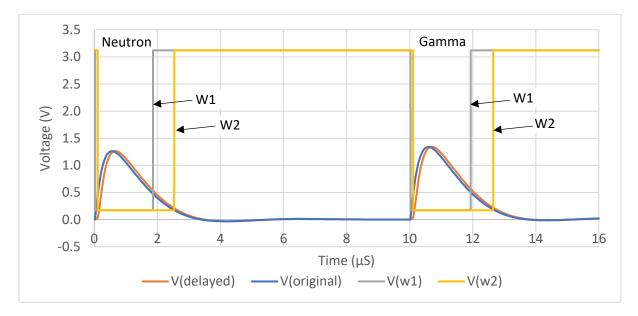

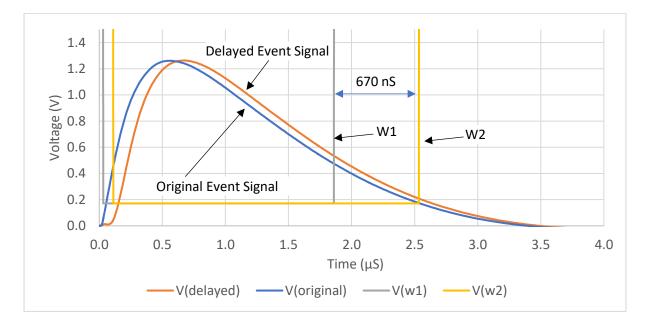

| Figure 4-14 Simulated discrimination circuit results, showing window for neutron (1st event) and a     |

| gamma (2nd event)66                                                                                    |

| Figure 4-15 Simulated neutron event window measurement67                                               |

| Figure 4-16 Simulated gamma event window measurement67                                                 |

| Figure 4-17 Measuring the generated signal delay in the prototype circuit, showing a delay of 173 nS.  |

|                                                                                                        |

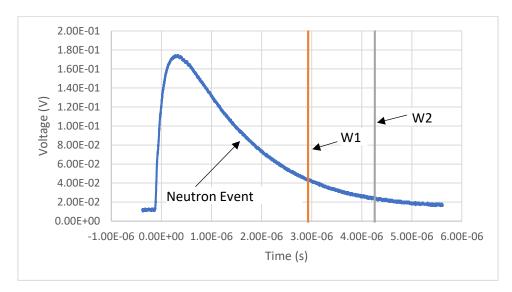

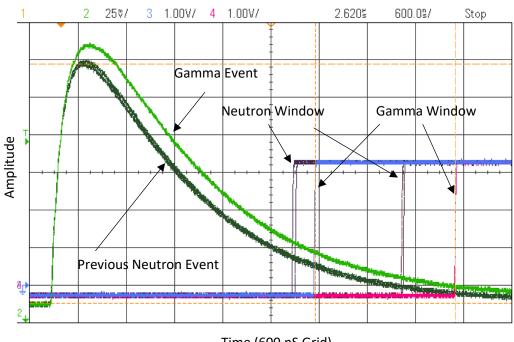

| Figure 4-18 Oscilloscope trace showing a neutron event with the discrimination window69                |

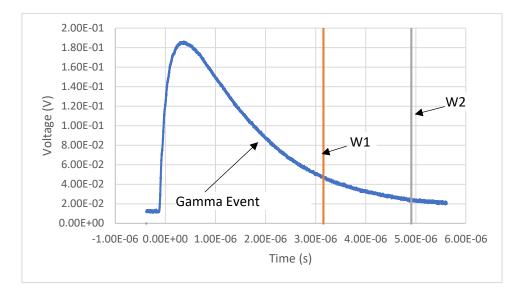

| Figure 4-19 Oscilloscope trace showing a gamma event with the discrimination window70                  |

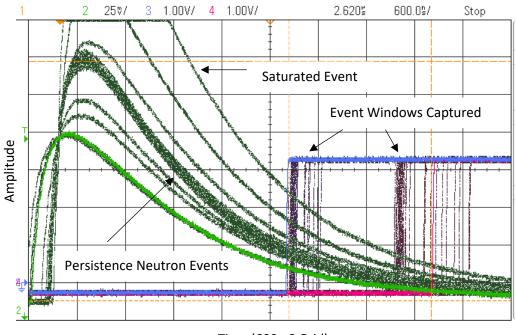

| Figure 4-20 Oscilloscope trace showing a neutron and gamma event with the discrimination windows.      |

|                                                                                                        |

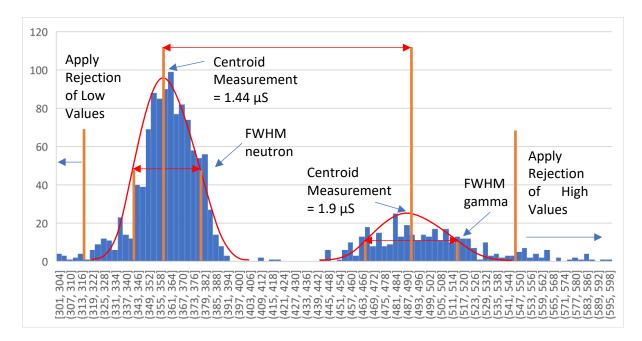

| Figure 4-21 Histogram of window times using the discrimination system with gamma and neutron           |

| radiation sources, with FOM measurement annotations using a 250 MHz counter clock71                    |

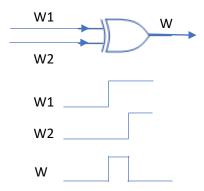

| Figure 4-22 XOR gate used to create a logic pulse with the length matching the difference between      |

| W1 and W2 rising edges73                                                                               |

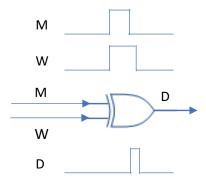

| Figure 4-23 Using a monostable and XOR logic as the decision threshold in the discrimination system.   |

| Figure 4-24 Proposed spectroscopic gamma and neutron radiation detection system for portable, low      |

| power devices                                                                                          |

|                                                                                                        |

# List of Tables

| Table 3-1 UART configuration used in the application.         4                              | 15 |

|----------------------------------------------------------------------------------------------|----|

| Table 4-1 Power consumption properties of the proposed prototype discrimination system       | 72 |

| Table 4-2 Complete gamma spectroscopic and neutron detection system components proposed usir | ng |

| the improvements suggested to the discrimination system7                                     | 76 |

# List of Equations

| Equation 2-1 Figure of Merit Equation used to evaluate the effectiveness of a discrimination system. |

|------------------------------------------------------------------------------------------------------|

| 25                                                                                                   |

| Equation 2-2 - Shaping time equation (Noulis, 2016)                                                  |

| Equation 2-3 - Calculated Resolution capability of the gamma detector circuitry in the D3S using     |

| reported 12 bit resolution                                                                           |

| Equation 4-1 Finding the time delay generated from an all pass filter based on known signal          |

| frequencies (Pallas-Areny & Webster, 1999)58                                                         |

| Equation 4-2 Finding $f_0$ in Equation 4-1 where $f_0$ is equal to 3.39 MHz                          |

| Equation 4-3 Calculating a sine wave fit approximation using the measurement in Figure 4-560         |

| Equation 4-4 Calculating the relative amplitude intersect time point for W1                          |

| Equation 4-5 Calculating the relative amplitude intersect time point for W2                          |

| Equation 4-6 Calculating the expected amplitude of neutron scintillation events using a Cs137 event  |

| amplitude reference                                                                                  |

| Equation 4-7 Calculations showing the conversion of the counter result to a discrimination window    |

| time for a neutron event (top) and gamma event (bottom)71                                            |

| Equation 4-8 Worked figure of merit calculation based on the discrimination histogram results in     |

| Figure 4-2172                                                                                        |

# 1 Introduction

In the environment around us, radiation is emitted from many radioactive sources both natural and manmade. Natural sources such as granite rock, natural radon in the ground, and cosmic radiation largely make up the background radiation levels, varying by geometric location. Manmade sources, consisting of laboratory synthesised radioactive material, and processed material from natural sources also contribute to background levels, largely from use in medical practices.

Radiation sources have uses in everyday life, not only for medical treatments, but for example are also used in industrial instruments for material thickness measurements, tinned food processing and household smoke alarm detectors. Radioactive waste products are also produced in the nuclear power industry, and although usually sealed and safely disposed of, accidental leakage or escape of radioactive materials have contributed to hazardous radiation levels in some places such as Chernobyl and Fukushima.

The manufacture and use of manmade sources and the uses of them are strictly controlled due to the health hazards of excessive radiation exposure to individuals and to the public. Radiation detection devices are essential for discovering and monitoring the potential impacts of radiation exposure, whether it's from an unsafe natural increase in radiation levels, the effects of a nuclear accident or illicit movement and use of a radiation source or radioactive material.

#### 1.1 Radiation Monitoring and Radioactive Source Control

The use and manufacture of radioactive material is increasing as demand of it for its uses increases in society, therefore the control of the increasing amount of radioactive source material is seen as an ever increasing challenge for security services. Some radioactive sources are more controlled than others, typically due to the health hazard the material presents from its type, strength and energy of emitted radiation.

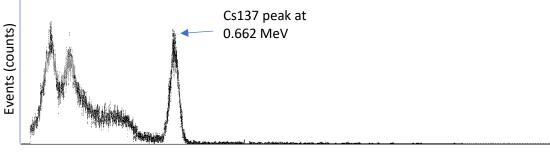

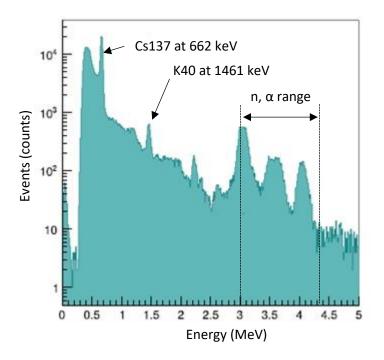

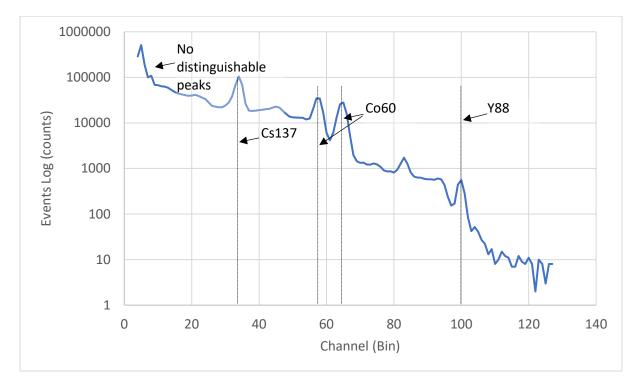

The main radiation types are alpha, beta, gamma and neutron, where gamma and neutron radiation are also categorised as uncharged radiation. Uncharged radiation can travel large distances compared to alpha and beta radiation due to its higher penetration energy, therefore its detection can also be achieved from a distance. Gamma radioactive sources will emit gamma radiation with specific gamma energies depending on the decay of the radioactive isotopes in the material. When using gamma spectroscopy, these energies can be identified in the yielded gamma spectrum and matched to the known gamma emissions of radioactive isotopes, where the isotope can then be identified. Figure 1-1 shows a typical collected spectrum showing energies consistent with the identification of the isotope caesium 137 (Cs137).

Energy (MeV)

#### Figure 1-1 A typical Cs137 spectrum showing energy peak of 0.662 MeV for the Cs137 radioactive isotope.

Source control is therefore made more complex by not only having to monitor for unsafe radiation levels but also to identify the radiation sources detected to evaluate the safety of the immediate environment. An example of this would be a medical patient that has undergone recent treatment with the use of a medical radioactive material, would then be emitting radiation with the energies of the associated isotope used in the medical treatment. As a public safety concern, medical sources and the radiation exposure is strictly controlled so a prolonged exposure would not increase any risk to health. The detection of radioactive waste in a city centre however would cause a safety concern if detected with any exposure level, and the necessary security actions can then be taken.

The development of technology in radiation detection devices, and the increased requirement for detection devices is pushing development of mass market, particularly pocket sized, hand held portable radiation detection and monitoring devices in the security industry.

#### 1.2 Radiation Safety and Monitoring Systems

Currently, a large amount of radiation detection for security is used at transportation hubs, particularly for goods scanning to detect any radioactive contaminates, or undocumented transportation of radioactive material that could be used for illicit purposes if its intended destination is reached. Often called portal screening, large installations built to scan shipping containers or lorries in bulk whilst moving through, where an example is shown in Figure 1-2.

Figure 1-2 Example of a lorry radiation screening portal (Shanghai Eastimage Equipment Co Ltd, 2016).

Whilst these solutions are suitable for large scale detection, the technology is impractical for densely populated city centres for example and is far from a portable solution.

Traditional portable detection devices are often heavy and do not meet in the industry demands of the pocket sized, hand held device. This is largely due to the radiation detection method employed in the device, where the use of Geiger Muller tubes or the use of photo multiplier tubes (PMTs) with scintillator material restricted how small such a device could be. Another issue is that the traditional detectors used require the generation of high voltage, particularly for PMTs where the operation voltage required can be over 1000 V, thus the power demands often dictated larger batteries.

Scintillation is the process of photon emission upon radiation interaction in specified scintillator material where it can then be used to detect a chosen type of radiation. Portable devices already typically use a Caesium lodide crystal as a gamma scintillator, and Boron can be used as a neutron scintillator, both then implemented as two discrete gamma and neutron detector modules. Radiation devices that use the method of scintillation have benefited from recent advances in silicon photomultiplier (SiPM) technology which achieves single photon detection from a component as small as 1x1 mm and only requiring a relatively low operation bias voltage of between 30 V and 60 V. The SiPM technology removes both the requirement of the use of large PMT detectors and the associated power consuming electronics. This then has allowed the use of smaller batteries, in turn leading to smaller, more power efficient portable radiation detector devices where the latest portable detectors can achieve operating power consumptions as low as 300 mW, such as the Kromek D3S, shown in Figure 1-3.

Figure 1-3 The Kromek hand held D3S gamma and neutron detector (Kromek Ltd, 2016).

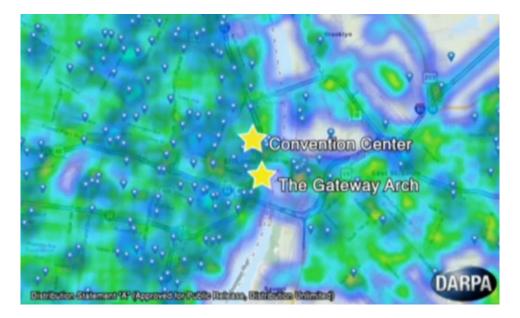

The Defence Advanced Research Projects Agency (DARPA) aims to use a wide network of portable radiation detection devices carried by already mobile people such as police officers and fire crews to monitor radiation, particularly in the city centres. By processing the accumulated spectra data from all the detector devices through internet based cloud computing methods, DARPA aims to use a live heat map as shown in Figure 1-4, to visually identify the radiation level, where the system can send the necessary alerts depending on the automated detection and identification of a potentially illicit radioactive material (DARPA, 2015).

Figure 1-4 Simulated heat map showing radiation levels monitored by a network of portable detectors in a city (DARPA, 2015).

#### 1.3 Research Aims and Objectives

The requirements from industry applications is for the next generation of uncharged radiation detection devices to be smaller in size and have a longer operational time between battery replacement or charge. By exploiting the latest advances in SiPM technology and new state of the art scintillation material, which scintillates upon gamma and neutron interaction, detector sizes can

potentially be reduced by a factor of two, as currently separate gamma and neutron modules can be combined. To be able to exploit this however, the electronic circuitry must not only be able to accurately process the gamma spectroscopy information, but accurately distinguish between a gamma and neutron event whilst achieving a high operational power efficiency. The developed circuitry must also be scalable to match the specified scintillator capability, where some applications require the processing of up to 100,000 detected radiation events per second for extreme emergency situations.

The research objectives were as follows:

- Evaluate the existing technology available for radiation detection using scintillators and SiPM technology for gamma and neutron detection.

- Determine key technology requirements for the use of scintillators and SiPMs, as well as gamma spectroscopy and gamma neutron discrimination.

- Design and implement detection circuitry and relevant processing techniques that can then allow the implementation of low power, compact size gamma spectroscopy applications and provide gamma neutron discrimination.

- Deliver and evaluate prototype systems using the developed circuitry that can provide accurate detection of radiation events through the use of scintillators and the use of test radiation sources.

#### 1.4 Research Structure and Methodology

The following method was used to achieve the objectives set out in section 1.3, where each point then has a summary of the work undertaken and the key research contributions made to the research aims.

Complete a literature review, covering the principals of radiation detection via the scintillation method. Further include an investigation of existing pulse shape discrimination methods based on the current state of the art scintillation technology. Add to the literature review an investigation on the latest SiPM technology, and commonly used electronic processing circuitry for radiation event detection devices.

Chapter two in this research establishes the foundation technology that is commonly used for radiation detection, including for use in modern portable devices. The chapter evaluates how the radiation events are detected and the importance of capturing the event signal characteristics, of which the subsequent circuit design proposed by this research uses as the basis for the novel enhancements that allow low power gamma neutron discrimination and gamma spectroscopy.

Introduction

Propose, design and test a flexible and power efficient electronics processing circuitry solution for use with a scintillator given the 100,000 event rate requirement, including the ability to be able to use the latest combined gamma neutron scintillators.

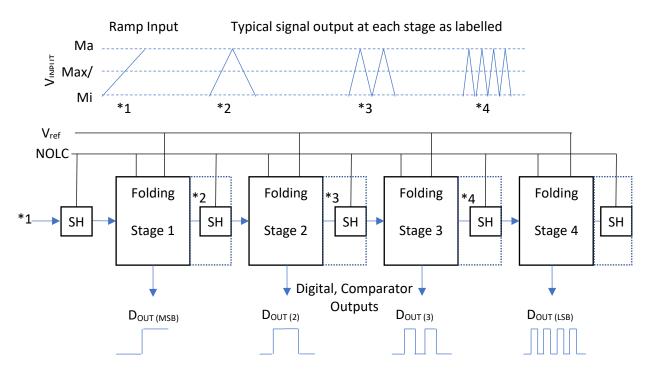

Chapter three in this research explains how using a state of the art analogue to digital converter (ADC) and the developed novel digital processing through the use of a Field Programmable Gate Array (FPGA) can eliminate the use of some of the traditional radiation event signal processing circuitry. The implementation of the designed system, including the constructed VHDL processing methods shows that the radiation event signal can be accurately reconstructed digitally such as to acquire the characteristics required for gamma spectroscopy and gamma neutron discrimination, with an efficient power consumption vs circuit performance advantage over traditional systems.

• Further propose, design and test an optimised solution for dual gamma neutron scintillators, where the emphasis is on size reduction and power efficiency.

Chapter four in this research details a novel method of gamma neutron discrimination whilst achieving low power operation, drawing particular reference to the innovative window generation circuit. This is developed and implemented in circuitry for the system gamma neutron discrimination performance to be evaluated, yielding a system figure of merit (FOM) of 1.68 whilst consuming less than 15 mW of power using the first prototype. Through further system optimisations and further adding low power optimised traditional circuitry for gamma spectroscopy, the final circuit design achieves the objectives with the FOM of 1.68 whilst consuming as lower power as 14 mW.

• Conclude information on the design methods and the tested solution's performance for use in portable radiation detection devices, also providing a future technology outlook.

The conclusion in chapter five highlights the key detection technology enhancements of the research and concludes on the designed systems effectiveness for their use in portable radiation detectors. A future outlook on radiation detector technology is also summarised.

## 2 Literature Review

For the purposes of radiation detection in portable devices, it is important to understand the frontend detection process, to determine the existing analogue signal processing methods are employed, and how the scintillation event characteristics translate to gamma energy information for gamma isotope identification, and neutron detection. This will provide a written overview of radiation detection from first principals.

#### 2.1 Scintillation overview

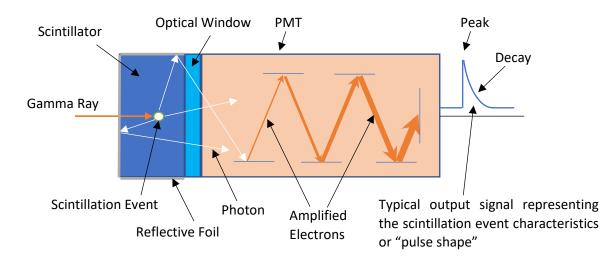

Using scintillation as a method of detecting ionizing radiation is a well-established process used in many applications, where different scintillating material is selected depending on the type of radiation that is to be detected, and the photon to electrical signal conversion method that is intended for use in the application. (Knoll G. F., Scintillation Detector Principles, 1999). A simplified diagram of the process is shown in Figure 2-1.

Figure 2-1 Diagram to show a gamma ray interaction with a scintillator and the photon detection method used.

The selection of the scintillation material is normally based on the efficiency of it converting the kinetic energy of the radiation particle in to photons, linearly over the energy range of interest; typically measured in keV or MeV. The material must also have suitable luminescence and optical properties, where the wavelength and the pulse shape of the emitted photons matches the detection capabilities of the sensor in the application, typically a photo multiplier tube (PMT) or photodiode based component. (Knoll G. F., Scintillation Detector Principles, 1999). The use of the photon sensor allows the allows conversion of the emitted photons from the scintillation event to be converted into an electrical current output, which can then be processed by the detector electronics.

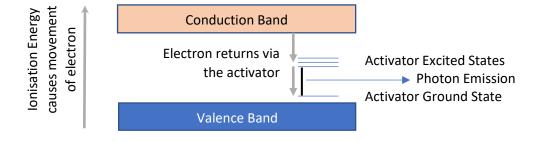

Focusing on gamma radiation detection; in the year 1948 Robert Hofstadter showed that an inorganic scintillator composed of sodium iodide, with a trace of thallium iodide used as an activator yielded a significant quantity of emitted photons upon radiation interaction. The process of scintillation with most inorganic materials is the same, ionising radiation interacts with the scintillator crystal material and excites electrons, causing them to rise from the valance band in the material atomic structure, to the conduction band. As this leaves behind an electron hole, the return of the electron causes the emission of a photon. Since the gap width between the valance band and the conduction band in a pure crystal material such as sodium iodide on its own is too great, the resulting photon emission has a high energy that is not easily detected. (Knoll G. F., 1999).

The use the activator, thallium iodide in this case allows for an increased probability of photon emission with a lower energy and hence a wavelength that is easier to detect. This process can be seen in Figure 2-2. Efficiencies and decay characteristics of these electron interactions, and therefore the photon yield and photon emission pulse shapes upon scintillation are different for each material. Gamma radiation passing through the crystal will excite many electrons proportional to the kinetic energy of the radiation absorbed, and since different radioactive isotopes emit gamma energies that can identify the isotope, this process forms the basis of gamma spectroscopy applications (Pursley, J & Michigan State University, 2001).

Figure 2-2 Diagram showing electron movement upon ionization event in an activator doped scintillator.

As well as a large photon yield, sodium iodide with thallium activator, NaI(TI), exhibits low nonlinearity for photon output versus the gamma radiation absorbed, at 38000 photons per MeV. The wavelength of the emitted photons upon scintillation for NaI(Ti) is 415 nm, and is compatible with common detector sensitivities and also, has a decay time characteristic of 230 nS. Additionally, NaI(Ti) is relatively easy to produce, compared to that of organic scintillator alternatives, and can be scaled to different shapes and sizes. Considerations must be made when using NaI(TI) however, as the crystal is hydroscopic, where atmosphere moisture can destroy the crystal and hence must be sealed in a protective encapsulation with a window often referred to as being canned. NaI(TI) crystals also considered to be brittle and therefore must be handled with care, making it unsuitable for some harsh Literature Review

applications where exposure to forceful impacts could damage the crystal. (Knoll G. F., Scintillation Detector Principles, 1999).

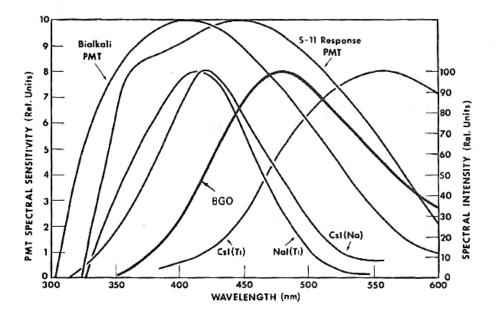

Although Nal(TI), is still commonly used in applications, Caesium Iodide with thallium activator, CsI(TI), is also commonly used in application where crystal robustness is needed as it is less brittle than Nal(TI), and where performance to volume is important. CsI(TI) yields 65000 photons per MeV, higher than that of Nal(TI), however the wavelength of the photon emissions is at nominally 550 nm and is therefore further away from the peak sensitivity of some detector devices such as PMTs, compared to that of NAI(TI). The photon emission wavelength of a selection of inorganic scintillators showing spectral sensitivity and wavelength can be seen in Figure 2-3. The total time of the pulse generated upon a scintillon event in CsI(TI) is also longer than NaI(TI) with two time components to its scintillation decay process at 680 nS and 3340 nS, making the scintillation event time longer and CsI(TI) less suitable to higher radiation count rate applications (Saint-Gobain Crystals, 2017). The entirety of the pulse generated form the scintillation event represents the total energy deposited into the scintillator crystal from the gamma radiation, and therefore the detector system must be capable of capturing the pulse output height and shape accurately to accurately process the energy deposited from the radiation in the scintillation event (Knoll G. F., 1999).

*Figure 2-3 Emission wavelength of selected inorganic scintillators plotted with the response sensitivities of two PMT examples. (Knoll G. F., Scintillation Detector Principles, 1999).*

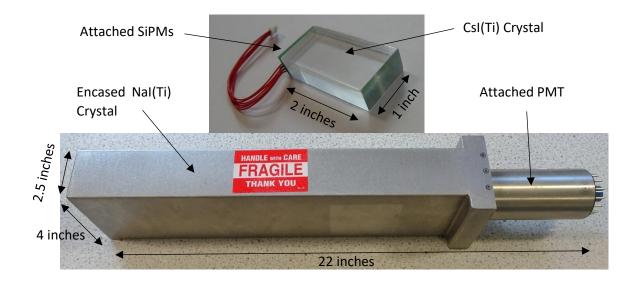

Figure 2-4 CsI(TI) Crystal with bonded SiPMs on a PCB (Top), Metal encased NaI(TI) Crystal with attached PMT (Bottom).

## 2.2 Scintillation for Neutron Detection

Research into neutron detection has increased since a recent global shortage of Helium 3, which was traditionally used for neutron detection. Helium 3 is a by-product of the radioactive decay of tritium of which the United States, a previous supplier of this has ceased production of, as tritium is only made as part of specific nuclear weapons manufacturing methods that are no longer used. (United States Government Accountability Office, 2011).

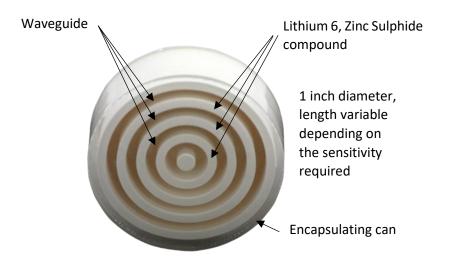

An alternative method for neutron detection with Helium 3, currently deployed in some portable detectors is to use a lithium-6 fluoride and zinc sulphide phosphor compound, where as part of the thermal neutron interaction with the lithium-6 fluoride an alpha particle is produced. This alpha particle then reacts with the zinc sulphide phosphor compound to emit photons with a wavelength in the region of 450 nm. Zinc sulphide alone can also be used for alpha particle detection (Saint-Gobain Crystals and Detectors, 2002). The photons produced can then be detected using a PMT for example. As these compounds tend to be absorbing to the wavelength of the emitted photons, they are often applied in thin layers to maximise surface area available for interaction with minimal material photon absorption, and a waveguide is then used to channel the photons to the detector. (Southern Scientific Ltd, 2012).

*Figure 2-5 Neutron detector, showing thin Lithium Zinc Sulphide layers and wave guide layers example. (Southern Scientific Ltd, 2012).*

Neutrons are primarily categorised in to thermal (or slow) neutrons, or fast neutrons depending on the neutron kinetic energy. Thermal neutrons typically possess energies of fractions of, or a few eV, where fast neutrons can possess energies in to the MeV range. Since the energy spectrum of thermal neutrons is so narrow, many detectors count thermal neutrons using the basis of the method described above, rather than capture the associated energy. Fast neutron detection can be achieved by typically employing hydrogenous or carbon based neutron moderators to reduce the kinetic energy to that of a thermal neutron (Saint-Gobain, 2017).

Spectroscopic fast neutron detection can be achieved by employing extra physical processes including elastic or inelastic scattering (Saint-Gobain, 2017). Applications for neutron spectroscopy include spent nuclear reactor fuel identification (Akyurek & Usman, 2015). Spectroscopic alpha particle detection can also be used to identify the source material, however can be challenging as alpha particles are easily absorbed in air and do not penetrate very far through matter. (arpansa, 2017). The detection of a high rate of neutrons would be classed as a hazard for security applications, hence most portable products use a moderator, typically water based, or some plastic based materials to decrease the energy of fast neutrons in to thermal neutrons, and only count the number of neutron interactions, rather than employ more complex spectroscopic processing for neutrons (Knoll G. F., 1999).

#### 2.3 Dual Gamma Neutron Detection Capable Materials

Using the similar scintillation principles as with gamma detection and neutron detection, crystals are emerging onto the market that can scintillate upon both gamma and neutron radiation interaction. Such a material would allow the use of a single detector system yielding both power and size benefits for portable detector products. (Saint-Gobain Crystals, 2017). One particular crystal material of interest is Cs2LiLaBr6 (CLLB) due to its high scintillation photon output of up to 60000 photons per MeV of radiation energy absorbed, good energy resolution figure relative to other scintillator materials, and photon emission wavelengths that are still compatible with common detection systems. (Mesick, Coupland, & Stonehill, 2016) (Shirwadkar, et al., 2010).

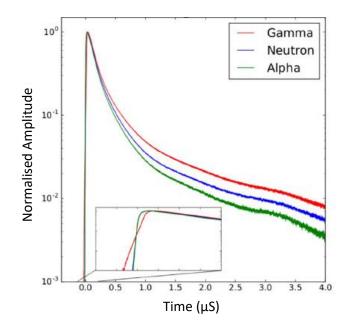

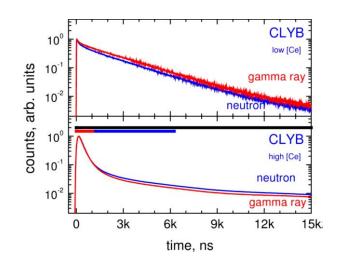

The properties of CLLB that are useful in dual gamma neutron detection is that the scintillation characteristics are different for gamma and neutron events, as well as alpha particle interactions. (Mesick, Coupland, & Stonehill, 2016). The differences can be seen in Figure 2-6.

Figure 2-6 Normalised CLLB scintillation average output waveforms for gamma, thermal neutron and alpha particles. (Mesick, Coupland, & Stonehill, 2016).

Another property of CLLB is the photons emitted upon neutron scintillation yield an electron equivalent energy of between 3.03 MeV and 3.2 MeV. Given that the energy ranges of interest in this project is for the identification of sources, with isotope emissions ranging between 60 keV and 3 MeV, there is another possible method of discrimination between gamma and neutron events. This can be seen when comparing gamma and neutron energy information spectroscopically, where Figure 2-7 shows gamma isotopes and neutron energy appearing in a sample spectrum. Both this energy range and the decay time of the photon output pulse are the key discrimination properties that factor in implementing gamma neutron discrimination methods. (Mesick, Coupland, & Stonehill, 2016).

Figure 2-7 An energy spectrum acquired using CLLB exposed to gamma, thermal neutrons and alpha radiation. (Mesick, Coupland, & Stonehill, 2016).

#### 2.4 Discrimination methods

There are multiple methods of discriminating gamma events from neutron events when using dual scintillators such as CLLB. Two main methods of gamma neutron discrimination that are commonly applied are pulse height discrimination (PHD) and pulse shape discrimination (PSD), where PSD methods often yield more distinguishable gamma neutron separation (Glodo, Hawrami, Loef, Shirwadkar, & Shah, 2012). These are applied to the electrical pulse output from the detection of the photons from the scintillation event through a device such as a PMT or photodiode component such as a SiPM.

#### 2.4.1 Pulse Height Discrimination

The method of PHD applied to CLLB is achieved based on identifying the neutron scintillation events where the emitted photons yield an electron equivalent energy of 3.03 MeV to 3.2 MeV, therefore by setting a threshold for any event that occurs over 3 MeV for example, will be deemed as a neutron event assuming no alpha particle detection. This method is however limited in accuracy as photon coupling to the detector is not perfect, and some gamma events can also register above 3 MeV such as cosmic gamma rays. (Mesick, Coupland, & Stonehill, 2016) (Glodo, Hawrami, Loef, Shirwadkar, & Shah, 2012).

#### 2.4.2 Pulse Shape Discrimination

Pulse shape discrimination relies primarily on identifying the difference in the decay characteristic between a gamma and neutron interaction, as shown previously in Figure 2-6. Integral windows are set at two time places where the decay difference is greatest between a gamma and neutron event. The signal present in these windows is then integrated and compared to each other and in some cases, the total length of the pulse. Figure 2-8 shows an example of this for another dual gamma neutron scintillator Cs2LiYBr6:Ce (CLYB). The integration result, which is the discrimination parameter in this method is accumulated over the total number of events in a histogram, used to show the separation of gamma and neutron events. (Glodo, Hawrami, Loef, Shirwadkar, & Shah, 2012).

Figure 2-8 Smoothed gamma and neutron scintillation output showing window bars for the window integration periods (Glodo, Hawrami, Loef, Shirwadkar, & Shah, 2012).

Both pulse height and pulse shape discrimination currently rely on digital conversion and processing of continuously sampled input pulses and so typically have to rely on high power components such as fast Analogue to Digital converters or laboratory oscilloscopes capturing the pulse waveforms, for offline pulse shape discrimination processing. Hand held detector products therefore do not yet implement these methods. (Cester, et al., 2014).

#### 2.4.3 Pulse Gradient Detection

A less commonly used method is pulse gradient measurement, where the peak of the scintillation signal is detected, and its amplitude is then measured. The time measured between this and the event signal decay crossing lower threshold voltage, where typically the event detection threshold voltage is used. As both axis parameters are then known, a gradient can be found and is used as the discrimination parameter in this method. In the same way as pulse shape discrimination, these gradient figures accumulated over multiple events are plotted on a histogram, and an FOM calculated

(Saldana & Stemen, 2014). The method is less commonly applied in CLLB applications as the peak to tail differences are minimal, so the discrimination result is poor.

#### 2.4.4 Evaluating Discrimination Methods and Systems

The main calculation used to evaluate the effectiveness of a discrimination system is its figure of merit (FOM), where the greater the figure of merit result, the greater the effectiveness of the system of correctly identifying the occurrence of a gamma or neutron scintillation interaction (Knoll G. F., Radiation Detection and Measurement, 2010). A figure of merit that is greater than 1.5 is generally considered as good in application. Scatter plots as suggested for use with pulse shape discrimination can be used to realise the FOM by gaussian fitting the accumulated gamma and neutron discrimination parameters and applying the FOM calculation. The equation for calculating the FOM when using this method is shown in Equation 2-1.

$$FOM = \frac{Centriod_{gamma} - Centriod_{neutron}}{FWHM_{gamma} + FWHM_{neutron}}$$

#### Equation 2-1 Figure of Merit Equation used to evaluate the effectiveness of a discrimination system.

A figure of merit of 1 would indicate that a decision threshold between determining whether an event was caused by a gamma or neutron would be hard to implement, as the gamma event and neutron event result regions would be next to each other in a histogram. Less than 1 would indicate discrimination was only partially, or not achieved as the regions overlap.

#### 2.5 Radiation Detection Utilising Silicon Photo Multipliers

Detecting the photons from scintillation caused by ionizing radiation interactions is currently achieved by the well-established use of photon detection components such as PMTs, positive – intrinsic – negative (PIN) photodiodes and standalone avalanche photodiodes (APD). Each of these detection components have advantages, such as single photon sensitive PMT performance, and the low relative operating voltage, cost and size of PIN diodes and APDs. Silicon photo multipliers (SiPM) have been developed with the aim of achieving these characteristics, where the performance of a PMT is achieved using the same size component as many PIN diodes and APDs, ideal for portable devices. (Jackson, O'Neill, Wall, & McGarvey, 2016).

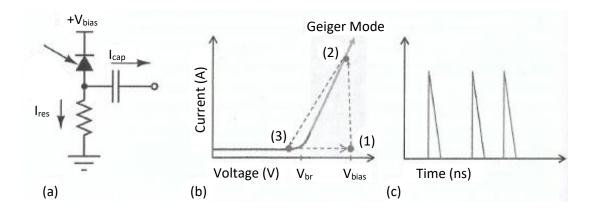

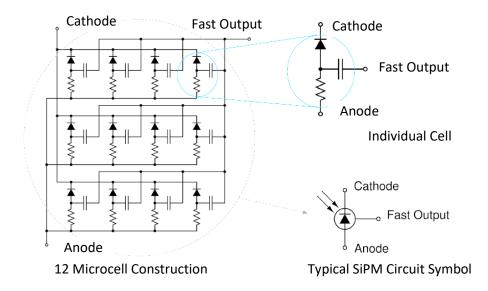

SiPMs are constructed using avalanche photodiodes (APD) that have been specifically fabricated so when biased into Geiger mode become single photon sensitive and referred to as a single photon avalanche diode (SPAD). As well as a SPAD, a quench resistor is connected to the SPAD anode as shown in Figure 2-9(a) to limit the current flow upon photon interaction, and with SensL manufactured SiPMs a fast output capacitor is also connected to the anode to form a microcell. (SensL Technologies Ltd,

2017). The SPAD is operating in Geiger mode when a reverse voltage that is in excess of the breakdown voltage is applied, known as overvoltage. A typical breakdown voltage depends on the fabrication process used when manufacturing the SiPM so varies between manufacturers however, 25 V is a typical breakdown voltage for a SensL SiPM, and an overvoltage of typically between 1 V and 5 V is applied. (Jackson, O'Neill, Wall, & McGarvey, 2016).

Figure 2-9 APD operation overview showing (a) A single microcell configuration, (b) states of a microcell upon photon interaction shown on a current vs voltage graph, (c) Output voltage pulses using a load resistor (Jackson, O'Neill, Wall, & McGarvey, 2016).

For comparison, Hamamatsu SiPMs typically have a breakdown voltage of between 50 V and 70 V, and a 10 V overvoltage range can then be applied. The amount of overvoltage applied determines how much gain is achieved from the SiPM, which is typically a magnitude of between 10<sup>5</sup> and 10<sup>7</sup> charge carriers generated in the gain region of each SPAD, for the charge carrier created by the initial photon interaction. (Hamamatsu Photonics, 2017).

The simplified operation of a single microcell upon photon interaction can be seen in Figure 2-9(b), where biased using an external voltage source in overvoltage operation with no current flow, the breakdown of the SPAD and generation of charge carriers causes current to immediately flow and after the step change reactance through the capacitor, which is the desired event signal, the voltage over the quench resistor starts to rise, seen at point 2 in Figure 2-9(b). This allows the microcell to recover by causing the voltage over the SPAD to lower to below the SPAD breakdown voltage. at which point the current no longer flows and can be seen at point 3 in Figure 2-9(b). The overvoltage is then restored over the SPAD given there is no longer a voltage drop caused by current flow through the quench resistor, returning to point 1 in Figure 2-9(b), and the microcell is ready for the next photon interaction. Using a load resistor to convert current to voltage, a typical output voltage from a microcell (from cathode to anode) upon photon interaction can be seen in Figure 2-9(c), where this faster initial current flow causes the faster rising edge, and the slower recovery resulting in a slower falling edge of the voltage output pulse. (Jackson, O'Neill, Wall, & McGarvey, 2016).

Arrays of tightly packed microcells are then fabricated onto a single SiPM component to allow the detection of multiple photons, demonstrated by the schematic shown in Figure 2-10, where the outputs of many microcells are arranged in parallel to sum the outputs together. Manufactured SiPMs however, will typically have high hundreds or thousands of microcells depending on manufacturer and size variant. Microcell sizes again depend on variant but are typically selectable from arrays populated with 10 µm microcells, to arrays populated with 50 µm microcells. (SensL Technologies Ltd, 2017).

The array of microcells enables the detection of multiple photons arriving at the same time within the SiPM surface area. As each microcell is single photon sensitive it will breakdown regardless of how many photons interact with it, however other microcells on the SiPM will still be ready for photon interaction. Given there is also a recovery time for each microcell, photon interaction may also be missed by a microcell as it had not yet recovered, and this is known as deadtime. (Hamamatsu Photonics, 2017).

Figure 2-10 SiPM construction example using 12 microcells (SensL Technologies Ltd, 2017).

To capture the scintillation photon output using a SiPM, the photon emission wavelength must fall into the optimal sensitivity region of the SiPM, where ideally the peak wavelength of the emitted photons should match the peak sensitivity wavelength of the SiPM. This sensitivity can be selected from variants of SiPMs from different manufactures, to match for the intended scintillation crystal, or other photon source to be used in the application. The sensitivity for a SensL 30035 SiPM can be seen in Figure 2-11, where the peak sensitivity at a wavelength of 420 nm can be seen quoted in terms of Photon Detection Efficiency (PDE). The difference in gain that can be achieved by adjusting the level of overvoltage applied to the SiPM bias voltage can also be seen. (Jackson, O'Neill, Wall, & McGarvey, 2016). PDE is also affected by the fill factor of a microcell array, as only the silicon area containing the

SPAD is photon sensitive, leaving non photon sensitive area used for the quench resistor, array connections, and the fast output capacitor where applicable. Given that microcells are available in different geometrical sizes each with a proportion of sensitive area, the more microcells in an array, a lower fill factor is achieved. (Hamamatsu Photonics, 2017).

*Figure 2-11 Graph showing optimal wavelength for photon detection efficiency at over-voltages of 2.5 V and 5.0 V (Jackson, O'Neill, Wall, & McGarvey, 2016).*

When using SiPMs for scintillation detection, it is common to tile individual SiPM components, connecting them in parallel, in order to maximise photon collection from a larger scintillation crystal. Care must be taken when tiling SiPMs to minimise the gap between them, in order to reduce the probability of missing a photon. Packages for SiPMs vary between manufacturer, where the package used may have an effect on the total sensitive area of the SiPM, and the refractive index of the package material selected will also influence the total system efficiency of detecting photon emissions. Matching this refractive index of the SiPM packaging is often considered along with refractive index of the scintillator crystal, and any optical coupling required to bond the SiPM array to the crystal, such as epoxy. It is also common to wrap or encapsulate crystals in reflective coating, with the aim of eventually reflecting the photons towards the SiPM array. Encapsulation is also necessary in some cases due to the hydroscopic properties of the crystal, such as with an NaI(Ti) crystal. (Jackson, O'Neill, Wall, & McGarvey, 2016).

#### 2.6 Scintillation Event Processing Circuitry using SiPMs

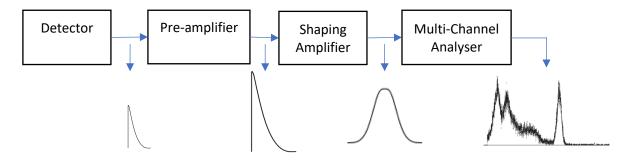

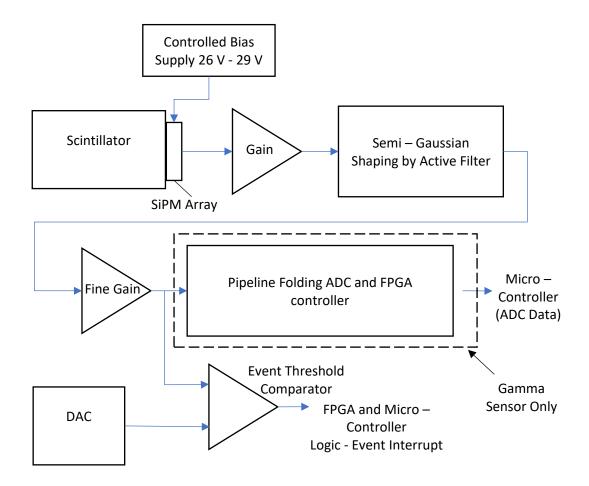

Processing the electrical pulse output from a SiPM upon a scintillation event can be implemented using both analogue and digital circuitry based techniques, whilst implementing varying methods of digitising the data for user readout applications. The complexity of the system that is implemented largely relies on the amount, and type of information that is required from the scintillation process, for example pulse height, pulse shape or both. The system shown in Figure 2-12 is a typical detector system to process electrical signals generated from the SiPM output upon a photon detection from a scintillator.

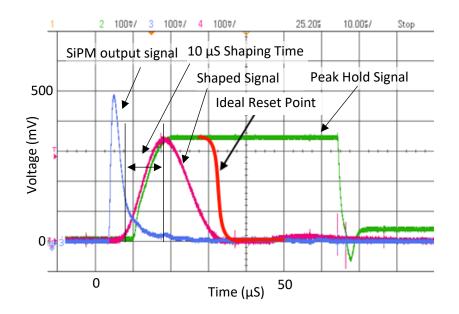

*Figure 2-12 Diagram of a typical detector system, showing the typical electrical signal output at each stage.*

The detector output signal in Figure 2-12 is a typical SiPM output signal upon photon detection from scintillation. The characteristics of the signal are largely delectated by the scintillator used as discussed in section 2.1, with some impact from parasitic capacitance and inductance in the SiPM and connections to it. Low parasitic capacitance is desired for use with faster scintillators applicable for processing of high event rates. Since the typical SiPM output is of the order of 100 mV, a pre-amplifier is used, with a gain set to achieve the scaling of the radiation energy range within the shaper input voltage limits. (Knoll G. F., 1999).

The function of the shaper in a typical detector system is to provide two functions, to integrate the input pulse coming from the amplified SiPM signal, and to define the event within the set shaping time. Since the SiPM pulse shape, with the fast rise time and slower decay tail represents the total energy deposited in the scintillation event, by integrating this signal the scintillation event can be represented by the maximum amplitude of the resulting integration using the shaped pulse. (Noulis, 2016).

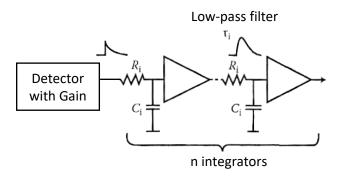

An option for signal shaping is to use low pass, passive resistor – capacitor networks (RC) filters provide an integration function, forming the basis of the implemented shaping filter. The required filter response is referred to as the required shaping time, where the time at which the peak amplitude of the shaped signal is achieved is the end time of the input signal, and hence the end time of the required integration of the scintillation event. This can be achieved as an RC filter preforms as an integrator within the limits of the time constant set by the resistor and capacitor components. (Knoll G. F., Pulse Shape, 1999). In practice, the shaping time is adjusted to that the maximum signal to noise ratio is achieved, as integrating to the end of the event pulse results in integrating further in to the smaller tail signal where signal noise is more dominant. (Abbene, Gerardi, & Principato, 2016). The shaping time of the implemented RC filter, assuming the same RC stages are repeated, is given by Equation 2-2, where  $\tau_s$  is the shaping time, *n* is the number of RC networks or the order of the combined filter, R is the resistance value of each resistor, and C is the capacitance value for each capacitor. (Noulis, 2016).

$$\tau_s = n RC$$

#### Equation 2-2 - Shaping time equation (Noulis, 2016).

An issue for pulse detection applications is that utilising a single RC filter stage yields undesirably long fall time which results in a system that has a limited maximum count rate throughput. As further RC networks are added to the shaping filter, where the time constants are optimised the output response of the filter tends further towards that of a Gaussian shaped output, with close to symmetrical rise and fall shaping times, ideal for improving the ability of a system to process a higher count rate, as the long fall time of the RC filter is reduced. (Knoll G. F., Pulse Shape, 1999).

A further issue when using passive RC networks in pulse detection is the loss of signal amplitude at the output of the filter of each filter stage, resulting in a reduced signal to noise ratio (SNR) and ultimately a degradation in spectrum data. Active filter topologies that implement operational amplifiers to add gain after each RC stage, as shown in Figure 2-13, reduces the loss of signal amplitude, and allows an improved SNR when capturing the peak amplitude of the shaped pulse. (Noulis, 2016).

Figure 2-13 - Diagram showing basic structure of an (RC)<sup>n</sup> second order shaping filter with gain stages (Noulis, 2016).

A more efficient solution over many RC filter and amplifier networks is to use a Sallen and Key topology filter to implement a semi-gaussian shaping element, as a higher order of filter can still be achieved to yield a near ideal gaussian response, with only using 1 amplifier for every 2 filter orders. (Jianbin, Wei, Fang, Yi, & Xing, 2011).

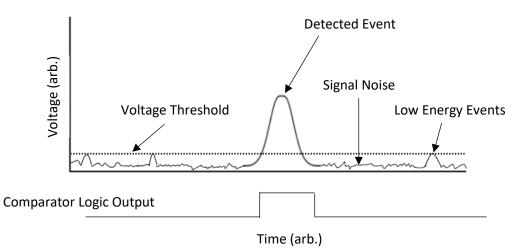

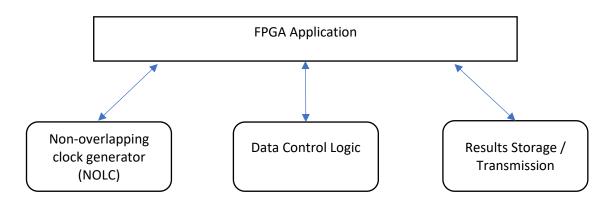

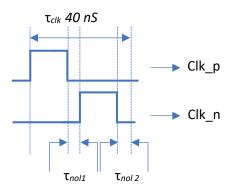

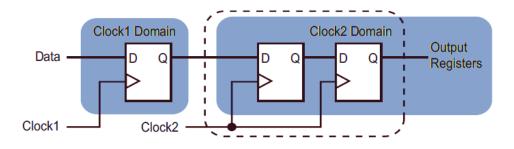

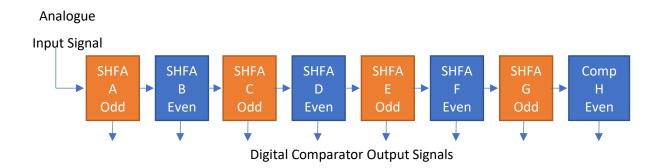

The function of the Multi-Channel Analyser (MCA) is to measure the amplitude of the shaped pulse converting this to digital data used to form the spectroscopic information. For the MCA to operate, a trigger using a threshold voltage comparator is typically employed to detect the rising edge of the incoming event signal. The voltage threshold is set above any signal noise, thus not to trigger when events are not present, as shown in Figure 2-14. The comparator logic output then triggers the internal analogue to digital conversion of the shaped pulse height. (Abbene, Gerardi, & Principato, 2016).