# **University of Huddersfield Repository**

Izod, Toby D.

Electron multiplier supply and signal processing: working towards a system on chip solution

# **Original Citation**

Izod, Toby D. (2018) Electron multiplier supply and signal processing: working towards a system on chip solution. Masters thesis, University of Huddersfield.

This version is available at http://eprints.hud.ac.uk/id/eprint/34864/

The University Repository is a digital collection of the research output of the University, available on Open Access. Copyright and Moral Rights for the items on this site are retained by the individual author and/or other copyright owners. Users may access full items free of charge; copies of full text items generally can be reproduced, displayed or performed and given to third parties in any format or medium for personal research or study, educational or not-for-profit purposes without prior permission or charge, provided:

- The authors, title and full bibliographic details is credited in any copy;

- A hyperlink and/or URL is included for the original metadata page; and

- The content is not changed in any way.

For more information, including our policy and submission procedure, please contact the Repository Team at: E.mailbox@hud.ac.uk.

http://eprints.hud.ac.uk/

# Electron multiplier supply and signal processing:

# working towards a system on chip solution

Toby D. Izod

Submitted for the Degree of Master of Science

University of Huddersfield

11<sup>th</sup> April 2018

i. The author of this thesis (including any appendices and/ or schedules to this thesis) owns any copyright in it (the "Copyright") and s/he has given The University of Huddersfield the right to use such Copyright for any administrative, promotional, educational and/or teaching purposes.

ii. Copies of this thesis, either in full or in extracts, may be made only in accordance with the regulations of the University Library. Details of these regulations may be obtained from the Librarian. Details of these regulations may be obtained from the Librarian. This page must form part of any such copies made.

iii. The ownership of any patents, designs, trademarks and any and all other intellectual property rights except for the Copyright (the "Intellectual Property Rights") and any reproductions of copyright works, for example graphs and tables ("Reproductions"), which may be described in this thesis, may not be owned by the author and may be owned by third parties. Such Intellectual Property Rights and Reproductions cannot and must not be made available for use without permission of the owner(s) of the relevant Intellectual Property Rights and/or Reproductions.

#### **Acknowledgements**

I would like to thank my mother, father and step brother Joshua for their continued support, Dr Alan James Bell, Dr Martin Sibley, Dr Peter Mather and my colleagues at Kromek: Dr Ed Marsden and Richard Haigh.

# Abstract

Despite the primitive operation and challenging practicalities of electron multipliers, they still outperform solid state equivalents in professional level equipment that requires single electron or photon resolution. The advent of the Micro Electronic and Mechanical (MEMs) fabrication process has the potential to miniaturise electron multipliers to allow mass production, reduce physical volume, and minimise part to part variation. The potential impact of MEMs is greatly reduced if secondary electronics associated with such devices cannot be reduced by a similar magnitude.

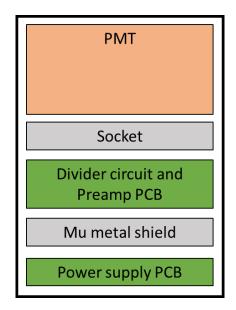

The primary purpose of this research project was to develop the secondary electronics (power supply, divider and decoupling) to enable electron multiplier-based detectors to rival solid-state counterparts in terms of size and power consumption for use in a device the size of a mobile phone. To be comparable with solid state alternatives a *System in Package* (SiP) specification was targeted, with all specialised circuitry occupying the same package as the detector.

To realise the reduction in size required, a number of practical limitations were identified and addressed, including standard capacitor values, behaviour under DC bias and dark discharge across PCBs. These were characterized through hardware measurement, fed into theoretical models and finally electronic assemblies were then designed around these. This bottom-up methodology was shown to have performance advantages when optimising proven topologies under restrictive design limitations.

To demonstrate the size and power reduction available to new detectors, two existing topologies were optimized and evaluated using this bottom-up method. A third new topology was synthesised to better overcome identified shortcomings at a conceptual level. Performance of all three designs is reported.

This proof of concept project was based around a scintillation detector employing a photomultiplier tube. However, it is equally applicable to any discrete dynode or microchannel plate electron multiplier, such as high gain pixilated imaging systems. Devices were tested in a spectroscopic scintillation radiation detection system to evaluate performance deficiencies introduced by reduction of both size and power consumption.

As MEMS manufactured devices are still in an early stage of development, this work did not attempt to demonstrate any overall comparison against solid state equivalents' performance but demonstrated that the secondary electronics would not be the limiting factor in terms of cost or performance in the application to MEMs manufactured electron multipliers.

The project delivered three prototypes that performed against the specification, with limitations highlighted, and a brief for a SoC solution was constructed.

# **Contents**

| Abstract4 |                                                        |                                              |    |  |  |

|-----------|--------------------------------------------------------|----------------------------------------------|----|--|--|

| 1         | 1 Introduction                                         |                                              |    |  |  |

| 2         | Photo Multiplier Tubes11                               |                                              |    |  |  |

| 2.1       | Electron-Multiplier Principles                         |                                              |    |  |  |

| 2.2       | The introduction of the photocathode12                 |                                              |    |  |  |

| 2.3       | Conventional current model                             |                                              |    |  |  |

| 2.4       | Dyne                                                   | ode supply dividers                          | 17 |  |  |

| 2.4.      | 1                                                      | Resistive                                    | 17 |  |  |

| 2.4.      | 2                                                      | Active divider biasing                       | 18 |  |  |

| 2.4.      | 3                                                      | Voltage multiplier biasing                   | 20 |  |  |

| 2.5       | Cou                                                    | pling techniques                             | 20 |  |  |

| 2.5.      | 1                                                      | Resistor-capacitor                           | 21 |  |  |

| 2.5.      | 2                                                      | Transimpedance and charge amplifiers         | 24 |  |  |

| 2.5.      | 3                                                      | Current mirror                               | 27 |  |  |

| 2.5.      | 4                                                      | Signal transformer                           | 29 |  |  |

| 3         | Higł                                                   | n Voltage DC-DC Converters                   | 32 |  |  |

| 3.1       | Casc                                                   | ading power supply topologies                | 32 |  |  |

| 3.2       | Volt                                                   | age Multipliers                              | 33 |  |  |

| 3.2.      | 1                                                      | Cockcroft Walton multipliers                 | 33 |  |  |

| 3.2.      | 2                                                      | Dickinson charge pump multipliers            | 38 |  |  |

| 3.3       | Step                                                   | -up converters                               | 11 |  |  |

| 3.3.      | 1                                                      | Fly back buck-boost converters               | 11 |  |  |

| 3.3.      | 2                                                      | Blocking oscillators                         | 13 |  |  |

| 3.4       | Phas                                                   | se margin considerations of cascaded systems | 14 |  |  |

| 3.5       | Design specifications4                                 |                                              | 16 |  |  |

| 4         | Mul                                                    | ti-layer Ceramic Capacitors (MLCC)           | 16 |  |  |

| 4.1       | Overview                                               |                                              | 16 |  |  |

| 4.2       | Measured results4                                      |                                              |    |  |  |

| 4.3       | Implications for multiplier circuits49                 |                                              |    |  |  |

| 4.4       | Implications for signal circuits                       |                                              |    |  |  |

| 5         | Air breakdown in High Density Printed Circuit Boards51 |                                              |    |  |  |

| 5.1       | Breakdown terms                                        |                                              |    |  |  |

| 5.2       | Measurement of voltage breakdown                       |                                              |    |  |  |

| 5.3       | Updated design rules                                   |                                              |    |  |  |

| 6         | Preliminary Simulations57                              |                                              |    |  |  |

| 6.1 | Divider simulations                        | 57  |

|-----|--------------------------------------------|-----|

| 6.2 | Hardware confirmation                      | 60  |

| 6.3 | Critical component evaluation: MOSFETS     | 62  |

| 7   | Design                                     | 63  |

| 7.1 | High voltage DC-DC converter concept build | 63  |

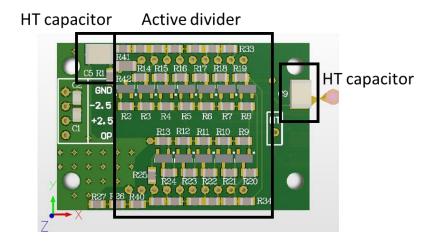

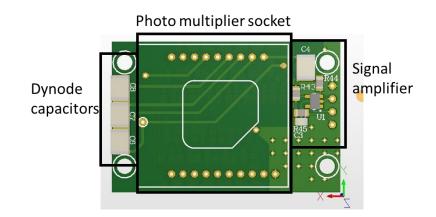

| 7.2 | Active divider prototype                   | 71  |

| 7.3 | Voltage multiplier prototype               | 74  |

| 7.4 | Clamped active divider                     | 77  |

| 7.5 | High density PCB layout                    | 81  |

| 8   | Results and Discussion                     |     |

| 8.1 | Electronic testing                         | 89  |

| 8.2 | Reference circuits                         | 94  |

| 8.3 | Active divider                             | 97  |

| 8.4 | Cockcroft Walton                           | 99  |

| 8.5 | Clamped active divider                     |     |

| 8.6 | Optical linearity                          |     |

| 8.7 | Results summary                            |     |

| 9   | Conclusions and Further Work               | 103 |

| 9.1 | Analysis against performance criteria      |     |

| 9.2 | Achievements                               | 105 |

| 9.3 | Compromises                                | 105 |

| 9.4 | Further development for SOC solution.      |     |

| 10  | Bibliography                               | 109 |

# **1** Introduction

Despite over 80 years having passed since the discovery of electron multipliers, they still have advantages over solid-state devices for critical, professional level applications. These include mass spectrometry, high gain imaging systems such as night vision, Raman spectroscopy, and scintillation radiation detection. In these applications the main advantages over solid state technology are higher speed due to lower intrinsic capacitance and lower self-noise.

The comparative electronic simplicity of solid-state devices has reduced the usage of vacuum electron multipliers based on practicalities, rather than performance. An example of this is spectroscopic scintillation detection for the identification of radio isotopes.

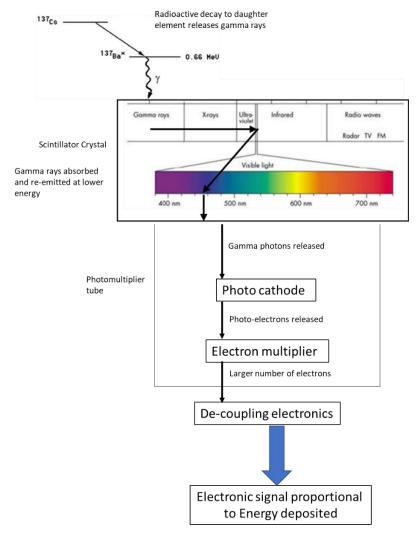

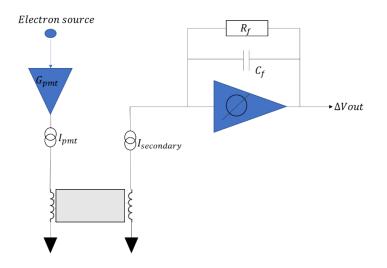

Figure 1.1: Signal flow within a scintillation radiation detector

Scintillation detection is the mechanism in which ionising radiation deposits energy into a crystalline structure which then releases this energy at a longer wavelength [1]. When coupled to a photodetector the emitted energy is converted to a current which is proportional to the energy deposited into the scintillator. The mechanics of such a system is detailed in figure 1.1.

The photodetector needs to have a noise flaw sufficiently low to allow detection with single photon resolution, along with a gain sufficient to couple the signal through to more conventional electronics. One such detector is an electron multiplier coupled to a photo electric cathode forming a Photo Multiplier Tube (PMT).

The current industry options for such a photodetector are either based around a vacuum *Photo Multiplier Tube* (PMT) or a silicon avalanche photo diode array referred to as a *Silicon Photo Multiplier* (SiPM). Both the PMT and SiPM are commonly used, but PMTs have advantages in resolution, temperature stability, speed and range of operation. The disadvantages of PMT detectors are complexity of electronics, physical fragility (especially above atmospheric pressure), susceptibility to magnetic field interference, and greater physical size than solid state alternatives.

When considering hand-held devices, such as personal radiation detectors<sup>1</sup>, the secondary electronics can present a limitation in the selection of a PMT both in terms of power consumption and size. A differentiator between SiPMs and PMT detectors is that the former leads itself to self-contained integrated sensor/electronics designs whereas PMTs tend to require more complex non-integrated electronics. Incorporating electronics into a single package along with the electron multiplier is the main drive behind this research.

<sup>&</sup>lt;sup>1</sup> Typical commercial hand held radiation detectors include:<u>https://en.polimaster.com/catalog/prd-gamma/personal-radiation-detector-pm1703ma/ https://www.kromek.com/product/d3s\_riid/</u>

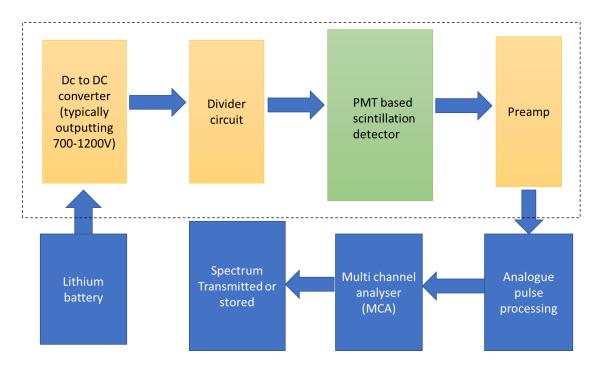

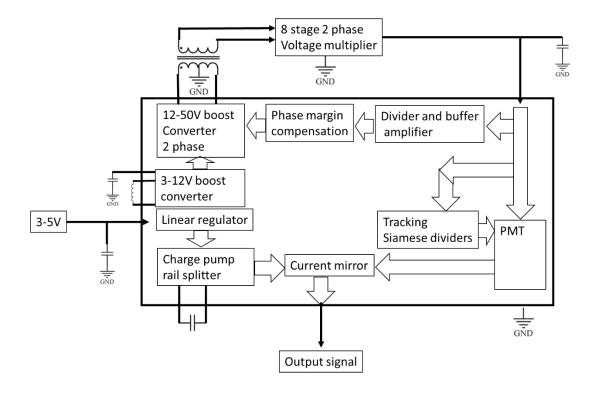

Figure 1.2: Typical hand-held radiation detector block diagram

Figure 1.2 illustrates the block diagram of a spectroscopic detection system, with the front-end module comprising the top half of the diagram. As can be seen this front end needs to accept a varying power source such as a lithium battery and present an electronic derivation of the energy deposited in the scintillation event to be processed by the MCA system.

Advances to the silicon process used to manufacture solid state devices has led to *Micro Electronic and Mechanical Systems* (MEMS) manufacturing [2] being used to produce photo multiplier tubes at significantly reduced physical volume. The potential advantages are being able to 'tile' the devices in a modular fashion, lower accelerating voltage requirements [3], reduced susceptibility to magnetic disruptions and less part to part variation. This would also allow certain elements of the electronics to be integrated with the PMT's silicon wafer.

This work aimed to match the miniaturisation of photo multipliers by providing a proof of concept of a System in Package (SiP) electronics design for voltage generation and signal processing. This would enable the identification of layout considerations of external passive components in a future single chip solution. A spectroscopic radiation detector was used as an application example for this project. The output from the design will feed an external

9

pulse processing circuit (figure 1.2) and multi-channel analyser (MCA). As imaging tubes could be an alternative application for this development, other output configurations were also considered for practicality. These could feature an optical output from a phosphor screen directly mounted directly on the tube or a fast electron detector mounted in place of the anode electrode. Potential applications in this area are discussed later in this work.

In order to demonstrate the outcomes of this project two key areas of improvement over current commercial solutions needed to be addressed: firstly, to reduce the size of the circuitry in order to be consistent with the anticipated size of a MeMs manufactured. Secondly, to reduce power consumption, without a significant reduction in performance to permit integration into hand held instrumentation.

To methodically ensure the final solution presented represents a fully optimised system the following steps were taken:

- Technology review of electron multipliers and power supplies (Chapter 2&3).

- Known practical limitations detailing ceramic capacitors' behaviour under DC bias and air breakdown on Compact PCBs (Chapter 4&5).

- Universal high voltage module design (Chapter 6).

- Design, simulate, optimise and evaluate two industry standard concepts (Chapter 6).

- Synthesise 3<sup>rd</sup> alternate design with practical advantage (Chapter 6).

- Spectroscopic radiation testing in a detection system (Chapter 7)

- Present SoC solution at block diagram based on results from SiP hardware testing (Chapter 7)

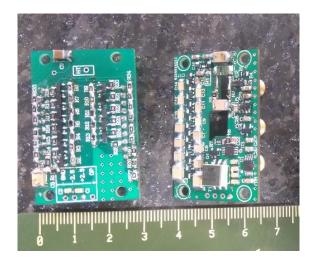

The deliverable of this project was to provide a proof of concept design of a DC to DC converter, divider system and first stage amplifier suitable for translation into a single chip design. This was built as an ultra-high-density surface mount prototype on the same footprint as a Hamamatsu commercially available compact PMT [4].

# 2 Photo Multiplier Tubes

## 2.1 Electron-Multiplier Principles

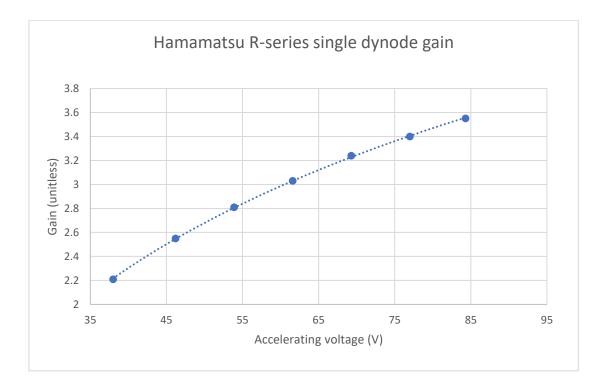

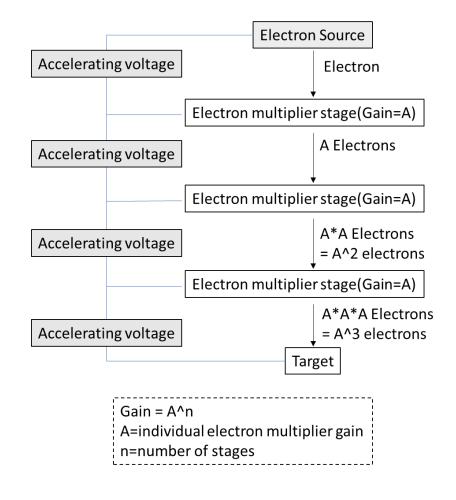

The first report on a secondary emissive surface was made by Austin in 1902 [5]. Initially observed as a hindrance to designers of tetrode valves before the introduction of the pentode and its suppression grid, secondary emission is the mechanism in which an electron directed to a dynode (intermediate electrode) structure via an accelerating voltage will release a number of secondary electrons from this structure [3]. This number of secondary electrons for each collision (A) is based on the accelerating voltage between the dynode and electron source. Figure 2.1 illustrates the effect of varying accelerating voltage on gain of such a device.

By cascading dynode structures with accelerating voltages between them (as shown in figure 2.2) electrons released at the final stage becomes A<sup>n</sup>.

Figure 2.2: Illustration of the concept of cascaded secondary emission dynodes [6]

## 2.2 The introduction of the photocathode

The electron multiplier cascade described in section 2.1 relies on an accelerating voltage between stages to function; however, creating the input conditions for this system are more complex. This takes the form of a Faraday Cup to capture lons, electrons, or charged particles in a vacuum with an accelerating voltage between the cup and the first dynode.

It can also take the form of a photocathode which, in accordance with the photoelectric effect, will release an electron when struck with a photon. When this is coupled to an electron multiplier it forms the basis of the PMT [5] [6].

(1) ALKALI PHOTOCATHODE

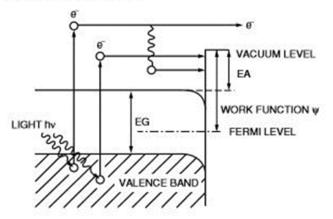

#### Figure 2.3: Photocathode mechanism showing how light releases electrons [6]

The gain in the PMT is carried out in the electron multiplier stage, with no amplification occurring on a photon level. The electrons released by a photocathode are sometimes referred to as *photo-electrons*, although this is in reference to their origin rather than state.

The photocathode functions by releasing an electron via energy transfer from a photon. The photon needs to have sufficient energy to overcome the work function of the semiconductor to release an electron, as illustrated in figure 2.3. As with secondary emission, such low numbers of interactions occur that the relationship between photons that strike the cathode and electrons released is termed quantum probability. The quantum efficiency for the entire device (including the electron multiplier) is a common metric for evaluation of devices [7].

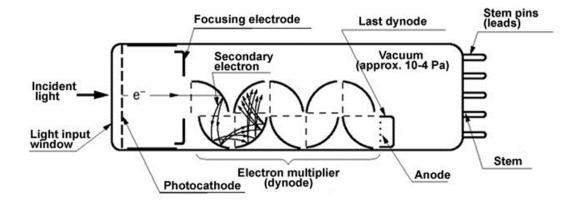

Figure 2.4: Basic vacuum photomultiplier operation [6]

The photocathode takes the form of vapour deposited onto a transparent window of either borosilicate glass, high purity glass, or quartz. This forms the end of an envelope, usually glass, which also contains the electron multiplier. A typical assembly is shown in figure 2.4.

Under normal operation the noise model is single electrons thermally released from either the photocathode or dynodes. These propagate through the electron multiplier mechanism to form thermally triggered false events.

If the accelerating voltage is sufficiently high to cause an electron beam between any pairs of electrodes the PMT will form more conventional shot noise.

#### 2.3 Conventional current model

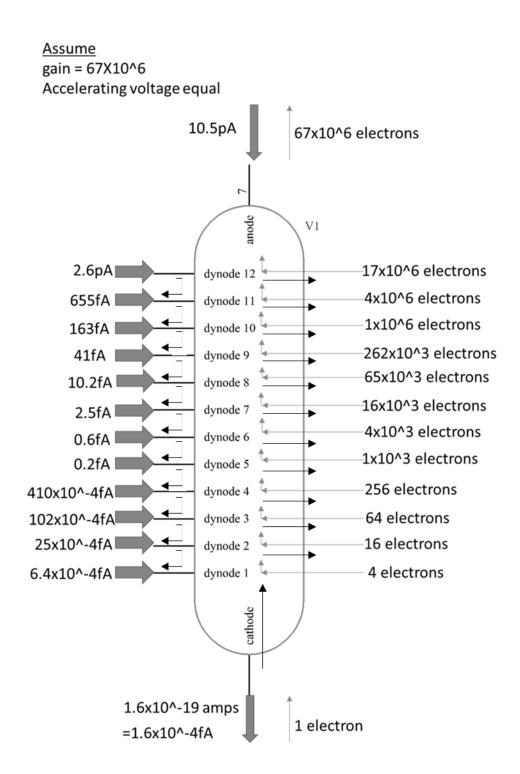

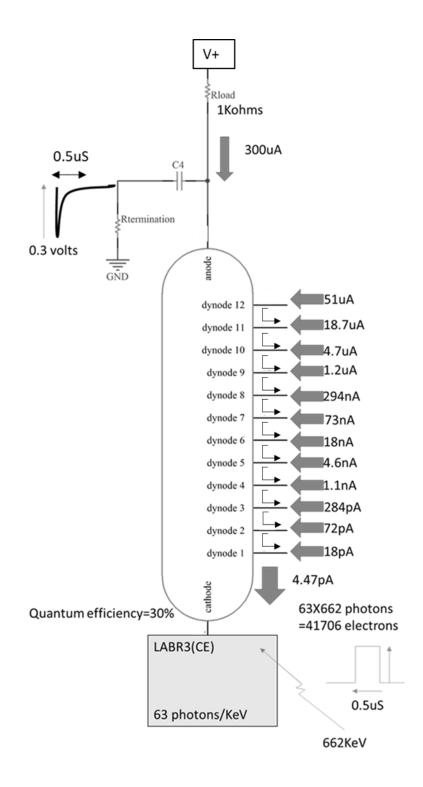

Assuming a scintillator has been correctly specified for the given detector application, the operating point of the tube can then be correctly modelled for a lean electronic design. Figure 2.4 shows a simple, steady state model of a PMT, and this is developed in figure 2.5 with the introduction of the time-domain, a scintillator and corresponding energy of a scintillation event.

The scintillator used for this simulation is *BilLanCe* [8], a lanthanum bromide-based scintillator manufactured by Saint-Gobain crystals. This is brighter (63 Photons/KeV) than many alternative scintillators as photons from the event are delivered in a short window (typically below 0.5µS) and low deviation between identical energy events (resolution).

*Figure 2.4:* Steady state single photon operation of a 12-dynode photomultiplier showing both electron flow and equivalent conventional current.

Figure 2.5: Dynamic operation during a scintillation event.

# 2.4 Dynode supply dividers

Figure 2.5 demonstrates the typical dynamic elements of current required by the dynode structures from a scintillation event. Figure 2.2 illustrates the function of an electron multiplier with individual power supplies. To use a single, rather than multiple, individual dynode supplies, a single high voltage supply can be divided down to power each individual stage.

# Accelerating voltage

#### 2.4.1 Resistive

#### Figure 2.6: Resistive based supply. [6]

The least complex method of achieving this is to use a multi-stage potential divider (as shown in figure 2.6) from a single supply. An example design would be as follows:

A factor of 5X peak dynode current would therefore be:

*Peak dynode current (from simulation)* =  $115.6\mu A$

$115.6 \times 10^{-6} \times 5 = 580 \times 10^{-6}$

$= 580 \mu A$

Assuming 60% supply efficiency at 1000V this would be:

$$Total Power = \frac{V \times I}{efficency}$$

$$= \frac{580 \times 10^{-6} \times 1000}{0.6}$$

$$= 0.986W$$

This power is predominantly dissipated as heat in the resistors making the circuit unsuitable for portable equipment relying on battery power or situations where heat dissipation is problematic, for example space applications.

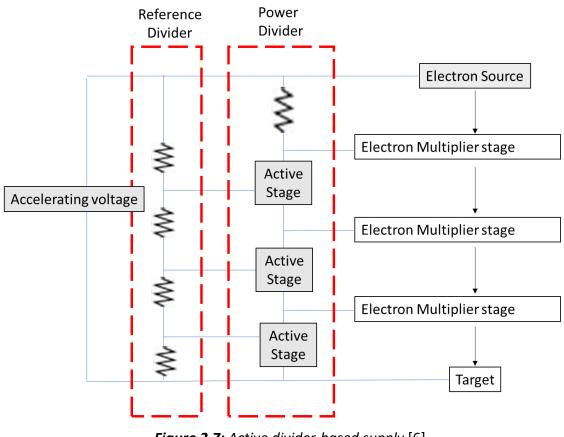

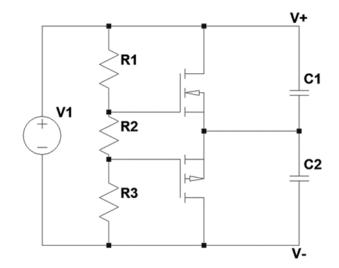

#### 2.4.2 Active divider biasing

Figure 2.7: Active divider-based supply [6]

Figure 2.7 illustrates the concept of dividing down a single voltage rail to cascaded electron multiplier stages using active devices rather than a resistive potential divider. The active stages typically take the form of a cascode chain of source or emitter follower amplifiers. These take a voltage input from the (high impedance) reference divider chain and provide sufficient drive to supply the dynode's current requirements. A single supply is used driving both a low current reference chain and a dynode driving chain in parallel. The principle is that any differential voltage between the reference and dynode chains will cause an increase in base current in the active elements, increasing current through that element of the dynode chain and enabling the dynode to be held at the correct accelerating voltage and supply ample current during an event.

At least one resistive element must be included in the dynode chain at the emitter (or source) of the lowest active device which provides the limitation to the system for the illustrated active system. An example design would be as follows:

Assuming 5M $\Omega$  leakage resistance, 5 $\mu$ A reference chain current, 12 active stages and a 1000V supply the quiescent current draw would become:

$$I = \left(\frac{V}{R}\right) + reference \ current$$

$$= \left(\frac{1000}{5 \times 10^6 + (12 \times 5 \times 10^6)}\right) + 5 \times 10^{-6}$$

$$= \left(\frac{1000}{65 \times 10^6}\right) + 5 \times 10^{-6}$$

$$= 20\mu A$$

Assuming 60% supply efficiency at 1000V this would be:

$$Total power = \frac{V \times I}{efficency}$$

$$= \frac{1000 \times 20 \times 10^{-6}}{0.6}$$

$$= 33 \times 10^{-3}$$

$$= 33mW$$

Significantly lower than the resistive only design

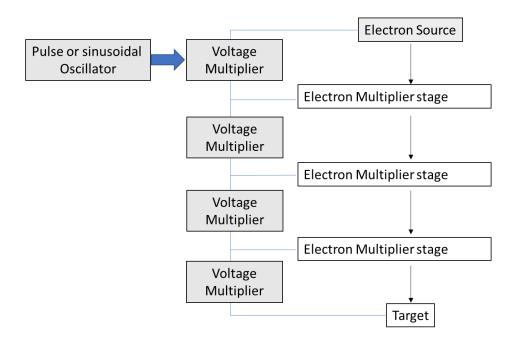

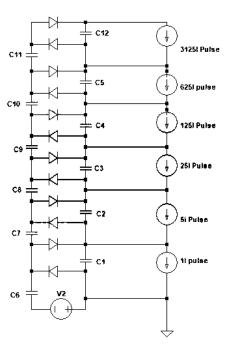

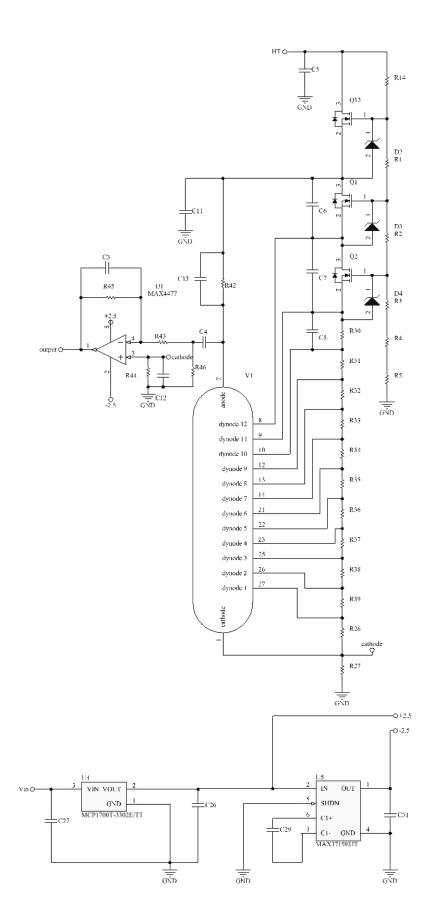

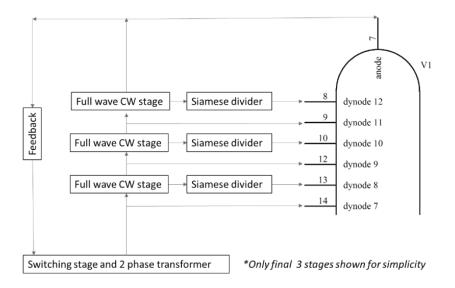

#### 2.4.3 Voltage multiplier biasing

#### Figure 2.8: Series rectifier-based supply [6]

Figure 2.8 illustrates a third possible method of powering the PMTs dynode chain. The Cockcroft Walton series voltage rectifier is commonly used for generating a single high voltage supply; however if the number of stages exceeds the number of dynodes in the PMT then outputs can be taken from each multiplier stage. In comparison with the previous examples, the steady state current draw is only the leakage, however it potentially requires a filter stage for every dynode as well as the anode supply, making it either bulky or noisy. CW ladders can also suffer from complex droop effects, to be discussed in 3.1.

#### 2.5 Coupling techniques

Although the previous section has detailed the mechanics of the photon activated electron multiplication within the photomultiplier, the current proportional to any optical event needs to be coupled through to subsequent measurement circuits.

This can be achieved through a variety of means, each of which will have differing effects on linearity, resolution, dynamic range, and ease of coupling to following stages.

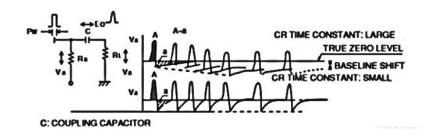

At an early stage in the design the decision must be made as to whether AC or DC coupling will be more suitable for the system. AC coupling will introduce signal artefacts related to the coupling capacitor charging and discharging, resulting in a rate dependant baseline shift if these effects overlap (see figure 2.9) as well as capacitive fly back effects. DC coupling on the other hand will result in an offset varying with temperature due to Dark current components and DC leakage across the component.

#### Figure 2.9: Effect of count rate on baseline for a capacitively coupled system. [6]

The relevance of this is that typically thermal offset variation will be far slower than rate dependant baseline shift, and so is easier to correct. The advantage of AC coupling is that it requires no active components so is likely to be more robust, considering the high voltages involved.

Finally, when dealing with the practicalities of producing a high-performance system, simplicity of PCB layout and vulnerability to induced noise need to be considered.

#### 2.5.1 Resistor-capacitor

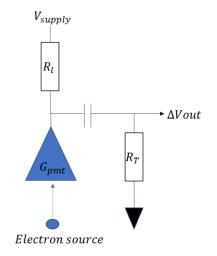

Figure 2.10: Resistive loading of a photomultiplier tube.

Figure 2.10 illustrates the most common form of decoupling a PMT, the resistively loaded AC coupled anode follower. Varying PMT current through  $R_L$  results in a voltage swing across the anode resistor in proportion to anode current. As the coupling capacitor is charged to the supply voltage (V+) the AC signal is coupled through to the terminating resistor,  $R_T$ .

The major advantage of this circuit is its simplicity. It only requires 3 additional components and as an industry standard produces results in line with end user expectations.

The disadvantages associated with AC coupling have been discussed previously. In addition to this, the voltage developed across  $R_L$  is subtracted from the anode voltage. As this anode voltage has a linear relationship with gain of the electron multiplier this produces a non-linearity in proportion to the load value.

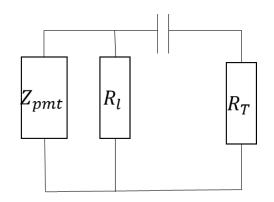

#### *Figure 2.11: Resistive loaded photomultiplier tube equivalent output impedance.*

The small signal output impedance (as shown in Figure 2.11) becomes the PMT in parallel with  $R_{load}$ . The PMTs impedance is typically orders of magnitude higher than the load resistance so output impedance can be considered as  $R_L || R_T$ .

The relationship between energy deposited in a scintillation event and the output voltage is given in the following example:

Ignoring any dark current in the PMT the dynamic current will be:

$$I_{Rl\ Event} = Single\ electron\ event \times G_{pmt}$$

$$V_{RL} = I_{RL\_Event} \times R_L$$

After introducing the AC coupling stage:

$$\Delta V_{out} = I_{RL \ Event} \times (R_L || R_T)$$

So the output voltage when used with a scintillation radiation detector could be calculated as the following simplified example (ignoring time domain):

Scintillator sensitivity = 50 photons per KeV, Event energy = 1KeV

Photocathode efficency = 30%,  $G_{pmt} = 60 \times 10^6$

$R_l = 1K\Omega$  ,  $R_T = 10K\Omega$

*Electron current* =

$$0.16 \times 10^{-15} A$$

*Electrons released = Event energy × Scintillator sensitivity × Cathode efficency*

$= 1 \times 50 \times 0.3$

= 15 *photoelectrons*

$\Delta Vout = photoelectrons(I_{RL_{event}} \times (R_L || R_T))$

= photoelectrons(electron current  $\times G_{pmt} \times (R_L || R_T))$

$= 15(0.16 \times 10^{-15} \times 6 \times 10^{6} \times (1 \times 10^{3} || 10 \times 10^{3})$

$= 15(9.6 \times 10^{-9} \times (909))$

= 0.131 mV/KeV

#### 2.5.2 Transimpedance and charge amplifiers

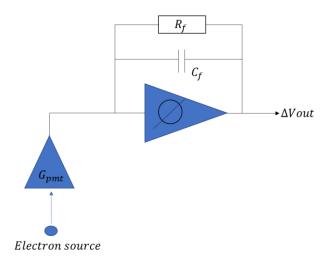

#### Figure 2.12: Transimpedance coupling of a photomultiplier tube.

Figure 2.12 illustrates the coupling of a PMT to a transimpedance or charge amplifier. This is DC coupled so will also amplify the dark current associated with the tube but avoid rate dependant baseline shifts where a capacitively coupled device would tend toward AC. A negative high voltage supply is typically applied to the cathode with the anode at 0V to allow coupling to low voltage circuitry.

The disadvantages to such a system are that inverting high ratio power supplies require more components to produce and PMTs with exposed metalwork often have it connected to the cathode internally creating isolation concerns.

If the amplifier's feedback is predominantly resistive it will be in transimpedance mode of operation with change in output given as the following:

$$\Delta Vout = -I_{PMT} \times R_f$$

So, to give the same sensitivity as the previous resistively coupled example:

$$\Delta Vout = 0.131 mV/KeV$$

Scintillator sensitivity = 50 photons per KeV

*Event energy* = 1*KeV, Photocathode efficency* = 30%

$$G_{pmt} = 60 \times 10^6$$

Electron current =

$$0.16 \times 10^{-15} A$$

*Electrons released = Event energy × Scintillator sensitivity × Cathode efficency*

$= 1 \times 50 \times 0.3$

$= 15 \ photoelectrons$

$R_f = \Delta Vout / -I_{in}$

$= \frac{0.131 \times 10^{-3}}{electron \ current \times G_{pmt} \times electrons}$

$=\frac{0.131\times10^{-3}}{0.16\times10^{-15}\times60\times10^{6}\times15}$

$$=\frac{0.131\times10^{-3}}{1.44\times10^{-7}}$$

# $R_f = 909\Omega$

If the amplifier's feedback is set to be predominantly capacitive then it becomes a charge sensitive amplifier.

Gain becomes:

$$\Delta Vout = Q/C_f, \ Q = It, \Delta Vout = (I \times t)/(C_f)$$

The feedback resistor ( $R_f$ ) is still included to discharge C  $_f$  between events and so sets the time constant of the circuit. To set gain to that of previous examples C  $_f$  would become equal to:

$\Delta Vout = 0.131 mV/KeV$

*Event duration* = 1us, *Event energy* = 1KeV

Photocathode efficency = 30%,  $G_{pmt} = 60 \times 10^{6}$

*Electron current* =  $0.16 \times 10^{-15} A$

*Electrons released = Event energy × Scintillator sensitivity × Cathode efficency*

$= 1 \times 50 \times 0.3$

= 15 photoelectrons

*Input charge* = *It*

= electron current  $\times$  photoelectrons  $\times$  G<sub>pmt</sub>  $\times$  t

$= 0.16 \times 10^{-15} \times 60 \times 10^{6} \times 15 \times 1 \times 10^{-6}$

$= 14.4 \times 10^{-12}$

= 0.144 pC

$\Delta Vout = Q/C_f$

$$C_f = \frac{Q}{\Delta Vout}$$

$$=\frac{14.4\times10^{-14}}{0.131\times10^{-3}}$$

$$= 1.01 \times 10^{-9}$$

= 1.01 nF

#### 2.5.3 Current mirror

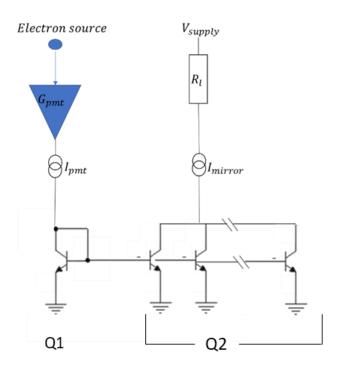

*Figure 2.13: Current mirror coupling of a photomultiplier tube.*

Figure 2.13 demonstrates the application of a bipolar current mirror to couple anode current (through diode connected Q1) through to a separate chain from the collector of Q2.

This potentially removes the compression effects associated with resistive coupling and has none of the associated AC coupling effects. However, it does require a further element to decouple to a stage closer to ground for the positive HT variant, doubling the anode current.

For example, if the required 0.131mV/KeV was required with a 50 $\Omega$  source impedance from a single current mirror stage the mirror ratio would be:

$\Delta Vout = 0.131 mV/KeV$ , Scintillator sensitivity = 50 photons per KeV

*Event energy* = 1*KeV, Photocathode efficency* = 30%

$G_{pmt} = 60 \times 10^6$

*Electron current* =  $0.16 \times 10^{-15} A$

$$R_l = 50\Omega$$

*Electrons released = Event energy × Scintillator sensitivity × Cathode efficency*

$$= 1 \times 50 \times 0.3$$

= 15 photoelectrons

$event \ current = electron \ current \times photoelectrons \times G_{pmt}$

$= 0.16 \times 10^{-15} \times 60 \times 10^{6} \times 15$  $= 14.4 \times 10^{-6}$

$$= 144nA$$

mirrored current =

$$\frac{\Delta V}{R_l}$$

$$=\frac{0.131\times10^{-3}}{50}$$

$$= 2.62 \times 10^{-6}$$

$$= 2.62 \mu A$$

$mirror\ ratio = \frac{mirror\ ed\ current}{event\ current}$

$$=\frac{2.62\times10^{-6}}{0.144\times10^{-6}}$$

#### *Mirror ratio* = 18.19

# 2.5.4 Signal transformer

Figure 2.14: Transformer coupled Photomultiplier tube

Figure 2.14 illustrates a development of the resistive load of the previous example to introduce a pulse transformer. As the PMT pulls current through the primary winding of the transformer it is charged, which is then coupled to the secondary winding. In this example the current induced in the secondary is coupled to a transimpedance amplifier.

Figure 2.15: Noise cancelling diagram

Figure 2.15 highlights a potentially useful addition of a tertiary winding in series with the primary, with an intersecting node bypassed to ground [9]. This arrangement sums ripple in the primary with its inversion in order to common mode reject the ripple from the secondary (output) winding.

Although this adds to cost and component count it has an advantage over the previous DC coupled transimpedance method that less gain is required, allowing a lower specification amplifier to be used.

For example, if a 1:3 transformer were used to couple the PMT to transimpedance amplifier from the previous example the new value of  $R_{f}$  would be:

*Event energy* = 1*KeV, Photocathode efficency* = 30%

$G_{pmt} = 60 \times 10^{6}$ , Electron current =  $0.16 \times 10^{-15} A$

Turns ratio = 3:1

*Electrons released = Event energy × Scintillator sensitivity × Cathode efficency*

$1 \times 50 \times 0.3 = 15$  photoelectrons

$Transfromer\ secondary\ current = (electron\ current \times G_{pmt} \times electrons) \times (\frac{1}{Turns\_ratio})$

$= 0.16 \times 10^{-15} \times 60 \times 10^{6} \times 15 \times 3$  $= 1.44 \times 10^{-7} \times 3$  $= 4.32 \times 10^{-7}$

=0.43µA

$R_f = \Delta Vout / -I_{in}$

$$= \frac{0.131 \times 10^{-3}}{0.43 \times 10^{-6}}$$

$$R_f = 304\Omega$$

The required gain bandwidth product for the amplifier then can be reduced from the previous example as follows, assuming the following parameters:

$$C_{pmt} = 2pF$$

,  $C_{transformer \, secondary} = 10pF$ ,  $C_f = 20pF$

$$F_{GBW} > (\frac{C_{in} + C_f}{2\pi R_f C_f^2})$$

So the required gain bandwidth for the DC coupled amplifier becomes:

$R_f = 909\Omega$   $C_{pmt} = 2pF$   $= \frac{2 \times 10^{-12} + 20 \times 10^{-12}}{2\pi \times 909 \times ((20 \times 10^{-12}) \times (20 \times 10^{-12}))}$   $= \frac{22 \times 10^{-12}}{2854.26 \times 400 \times 10^{-24}}$

$$=\frac{22\times10^{-12}}{1.14\times10^{-18}}$$

For amplifier selection this would be rounded to:

$$F_{gbw} > 20MHz$$

For the transformer coupled example:

$$C_{transformer \ secondary} = 10pF$$

$$R_f = 304\Omega$$

$$\frac{10 \times 10^{-12} + 20 \times 10^{-12}}{2\pi \times 909 \times ((20 \times 10^{-12}) \times (20 \times 10^{-12}))}$$

$$= \frac{30 \times 10^{-12}}{964.56 \times 400 \times 10^{-24}}$$

$$= \frac{30 \times 10^{-12}}{3.82 \times 10^{-19}}$$

$$= 7,853,403$$

For amplifier selection this would be rounded to:

=

$$F_{gbw} > 8MHz$$

As can be seen from the previous example the required gain bandwidth from any opamp used as a transimpedance amplifier is significantly reduced with the inclusion on a coupling transformer, providing gain system gain requirements are equal. This also adds isolation from high voltage photomultiplier circuits at the expense of AC coupling.

# 3 High Voltage DC-DC Converters

### 3.1 Cascading power supply topologies

In order to achieve the high ratio power supply multiplication ratios required for reaching the required high voltage rail from a typical battery voltage, various topologies will be employed in combination. The nature of this development lent itself to a single feedback regulation loop so the various multipliers and first stage converters will be reviewed to this end. [10] [11] As the development was intended to be equally applicable to most currently used image tubes and electron multipliers this ratio varies between 1:200 for a 650V PMT and 1:6000 for a 20KV micro channel plate base image intensifier. To encompass the required headroom for adjustment the PMT based scintillation detector used for this development required an initial 1:300 (1KV) capable system.

#### 3.2 Voltage Multipliers

#### 3.2.1 Cockcroft Walton multipliers

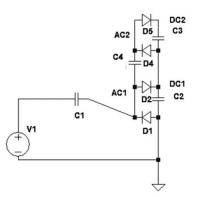

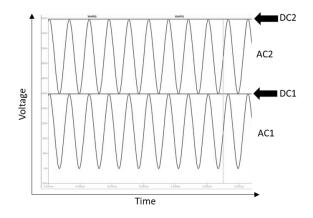

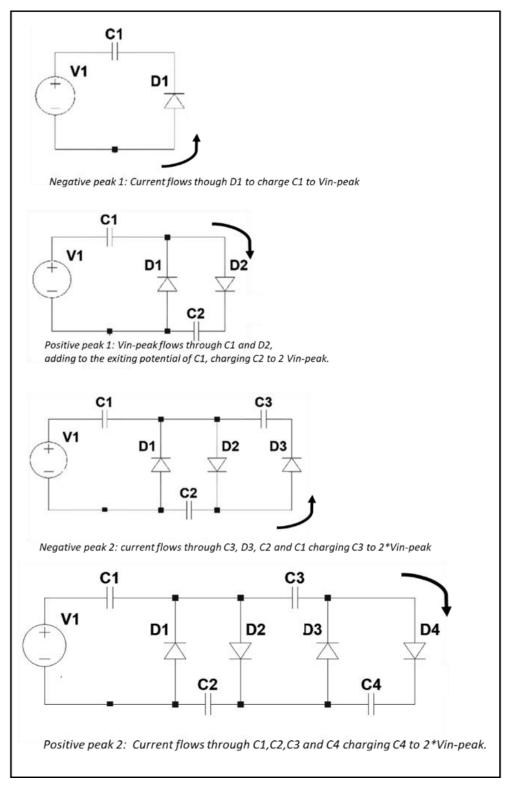

Although loosely based on the *Schenkel multiplier and Greinacher multiplier* the Cockcroft Walton designed by *John Cockroft* and *Ernest Walton* was famously used when they worked alongside *Ernest Rutherford* to split a lithium atom. Figures 3.1 & 3.2 shows the operation of the circuit. A 2-stage circuit is used as an example as it both illustrates the principal of operation and the cascode interaction between stages.

Figure 3.1: Two stage Cockcroft Walton multiplier/ series rectifier.

Figure 3.2: Waveforms at points of a Cockcroft Walton multiplier.

The original Cockcroft Walton multiplier generator used active stages (switched triodes) in the first stage, however these can be omitted to demonstrate the concept. [12] [13]

Figure 3.3: The pumping mechanism of voltage multiplication in series rectifier circuits.

Capacitors C1 and C3 can be considered as primarily coupling capacitors, whereas C2 and C4 are smoothing capacitors. These descriptions all assume zero supply impedance from the AC source so in application this will take significantly longer than the time period of a single wave for each stage to charge. [14] [15] [16]

Taking an output from the series combination of the C2-C4 chain:

$$V_{out} = V_{c2} + V_{c4}$$

$$= (2 \times V_{inpeak}) + (2 \times V_{inpeak})$$

$$= 4 V_{inpeak}$$

So for an n-stage network:

$$V_{out} = 2n(V_{inpeak})$$

Ignoring any diode losses, the intrinsic loss of the circuit is given by: (term removed)

$I_l$  = output current, F = drive frequency, C = capacitance, n = nuber of stages

$$V_{droop} = \left(\frac{I_l}{6 \times F \times C}\right) \times \left(4n^3 + 3n^2 - n\right)$$

Which leads to an output of:

$$V_{out} = \left(2n \times V_{inpeak}\right) - \left\{\left(\frac{I_l}{6FC}\right) \times (4n^3 + 3n^2 - n)\right\}$$

$$V_{ripple} = \left(\frac{I_l}{2FC}\right) \times \left(n \times (n+1)\right) \qquad (x)$$

To build a high-performance system including these limitations can cause issues with dynamic noise flaws and an equivalent supply impedance, especially when as previously discussed a PMT has a voltage dependent gain. The polynomial nature (ix) of these can be difficult to compensate for and/or narrow the range of stable operation if this circuit is included in any closed loop control systems.

A development to this circuit is to taper the capacitor values so:

$$C1\&2= nC, C3\&4=(n-1)C, C5\&6=(n-2)C, etc.$$

(xi)

As this source of loss is caused by each stage being driven from a combination of the source voltage and the subsequent stage, tapering the capacitors in this manner reduces the losses to that of a single stage ladder, which due to the n<sup>2</sup> and n<sup>3</sup> terms can be significant in longer chains. The droop and ripple is given as:

$$V_{ripple} = n \times (\frac{I_l}{FC})$$

$$V_{droop} = n^2 \times \left(\frac{I_l}{FC}\right)$$

The circuit is equally suitable for pulsed circuits but 2. V in- peak is substituted for V pulse.

| Required<br>multiplier | Available<br>multiplier |  |  |

|------------------------|-------------------------|--|--|

| 1                      | 1                       |  |  |

| 2                      | 1.8                     |  |  |

| 3                      | 2.2                     |  |  |

| 4                      | 3.3                     |  |  |

| 5                      | 3.9<br>4.7              |  |  |

| 6                      |                         |  |  |

| 7                      | 5.5                     |  |  |

| 8                      | 6.8                     |  |  |

| 9                      | 8.2                     |  |  |

| 10                     | 10                      |  |  |

#### Table 1: Approximation of linear multipliers for capacitor selection

Although this removes the polynomial element of the transfer function it does rely on capacitors being available in suitable multipliers. Table 1 highlights the difference between desired and available multipliers for capacitor values.

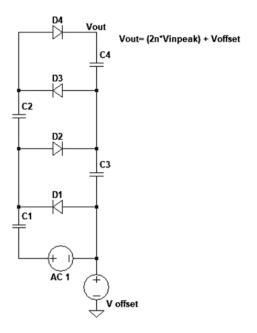

Figure 3.4: Offset half wave series rectifier circuit

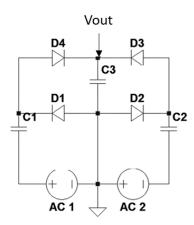

Figure 3.5: Full wave series rectifier

Figure 3.6: Bipolar series rectifier example.

Figures 3.4 to 3.6 and the following analysis demonstrates the half wave operation of the circuit; however, it can be used in full wave (figure 3.5), bipolar (figure 3.6), or with a DC offset (figure 3.4).

The advantage of this circuit is primarily its simplicity. Its passive nature making it extremely efficient for low load supplies, and as each stage is charged to the rectified input voltage. Bulky high voltage components are kept to a minimum. The disadvantages are that it has a complex transfer function for closed loop systems and requires careful selection of driver circuits.

#### 3.2.2 Dickinson charge pump multipliers

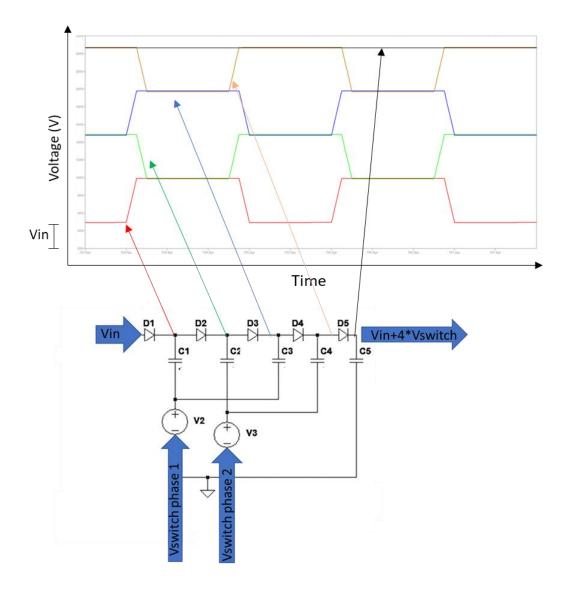

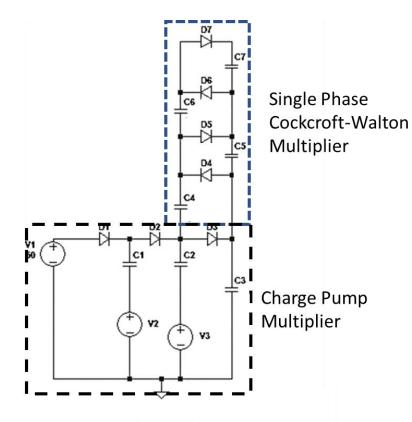

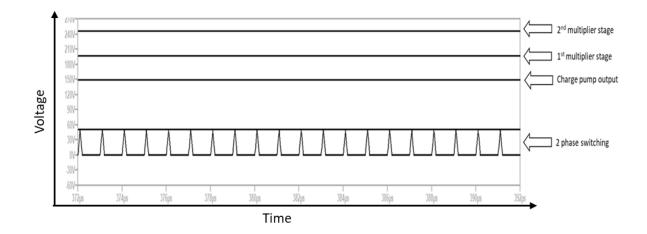

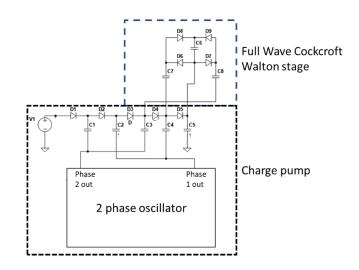

An active alternative to the CW multiplier is the *Dickinson Charge pump voltage multiplier*. There are alternative charge pumps, but these are largely improved in low voltage performance. Its operation is demonstrated in figure 3.7. It consists of a DC input (V1), and output peak detector (D5&C5), a 2-phase oscillator (V2 & V3) and a number of switching stages.

Figure 3.7: Dickinson charge pump multiplier

Whilst the oscillator is in its low state C1 charges to V1-diode drop. V2 pulses the lower side of C1 between V1 and V1+V2. Running V2 and V3 out of phase allows the D2 and C2 to act as a peak detector when V2 is high.

Therefore, the output becomes:

$$V_{out} = V_{in} + (V_{switch} \times n)$$

Or if V<sub>in</sub> = V <sub>switch</sub> then:

$$V_{out} = V_{in}(n+1)$$

This is not a direct replacement for a Cockcroft-Walton multiplier as it takes a DC input; however the switching pulse amplitude does need to be similar to that required to drive the previous multiplier in full wave form. In actuality it needs a DC and a 2 phase pulsed input, rather than the single pulsed input of the CW multiplier. The point where it fails to be competitive for high voltage circuits is that C1 needs to be rated to Vin, as with the CW multiplier, but C2 needs to be rated to 2\*Vin and C3 to 3\*Vin etc. This makes the circuit potentially bulky and expensive.

**Figure 3.9:** Implementation of coupling a switched charge pump to a Cockcroft Walton <u>stage</u>

Figure 3.11: Hybrid CW/Dickinson charge pump example

## 3.3 Step-up converters

## 3.3.1 Fly back buck-boost converters

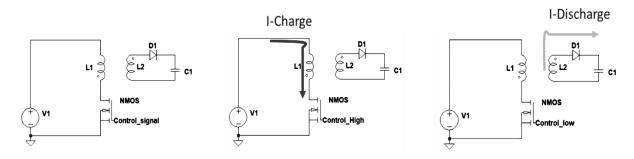

Figure 3.12: Details of buck-boost operation.

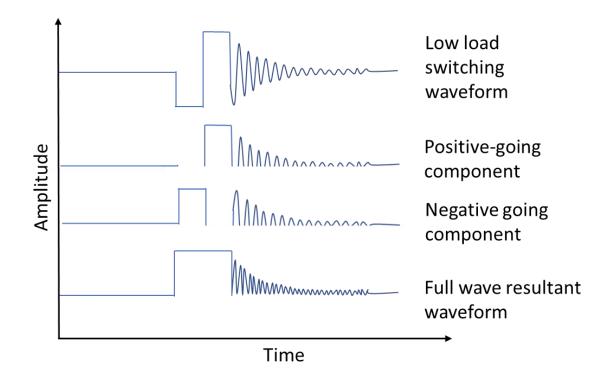

Often referred to simply as a Flyback converter, the *Flyback-buck-boost* converter is either a PWM (pulse width modulation) or PFM (pulse frequency modulation) topology. Only the flyback implementation is to be considered, as the ratio between input and output limits the use of simpler topologies.

The simplified principle of operation is demonstrated in figure 3.12; the switch is closed causing current *I\_charge* to flow, charging the primary winding. During this period the rectifier diode is reverse biased. When the switch is opened the diode becomes forward biased, allowing current Id to flow, charging the smoothing capacitor from the transformer secondary. In its simplest terms the ratio of input to output voltage is based on the ratio the switch is closed to open.

The next level of complexity is that the converter can either be run in *continuous* or *discontinuous* mode, vastly altering its characteristics and transfer function:

- In continuous mode the inductor will not fully discharge on each cycle. This residual charge is given as a percentage of the inductors total charge.

- In discontinuous mode the primary completely discharges each time the switch is opened. A simplification of this is that discontinuous mode offers higher step up ratios at the expense of noise, efficiency and linearity, which equates to stability in a feedback-based system.

They can also be considered as a binary situation whereby a converter stage is either continuous or discontinuous as load conditions will dictate its operating region. It is therefore a case of managing the point at which a converter will switch between these conditions.

The distinction that enables this circuit to act as a switching regulator as opposed to a simple proportional voltage converter is the mechanism controlling the switching of the circuit. A control signal proportional to the output voltage is compared with a reference voltage (or 'set-point') to generate an error term which is in turn used to generate a control signal from a VCO (voltage-controlled oscillator). This VCO can either generate a suitable PWM or PFM to drive a suitable switching device. A PWM signal will consist of a constant

42

period, variable on time signal whereas a PFM will consist of a constant on time, variable period waveform.

The difficulty with this approach is that in an effort to raise efficiency of commercial amplifiers they typically use a combination of both current and voltage feedback along with burst mode PWM. This resembles PWM as a switching function superimposed upon a low frequency PFM and variable frequency PWM.

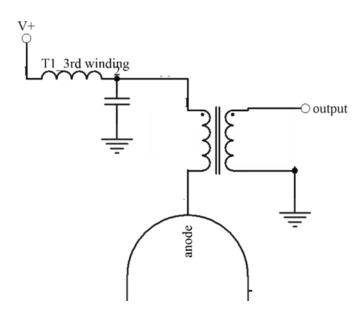

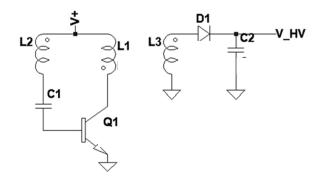

#### 3.3.2 Blocking oscillators

#### *Figure 3.13: Hartley/Blocking oscillator (L1,L2,L3 single transformer)*

The blocking oscillator is a relatively basic design dating from the mid-1930s in thermionic valve form. Shown in figure 3.13, It is based around a transformer with a primary either connected to the anode or collector circuit and a secondary driving either the grid or base circuit. The oscillation on the primary winding can either be rectified, or for higher voltages a tertiary winding of higher ratio (L3) can be used to step this up for increased output. Despite its simple nature this is still used for commercial low current high voltage supplies due to its small footprint, simple nature, low design cost, and proven results.

In operation the collector current charges L1 which couples through to L2 out of phase, blocking the collector current. This process will repeat resulting in sinusoidal oscillation of the collector current. The time constant of this is set by base capacitor C1. A tertiary winding with a high turns ratio relative to L1 steps up these oscillations and is then rectified (D1, C2) to form a DC output. This DC output is proportional to the input supply voltage without any means of adjustment. The resonance of the circuit will be affected by the forward current gain of Q1 so will vary dramatically with temperature.

43

Commercial examples [17] are commonly available but will typically have a several hundred-mW offset power along with a poor efficiency making them unsuitable for portable equipment. This is high enough to prevent battery powered equipment running for extended periods.

The fundamental disadvantage of this circuit is difficulty of adjustment as stated above. As has been discussed in section 1.1 the acceptable voltage variation is very small for a photo multiplier circuit, so feedback to compensate for voltage multiplier losses is an essential part of the system. The most common method of implementing this is to take the V+ input from the output of an operational amplifier (able to supply sufficient output current) controlled by a processed feedback signal post multiplier. This simple yet effective method has the disadvantage that losses are incurred in the voltage difference between the V+ level and the system input voltage along with the quiescent current of substantial operational amplifiers.

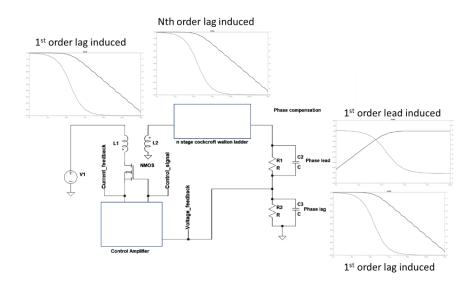

#### 3.4 Phase margin considerations of cascaded systems

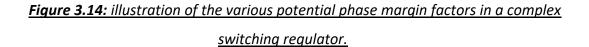

In a closed loop system the phase margin can be defined as a phase difference between nodes in the system, normally system input and returned feedback signal. Any significant lag (or lead) in this mechanism can result in system instability.

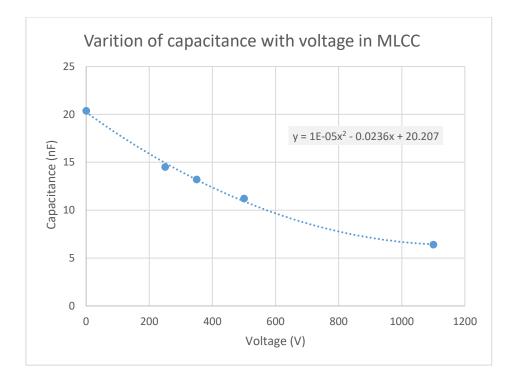

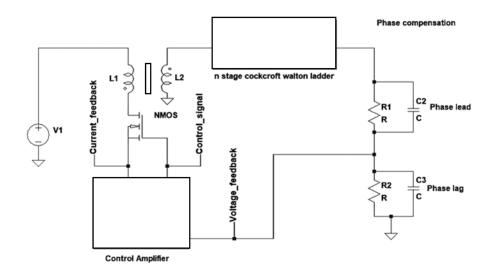

Figure 3.14 illustrates some of the various factors affecting this phase throughout a typical system. In simpler systems the current through the switch can be monitored to control the output voltage, however this can do little to compensate for droop of a voltage multiplier included in the system. To maintain a stable system output using final voltage feedback the control input and switching behaviour needs to have a phase margin within certain limits to avoid instability.

#### Figure 3.15: Phase margin of a single Cockcroft Walton series rectifier.

As can been seen in the simulation illustrated in figures 3.15 each Cockcroft Walton stage will introduce a 90-degree phase lag.

For example a converter based around a PWM flyback converter with an inverting transformer and 5 CW stages would have a phase margin of:

Converter margin + flyback margin + n(multiplier margin) = total phase margin

$$+90 + -180 + 5(-90) = -540^{\circ}$$

Or in real terms a 180 degree phase margin

This would need to be corrected if used in the feedback loop of a 3<sup>rd</sup> party boost or flyback converter system intended for a less complex system. The equivalent 180° lag will create steady state instabilities whilst the actual 540° lag will cause higher inrush currents on start-up.

## 3.5 Design specifications

The following specification has drawn up for a System in Package (SiP) PMT module capable of competing with solid state alternatives at a practical level.

- Footprint equal to that of an equivalent area solid-state detector module.

- Power supply requirements equal to that of a solid-state module with the inclusion of a buffer amplifier.

- To provide positive going output signal to be retrofittable in the place of a solidstate detector.

- Suitable to be battery powered.

- To incur minimum degradation in performance of its low power consumption and reduced form factor.

# 4 Multi-layer Ceramic Capacitors (MLCC)

## 4.1 Overview

High density surface mount boards demand the use of MLCC on the grounds of cost, size and availability. The trade-off for a compact footprint is a varying capacitance with different AC and DC conditions. Under static conditions (such as simple power rails) such variance can be compensated for with larger values; however in closed loop control systems these can cause dynamic elements in otherwise static circuits resulting in varying phase margins and in turn circuit instability. Published datasheet parameters [18] vary from package to package and manufacturer to manufacturer.

Multilayer ceramic capacitors can be divided into 2 categories:

- Class 1 capacitors (e.g. COG) which are typically *Calcium Zirconate* and;

- Class 2/3 (e.g. XR5/XR7) which are typically Barium Titanite.

The class dictates an overall stability rating with DC voltage, frequency, and temperature.

A concern in this compact high voltage design, as highlighted in chapter 3.1, is the number of capacitors required for either Dickinson charge pump or Cockcroft Walton circuits in order to achieve maximum functionality.

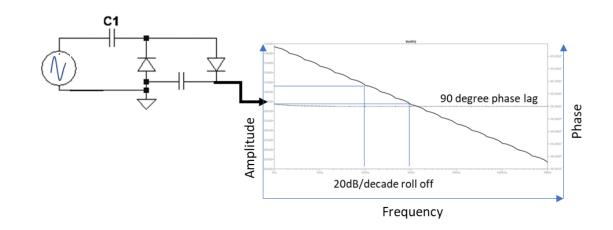

Figure 4.1: Maxims study of MLCCs for power supply decoupling [19]

Figure 4.1 and accompanying paper [19] highlight the variation of capacitance with DC bias of various decoupling capacitors' low voltage applications. As higher voltage capacitors require more dielectric material, they typically have fewer layers stacked in a larger package so have different characteristics.

#### 4.2 Measured results

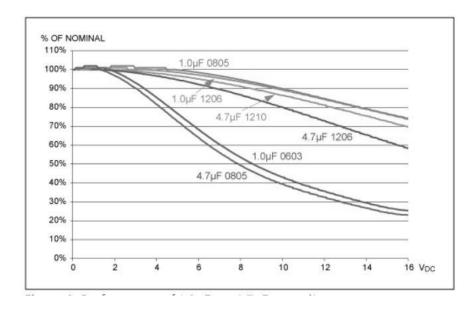

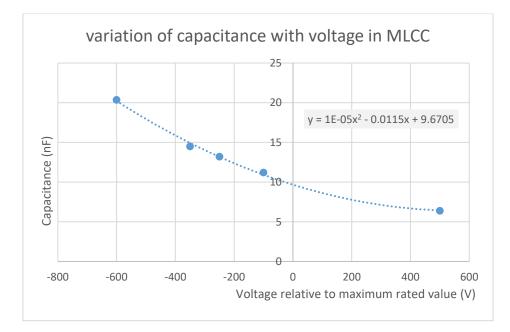

A non-taper multiplier is assumed, as the inaccuracies of a non-uniform taper would be too complex to draw conclusions from. A 22nF 600V rated XR7 1206 capacitor was chosen as a typical example for testing. Capacitance was measured by applying a DC bias across the capacitive element of a low pass filter.

Figures 4.2 and 4.3 show the results of bench testing using a test jig. For static voltage parts, such as supply decoupling capacitors the actual value can be obtained from this curve and the published (1V) value adjusted accordingly to achieve the correct capacitance under bias. Excel is used to estimate the best curve fit. A fourfold change in capacitance is observed with a variation of just under 1200v in the DC voltage

Figure 4.2: Capacitance variation of a 1206 22nF 600v capacitor with voltage.

Figure 4.3: Capacitance variation of a 1206 22nF 600v capacitor adjusted for voltage rating of capacitor

## 4.3 Implications for multiplier circuits

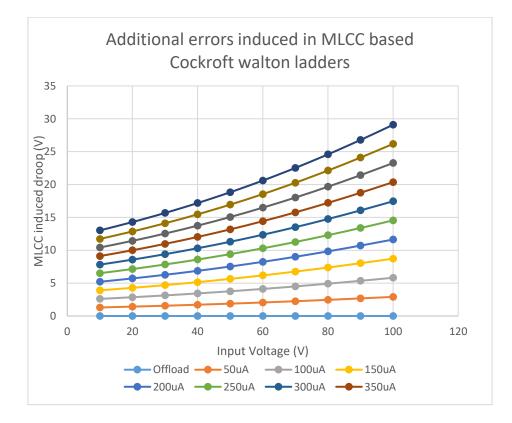

The 50% variation in capacitance (up to its 600V rated maximum voltage) shown in the above plots must be taken into consideration when designing for dynamic operation of the voltage multiplier in a closed loop control system. In a system with ideal capacitors and fixed frequency, droop of the multiplier is proportional to current, so during the increased current of a radiation event the voltage drops and the driving source is increased to compensate. During this period if capacitance temporarily drops then there is potential for instability. Figure 4.4 shows a 10-stage ladder with the additional error induced by MLCC (over ideal capacitors) to quantify this variance.

The magnitude of the deviation only reached a maximum of 30V on a 1000V supply, or 3% assuming C9 and C10 22nf tapering down to 220nf for C1 and C2. This is for a 500uA load which is more that would be expected to be drawn by a scintillation PMT circuit. A potential compromise for the design phase will be making the capacitors sufficiently large for this error not to cause instabilities in a closed loop system whilst not making so large as to cause issues with system phase margin.

Figure 4.4: Additional droop across a 10-stage ladder

## 4.4 Implications for signal circuits

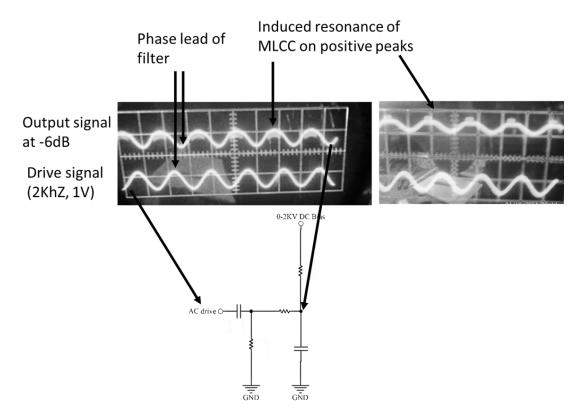

#### *Figure 4.5: Ringing within a DC biased capacitor (highlight filter and DC blocking capacitor)*

Although not the subject of the study, figure 4.5 demonstrates an artefact observed whilst conducting the investigation into DC capacitance variation. Unusually it shows a compression of the positive peak along with a ringing in this region when stimulated under sinusoidal and DC conditions simultaneously.

The conditions found to produce this were full voltage (600V across a 600V capacitor) with a 5Vp-p at 2KHz. The lower trace shows the signal directly from the signal generator. Barium Titanite as used in this XR7 capacitor is used for Piezo electric transducers, so this is hypothesized to be an electro mechanical artefact.

If further investigation is to be carried out this effect would need to be replicated on various packages and capacitor values using a spectrum analyser to characterise the relationship between these harmonics and the trigger conditions.

# 5 Air breakdown in High Density Printed Circuit Boards

## 5.1 Breakdown terms

Ordinarily the difference between high voltage and conventional circuit layout is that the track and component spacing are predominantly dictated by the avoidance of air breakdown rather than physical component size.

As the power supply module will include elements of low voltage feedback and signals from a detector, a system was synthesised to predict leakage from tangible data to allow the design to be as compact as possible without affecting performance.

The purpose for investigating current design rules is that if power supply sections cannot be reduced in size in proportion to that of the photomultiplier tube, then it will be impractical to use them in personal detector developments.

#### Glossary of terms

\***Dark discharge:** A leakage current that occurs between conductors with a voltage potential across them that fails to ionize the air between them.

\**Glow discharge:* A current between conductors that causes a partial ionization along with a distinctive glow, although current flow is limited.

\**Air breakdown:* When the voltage between a pair of conductors exceeds the insulation of the air (or other dielectric) between them current will flow with an equivalent negative resistance.

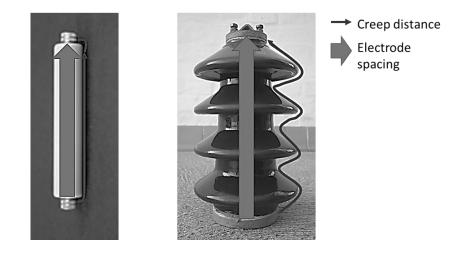

\**Creep:* The surface distance of an electrical path between conductors. This would be given as equivalent distance of a straight line when quoting insulation gaps. Comparison between creep and electrode spacing are shown below in figure 5.1

Figure 5.1: Illustration of creep distance

Although much has been published about breakdown of air between pairs of circular or spherical electrodes, little has been published on the more specific area of discharge between PCB tracks. The effects of complex creep and rectangular profile conductors along with possible surface contaminants suspended in flux from the reflow process cannot be ignored when optimising compact PCBs. Surface mount solder paste must be far richer in flux than traditional solder, which itself is relatively nonconductive but can act as a suspension medium for conductive particles. Although this is largely removed in the washing process, FR4 fibreglass can be sufficiently porous that an element of this remains in the board even with a robust solder mask.

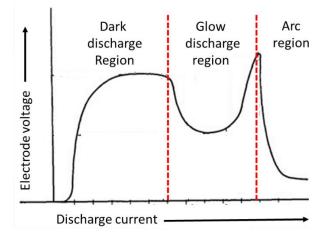

Rule of thumb figures [20] are given as 3000V/mm for full discharge and 1200V/mm for glow discharge; however these are only two points on a non-linear curve. The area of interest for the purposes of this project is dark discharge in relation to leakage from high voltage element to low voltage control systems, efficiency of power consumption, and protection of fragile components.

The scenarios in which these are of concern can be in 2 categories:

- Leakage between a supply rail and ground, causing system efficiency errors.

- Leakage over a single component not connected directly between the power rail and ground which disrupts the operation of the supply.

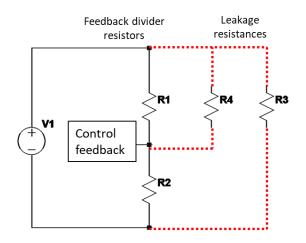

#### Figure 5.2: Leakage resistances across a potential divider network. (R1>>R2)

As illustrated in figure 5.2, R1 and R2 form a potential divider coupling high voltage and low voltage elements of the circuit. Discharge from the high voltage to ground is illustrated by R3 and leakage across a control element by R4. The effect of leakage illustrated by R3 is simply a reduction in power supply efficiency whereas R4 represents a signal error causing signal inaccuracies.

Any gas breakdown should follow a Townsend discharge curve (see figure 5.3) moving from dark discharge to glow discharge to air breakdown. The area for this study will be the dark discharge and low end of the glow discharge region as the intent is to be able to manage these artefacts, as opposed to accurately characterizing the full spectrum.

Figure 5.3: Theoretical Townsend discharge curve [21]

## 5.2 Measurement of voltage breakdown

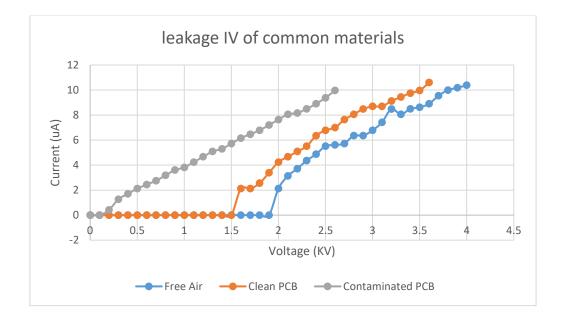

Three circuits were tested for discharge effects: a pair of parallel cylindrical conductors of 1mm diameter in air, a pair of parallel PCB tracks of  $35\mu$ m height and 0.254mm width on an FR4 sheet, and a second pair of PCB tracks coated in solder flux left to dry overnight then the excess wiped off with a lint free cloth. This aimed to separate the effects of air, clean FR4 surface discharge and discharge due to contamination of PCBs. These circuits were set up around a standard 1206 PCB component (based on anticipated critical component choices) footprint then tested for leakage with a variable 20KV supply. Results were taken using an *English Electric* isolation tester (measured 50M $\Omega$  source impedance), *MOD 30KV voltmeter* and a *Vacuum Generators* pico-ammeter. The equipment was selected on availability and did not have an up-to-date calibration. However, they were found to be consistent and gave reliable results when cross checked with other equipment.

Figure 5.4: Measured leakage resistance due to dark discharge in various materials.

Figure 5.4 shows the results of this testing. There is a significant difference between the free air, clean and contaminated PCB behaviour. Before the experimental setup was stripped down the gapping was re-measured with feeler gauges and found to be correct.

## 5.3 Updated design rules

The contaminated PCB demonstrated by far the highest leakage of all the samples tested. This manifested itself as a roughly linear resistance beyond a 200V threshold.

Leakage beyond the 200V threshold is therefore:

$$R_{leakage} = \frac{V}{I_{leakage}}$$

$$= \frac{1000}{4 \times 10^{-3}}$$

$$= 250 \times 10^{6}$$

$$= 250 M\Omega$$

To maintain accurate performance in a system under these conditions the threshold becomes:

$$\frac{200V}{1.5mm} = 133 \left(\frac{V}{mm}\right)$$

And above this threshold a leakage of:

impedance per mm =

$$\frac{measure impedance - source impedance}{distance}$$

$$= \frac{250 \times 10^3 - 50 \times 10^3}{1.5}$$

$$= 133 \frac{M\Omega}{mm}$$

The parallel conductors exhibited a similar performance but with a threshold of 1.8KV and a similar resistance within its leakage region. The normalized threshold becomes:

This does match up with the rule of thumb threshold given for the beginning of glow discharge. As this is the glow discharge region it also indicates that glow discharge was below 200nA, so negligible for most practical purposes.

The IV curve of the clean PCB ostensibly looks like that of the cylindrical conductors, with a lower threshold of:

## 1.5KV/1.5mm=1KV/mm.

The differentiator is that the glow discharge region does not reach its threshold until 1.7KV. There is a slight hump around the threshold which corresponds to the dark discharge region in figure 5.3. The actual mechanism of this is largely immaterial beyond that of curiosity as the single rule of thumb previously has been confirmed with a further two for best- and worst-case real world scenarios.

It is not uncommon for the PCB designer to introduce cut-outs between high and low voltage elements of mixed circuit boards. As machining techniques become more advanced this is now no longer limited to blocks of circuitry and could potentially be used to introduce cut-outs beneath surface mount components. Not only does this potentially reduce residual flux trapped under components not entirely removed by the wash process, but also the previously demonstrated FR4 surface leakage.

The major application for this is surface mount high voltage supply capacitors which give several mm between supply and ground (e.g. 3mm in 1812 package). High value resistors in the order of hundreds of mega ohms or giga ohms (used to isolate high voltage supplies from low voltage control circuits) could also become sources of error under such conditions. For constructing prototypes, the developed discharge coefficients need to be applied to all components used in high voltage circuits as it cannot be assumed dark discharge will be negligible at a component's rated value.

# Table 2: Summary of breakdown behaviour under tested condition. This updated rules of thumb for high voltage PCB design:

| Material         | Threshold (V/mm) | Leakage (MΩ/mm) |

|------------------|------------------|-----------------|

| Bare conductors  | 1200             | 130             |

| Contaminated PCB | 130              | 130             |

| Clean PCB        | 1000             | 130             |

It was observed during these measurements that air breakdown creates varying artefacts in the time domain which could be severely problematic in high performance systems. Characterizing this was beyond the scope and limitations of the equipment for these measurements but could provide further reductions in clearance if accurately documented.

Finally, the effect of adding glass or ceramic inserts through PCB slots over air gapping the PCB alone would be of potential interest. Hamamatsu have included a similar process in recent products in the form of ceramic coatings; however limited information is available at this time

# 6 Preliminary Simulations

## 6.1 Divider simulations

As covered in section 2.2, the purpose of this block of electronics is to develop the individual dynode accelerating voltages from a single main supply. The problematic issue is that the dynodes have increasing current requirements further along the circuit (figure 2.4-2.5). The traditional method for achieving this is to use a long potential divider chain (figure 2.6) with sufficient current flowing through it that any dynamic elements are insignificant. The disadvantage of this approach is that the dynodes still see significant supply impedance whilst the static current will typically be an order of magnitude above the peak dynode current, resulting in poor economy. The problem can be simplified into one of reducing the required offset current of a passive divider whilst maintaining its performance.

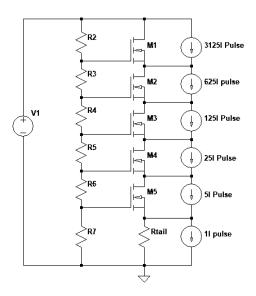

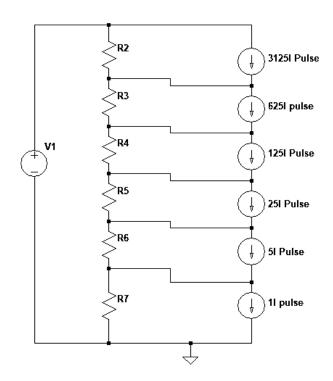

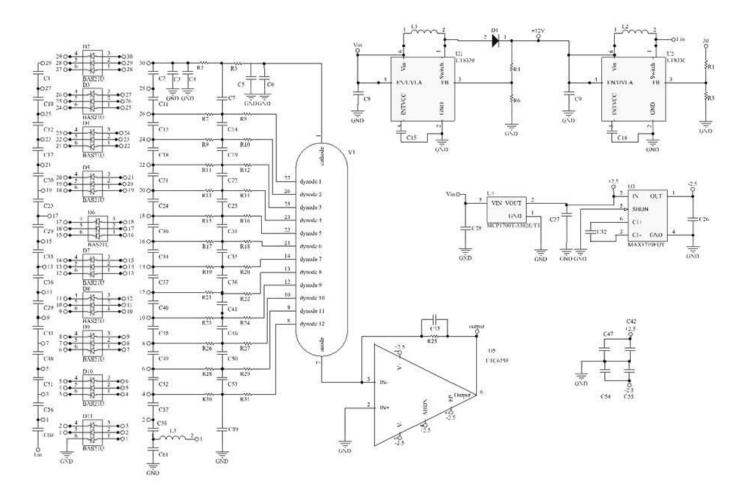

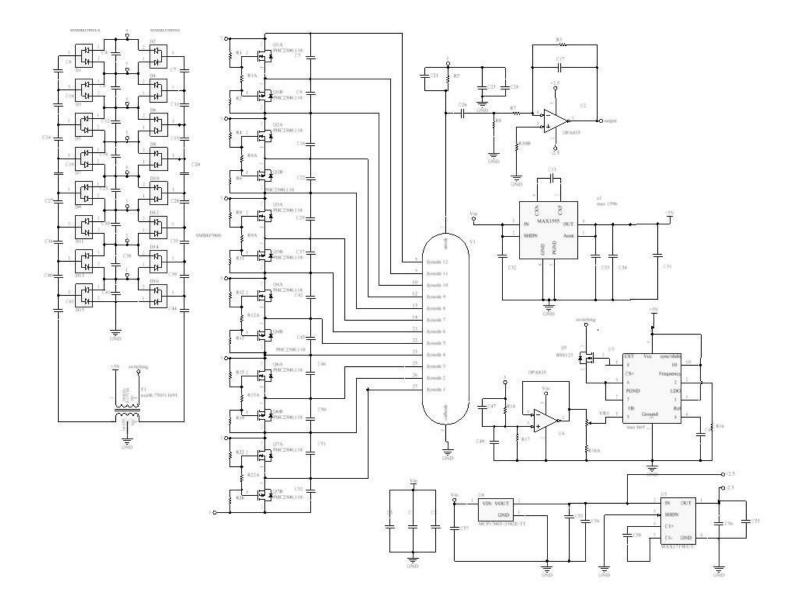

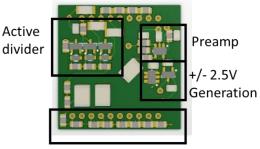

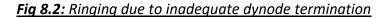

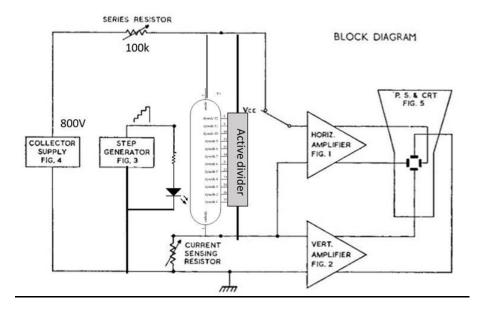

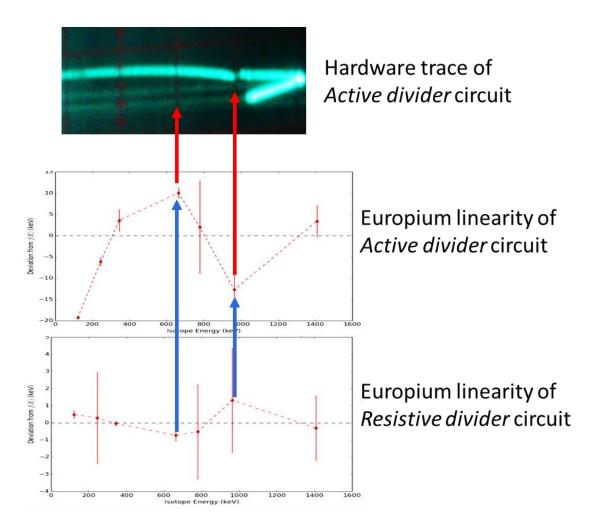

An active divider (figure 6.1), Cockcroft Walton based supply (figure 6.2) and resistive divider (figure 6.3) were all simulated, with 3 variants of each circuit with results shown in table 3. Measurements of droop were taken at all 5 nodes along with the total supply current at quiescent. Figure 6.4 highlights underdamped effects associated with the active divider circuit.

Figure 6.1: Active divider simulation

Figure 6.2: Voltage Multiplier based divider simulation

Figure 6.3: Resistive divider simulation

Figure 6.4: Simulated overshoot related underdamping effects under a capacitive load

(100nF)

| Circuit             | Supply<br>current | Droop1 | Droop2 | Droop3 | Droop4 | Droop5 |

|---------------------|-------------------|--------|--------|--------|--------|--------|

| Resistive1 (R=200K) | 500uA             | 5V     | 5V     | 3.8V   | 2.6V   | 1.3V   |

| Resistive2 (R=40K)  | 2.5mA             | 1V     | 1V     | 0.8V   | 0.5V   | 0.25V  |

| Resistive3 (R=8K)   | 12.5mA            | 200mV  | 200mV  | 150mV  | 100mV  | 50mV   |

| CW1 (C1=10p)        | 20uA approx.      | 14V    | 10V    | 6V     | 3V     | 1.2V   |

| CW2 (C1=100p)       | 20uA approx.      | 600mV  | 800mV  | 600mV  | 300mV  | 130mV  |

| CW3(C1=1n)          | 20uA approx.      | 140mV  | 90mV   | 55mV   | 32mV   | 12mV   |

| Active 1            | 15uA              | 1V     | 300mV  | 50mV   | 13mV   | 1.8V   |

| (Rtail=10M)         |                   |        |        |        |        |        |

| Active 2            | 25uA              | 1V     | 200mV  | 50mV   | 10mV   | 1mV    |

| (Rtail=5 M)         |                   |        |        |        |        |        |

| Active 3            | 102uA             | 500mV  | 180mV  | 20mV   | 3mV    | 0.9mV  |

| (Rtail=2 M)         |                   |        |        |        |        |        |

#### Table 3: Comparison table of divider methods (600V supply)

#### 6.2 Hardware confirmation

In order to quantify the variables discussed above and verify the simulations conceptually, a basic circuit was constructed to test the most severe effects introduced under high rate conditions.

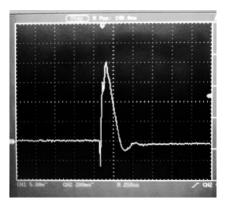

In order to create conditions for this, a 500mm\*100mm\*50mm caesium iodide (doped with Thallium) scintillator coupled to an *Electron Tubes* PMT [22] was used. This was used in conjunction with a Multi-Channel Analyser (MCA) capable of 100,000 counts per second (CPS). The circuit was powered with a lab-type high voltage power supply coupled to a fully active dynode chain and AC coupled to the MCA. The chain was set up using Infineon BSS127 N-channel Mosfets biased to 26uA quiescent current (drain), 8uA reference current (bias divider) with 330nF bypass capacitors across each cascode stage. The intent was to replicate both the droop and ringing (figure 6.4 and table 2) and quantify the effect on a full detector system.

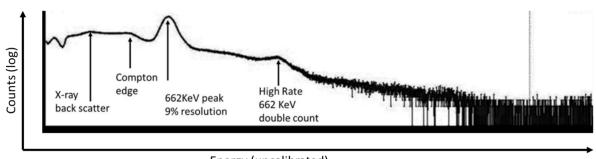

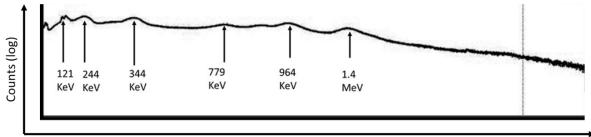

Energy (uncalibrated)

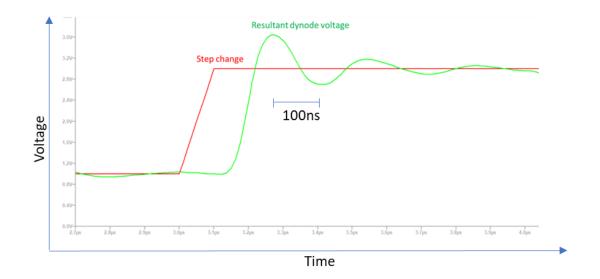

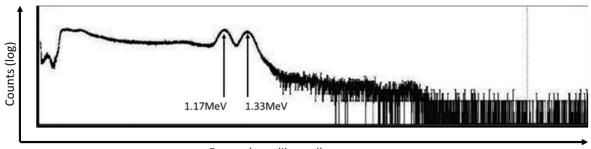

## Figure 6.5: Cobalt-60 spectrum taken on proof of concept jig

Figure 6.5 shows a Cobalt-60 spectrum at 13,000 CPS. It retains its distinctive twin peak emission with a little less separation than would be optimal.

Energy (uncalibrated)

## Figure 6.6: Caesium-137 spectrum taken on proof of concept jig

Figure 6.6 shows a Caesium 137 spectrum maintaining both its peak and Compton edge at 45,000CPS. Resolution is around 9%. This scintillator/MCA combination should be capable of below 8% but this is still acceptable at this very high rate with no baseline restoration.

Energy (uncalibrated)

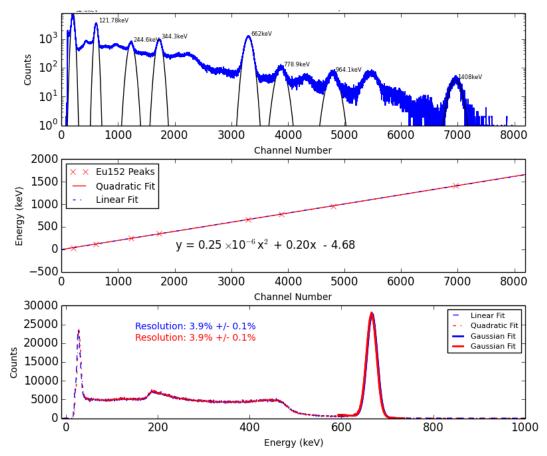

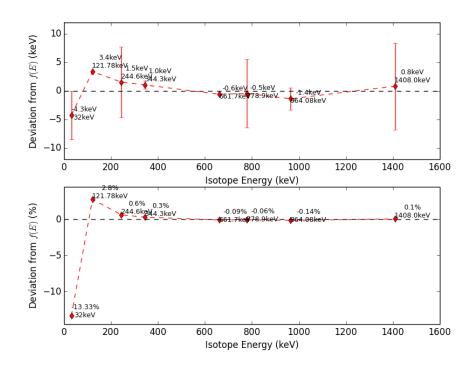

## Figure 6.7: EU152 spectrum taken on proof of concept jig

Figure 6.7 shows a europium-152 spectrum at 80,000CPS. At this very high rate the spectrum has lost most of its energy information; however peaks are still in existence and very close to the correct position.

Although this was a very brief test, it was intended to ascertain whether peak broadening or peak movement would be more of an issue for the dynode circuitry. It demonstrated that peaks maintained correct positioning at far higher count rates than a hand-held detector would be likely to experience or would be expected to accurately record, and peak broadening would be the issue to hinder the design process.

## 6.3 Critical component evaluation: MOSFETS

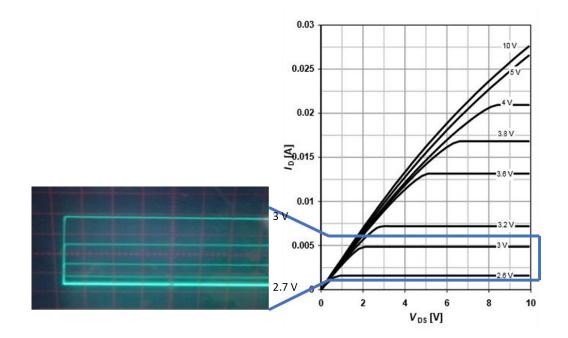

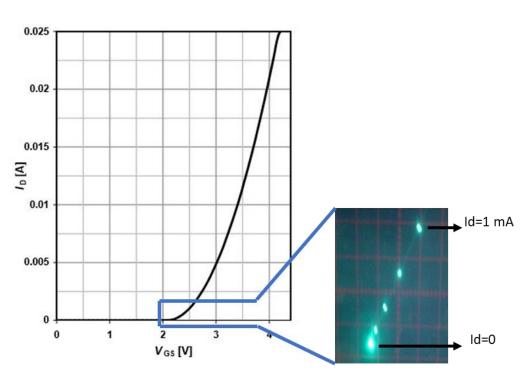

To further understand the underdamped nature of the active divider (figure 6.4) and understand the resolution/peak broadening problem with the circuit, the MOSFETs were measure within the cut off region:

Figure 6.8: Infineon BSS127(VT=2V published) MOSFET transition

region transfer curve [23]

Figure 6.9: BSS127 linearity [23]

In reference to figures 6.8- 6.9 we see the cut-off transition region of the BSS127 Mosfet used for initial testing. This is not shown in any detail in the datasheet but is critical for the dynode systems speed as the feedback system will compensate more quickly in the MOSFETS linear region.

# 7 Design

#### 7.1 High voltage DC-DC converter concept build

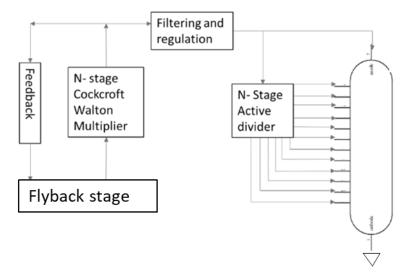

In designing the electronics for a project of this nature at a modular level the order of design can be as important as the design itself. The decision was made to build a supply capable of powering an existing dynode/PMT circuit (used for simulation proving in section 6.2), then design a suitable alternative dynode circuit. Once this was completed the power module was to be refined based on updated dynode circuit requirements. This also served as the base for the voltage multiplier-based divider circuits.

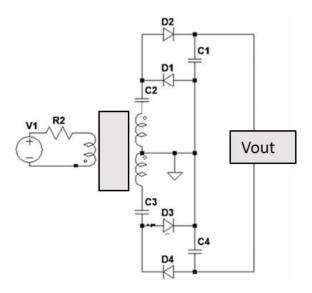

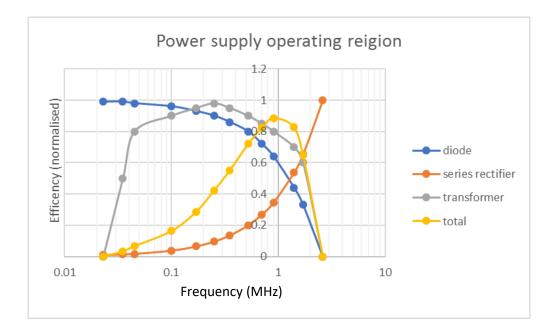

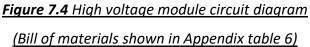

From the review in section 3 a flyback supply driving a Cockcroft Walton ladder was specified for the basis of the power supply board. Although this is a simple, relatively compact concept the trade-off is the choice of switching frequency as it will be common to both elements. Figure 7.1 illustrates the principle via a block diagram.

Figure 7.1: Basic block diagram of circuit

High ratio transformers tend to have higher intrinsic capacitance, so have reduced high frequency response. Analysis of available parts found many flyback transformers designed for space conscious circuits have severe attenuation when switching at an ideal frequency for the primary inductance. This caused a large offset current due to forced discontinuous mode operation.

When the subsequent Cockcroft Walton ladder is considered there are also trade-offs with selection of switching frequency. The capacitor droop is reduced at higher frequency; however recovery time losses in the diodes become more significant at higher frequencies.

This does raise the difficult decision amongst all the potential compromises of where to start the design process. This was done based on component availability; in this instance the most limited was the flyback transformer. The losses for the transformer and switching diodes were measured and overlaid with an ideal (lossless) voltage multiplier. These are shown in figure 7.2.

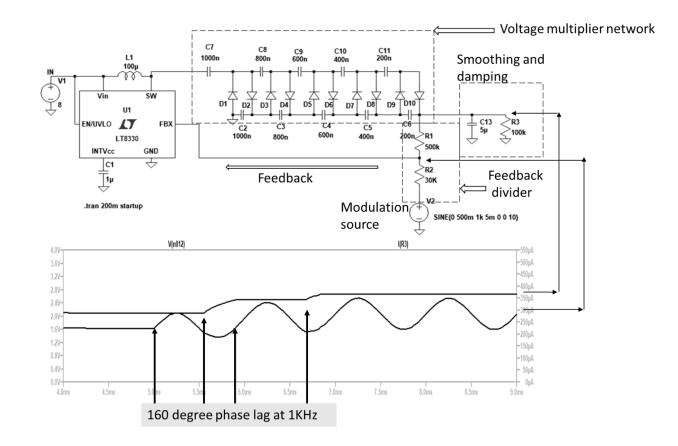

#### Figure 7.2: Overlaid efficiencies of all 3 power supply components.

When using a commercially available monolithic switching amplifier for reduced footprint, cost, or supply offset current, a drawback is that there is often little provision for adjustment of phase margin or time constants of the system, so external components need to be designed accordingly. The system shown in figure 7.3 was used when evaluating prospective components for suitability. It functions by modulating the feedback at a threshold just surpassing the hysteresis of the internal comparator and measuring the superimposed modulation of the output rail. This was found to be most successful with a modulation frequency a decade below the amplifier's switching frequency. The phase lag can then be calculated by viewing both waveforms on an oscilloscope. This also serves to measure the hysteresis level of the amplifier, as this will dictate the accuracy of the final system. This single point measurement does assume a simple phase margin, dictated predominantly by a single circuit element and should be developed further to be of swept frequency if results are found to be inadequate.

#### Figure 7.3: Simulated phase lag technique diagram

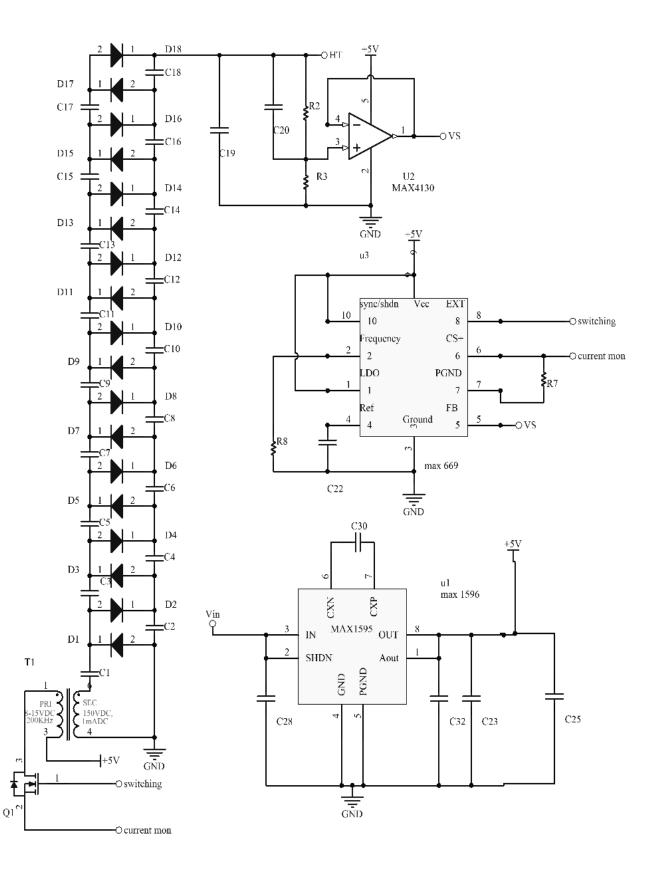

As previously stated, the starting point for the design was the switching transformer since the least flexibility was available from off the shelf parts. After measurement of available items, the *Wurth 750311691* transformer was selected based on physical volume, power rating and primary inductance. The primary inductance of 80uH, with a 1:5 ratio (2mH secondary) with low leakage (1 $\mu$ H peak quoted, 0.1 $\mu$ H measured) demonstrated advantage over other devices of this form factor. It was quoted as maintaining its inductance to 90% on a 1mA secondary draw which was confirmed on test and provided a comfortable amount of headroom for the supply. The secondary was rated to 150V but on testing the point of breakdown was found to be the gap between the pins of the device at 4KV.

Although many suitable switching amplifiers were evaluated the MAX669 [24]was selected based on measurement of hardware. Both this and the LT3757 [25] had the

66

required variable switching frequency and external switch capability whereas the Maxim required around half the current of the LT part for the control circuit (250µA).

It was found that the other differentiator between switching amplifiers was the threshold at which they switched modes; be they burst, pulse skipping or steady PWM. The Maxim was found to have a lower threshold of moving from various power saving modes so was potentially more stable, although it did lack the post input comparator compensation of the *Linear Technologies* equivalent.

When selecting the diodes for the Cockcroft Walton ladder, the requirements were a small form factor due to the number required, and to be robust enough to handle transients and errors during testing. The BAS21-03W [27] switching diode was rated for 250V peak, exceeding the voltage rating of the switching transformer of 250V. Its recovery time of 50ns was adequate for the 250KHz/4µs switching. Its reverse leakage current was 0.1µA (measured) under steady state; however the peak reverse leakage when transitioning between forward and reverse bias was not published.

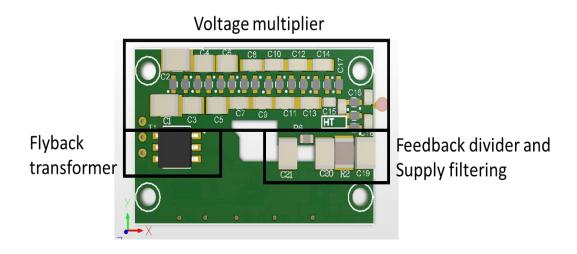

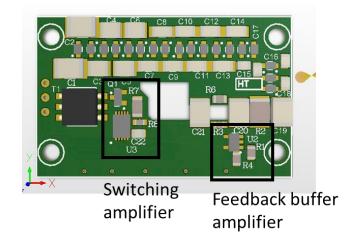

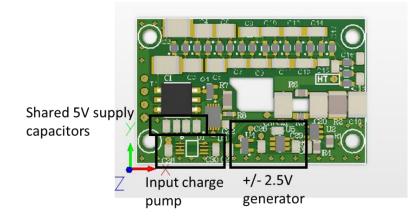

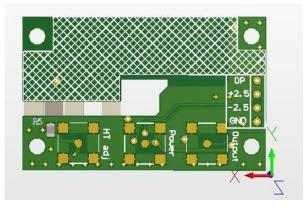

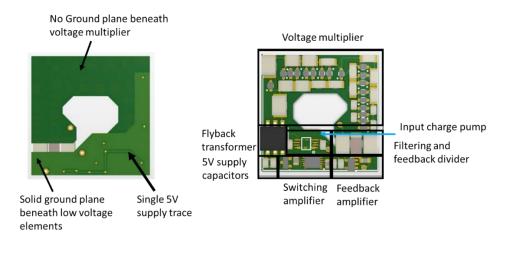

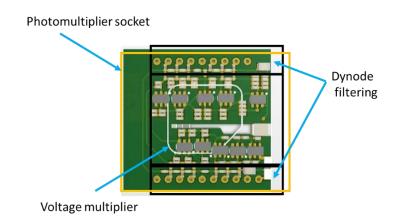

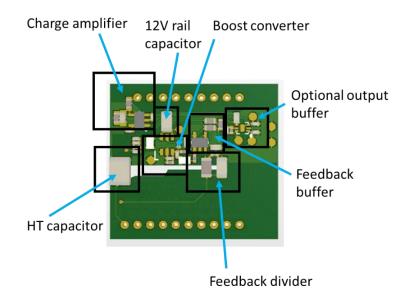

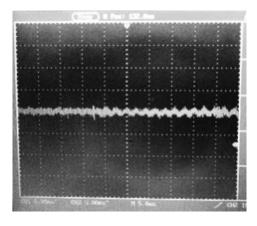

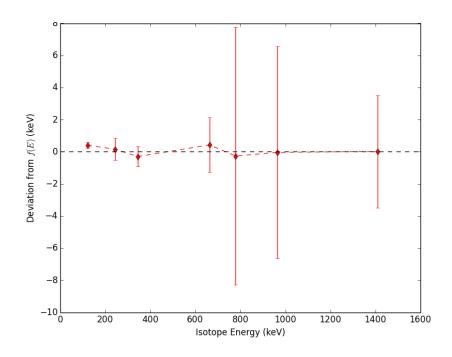

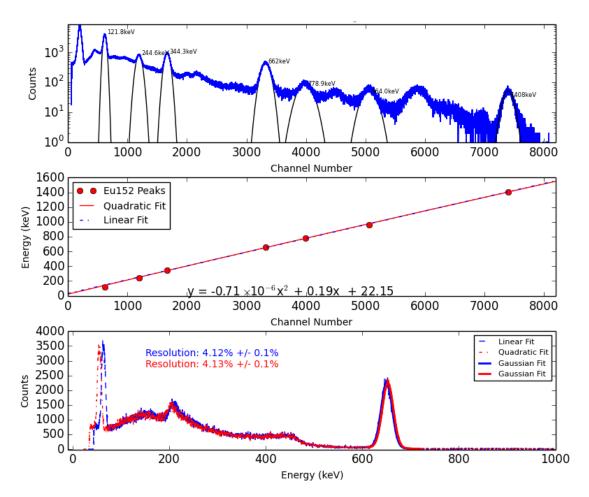

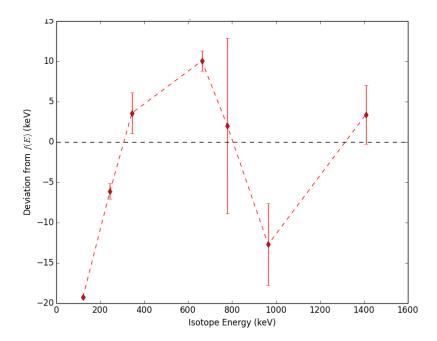

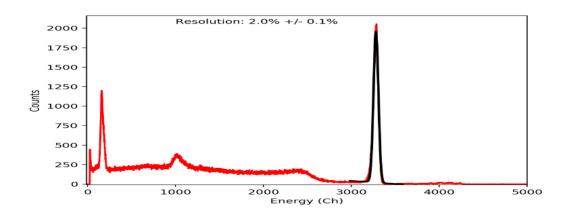

Nine multiplier stages were set as based on preliminary testing based on minimum acceptable recovery time. This number can be mathematically optimised for a simple sinusoidal source [15] but combining these calculations with the efficiency variation of the switching amplifier proved counterproductive. The limit of the supply was found to be 1425V under normal load which maintained diode headroom but exceeded the transformer rating.