### **University of Huddersfield Repository**

Al-Nedawe, Basman M.

Microelectronic Implementation of Dicode PPM System Employing RS Codes

#### **Original Citation**

Al-Nedawe, Basman M. (2014) Microelectronic Implementation of Dicode PPM System Employing RS Codes. Doctoral thesis, University of Huddersfield.

This version is available at http://eprints.hud.ac.uk/id/eprint/26229/

The University Repository is a digital collection of the research output of the University, available on Open Access. Copyright and Moral Rights for the items on this site are retained by the individual author and/or other copyright owners. Users may access full items free of charge; copies of full text items generally can be reproduced, displayed or performed and given to third parties in any format or medium for personal research or study, educational or not-for-profit purposes without prior permission or charge, provided:

- The authors, title and full bibliographic details is credited in any copy;

- A hyperlink and/or URL is included for the original metadata page; and

- The content is not changed in any way.

For more information, including our policy and submission procedure, please contact the Repository Team at: E.mailbox@hud.ac.uk.

http://eprints.hud.ac.uk/

# MICROELECTRONIC IMPLEMENTATION OF DICODE PPM SYSTEM EMPLOYING RS CODES

## **BASMAN MONTHER AL-NEDAWE**

A thesis submitted to the University of Huddersfield in partial fulfilment of the requirements for the degree of Doctor of Philosophy

The University of Huddersfield

December 2014

#### Copyright statement

The author of this thesis (including any appendices and/or schedules to this thesis) owns any copyright in it (the "Copyright") and s/he has given The University of Huddersfield the right to use such copyright for any administrative, promotional, educational and/or teaching purposes.

Copies of this thesis, either in full or in extracts, may be made only in accordance with the regulations of the University Library. Details of these regulations may be obtained from the Librarian. This page must form part of any such copies made.

The ownership of any patents, designs, trademarks and any and all other intellectual property rights except for the Copyright (the "Intellectual Property Rights") and any reproductions of copyright works, for example graphs and tables ("Reproductions"), which may be described in this thesis, may not be owned by the author and may be owned by third parties. Such Intellectual Property Rights and Reproductions cannot and must not be made available for use without the prior written permission of the owner(s) of the relevant Intellectual Property Rights and/or Reproductions.

### **Abstract**

Optical fibre systems have played a key role in making possible the extraordinary growth in world-wide communications that has occurred in the last 25 years, and are vital in enabling the proliferating use of the Internet. Its high bandwidth capabilities, low attenuation characteristics, low cost, and immunity from the many disturbances that can afflict electrical wires and wireless communication links make it ideal for gigabit transmission and a major building block in the telecommunication infrastructure.

A number of different techniques are used for the transmission of digital information between the transmitter and receiver sides in optical fibre system. One type of coding scheme is Pulse Position Modulation (PPM) in which the location of one pulse during  $2^M$  time slots is used to convey digital information from M bits. Although all the studies refer to advantages of PPM, it comes at a cost of large bandwidth and a complicated implementation. Therefore, variant PPM schemes have been proposed to transmit the data such as: Multiple Pulse Position Modulation (MPPM), Differential Pulse Position Modulation (DPPM), Pulse Interval Modulation (PIM), Digital Pulse Interval Modulation (DPIM), Dual Header Pulse Interval Modulation (DH-PIM), Dicode Pulse Position Modulation (DiPPM).

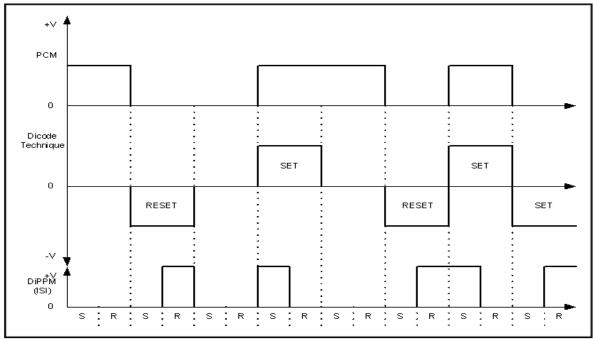

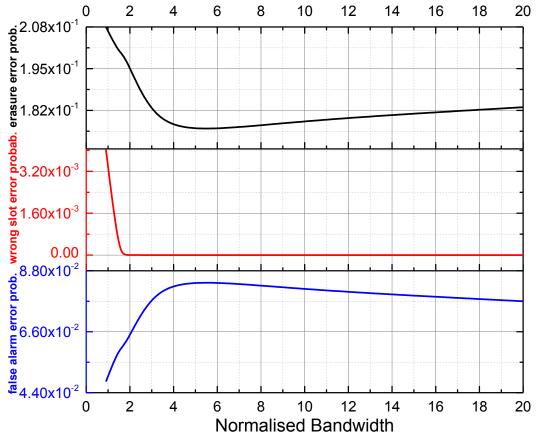

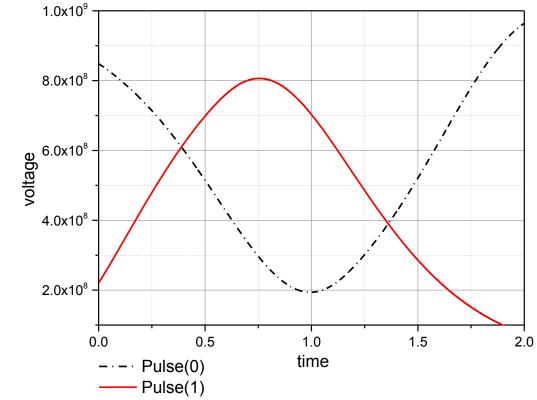

The DiPPM scheme has been considered as a solution for the bandwidth consumption issue that other existing PPM formats suffer from. This is because it has a line rate that is twice that of the original data rate. DiPPM can be efficiently implemented as it employs two slots to transmit one bit of pulse code modulation (PCM). A PCM conversion from logic zero to logic one provides a pulse in slot RESET (R) and from one to zero provides a pulse in slot SET (S). No pulse is transmitted if the PCM data is unvarying. Like other PPM schemes, DiPPM suffers from three types of pulse detection errors wrong slot, false alarm, and erasure.

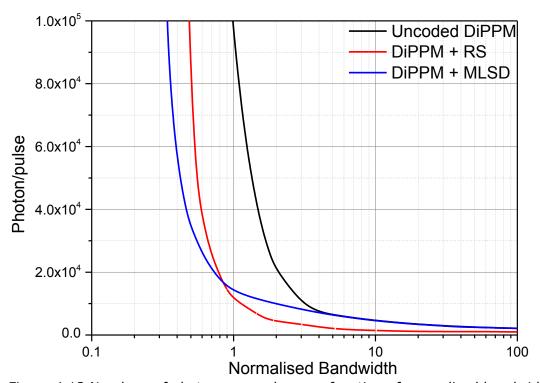

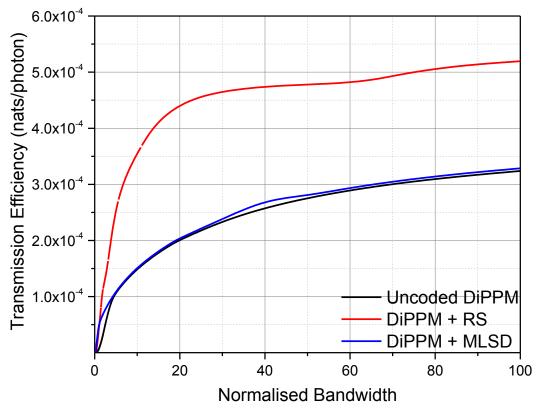

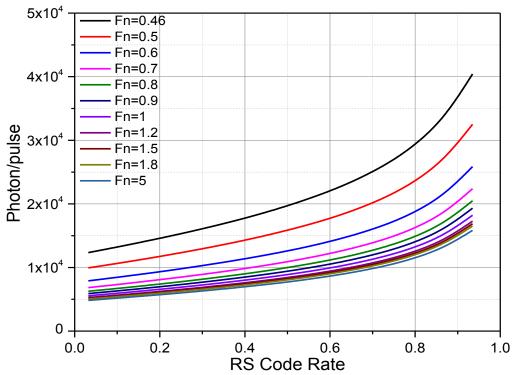

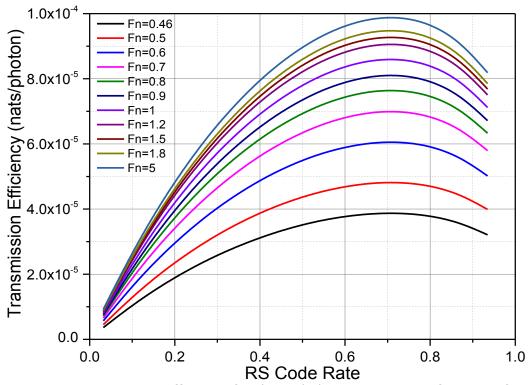

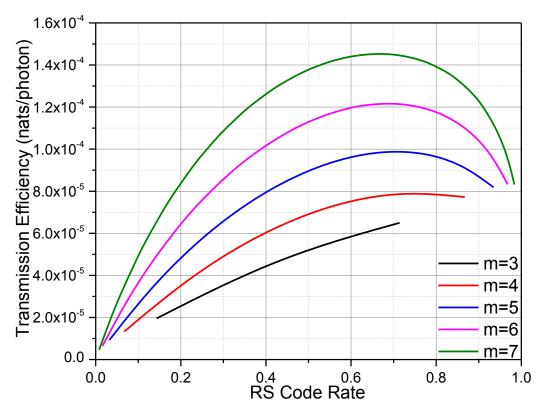

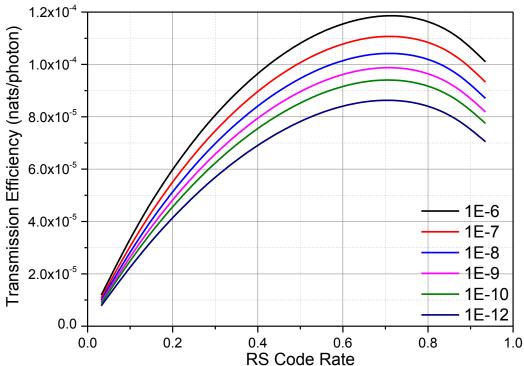

The aim of this work was to build an error correction system, Reed Solomon (RS) code, which would overcome or reduce the error sources in the DiPPM system. An original mathematical program was developed using the Mathcad software to find the optimum RS parameters which can improve the DiPPM system error performance, number of photons and transmission efficiency. The results showed that the DiPPM system employing RS code offered an improvement over uncoded DiPPM of 5.12 dB, when RS operating at the optimum code rate of approximately ¾ and a codeword length of 2<sup>5</sup> symbols.

Moreover, the error performance of the uncoded DiPPM is compared with the DiPPM system employing maximum likelihood sequence detector (MLSD), and RS code in terms

of number of photons per pulse, transmission efficiency, and bandwidth expansion. The DiPPM with RS code offers superior performance compared to the uncoded DiPPM and DiPPM using MLSD, requiring only  $4.5 \times 10^3$  photons per pulse when operating at a bandwidth equal to or above 0.9 times the original data rate.

Further investigation took place on the DiPPM system employing RS code. A Matlab program and very high speed circuit Hardware Description language (VHDL) were developed to simulate the designed communication system. Simulation results were considered and agreed with the previous DiPPM theory. For the first time, this thesis presents the practical implementation for the DiPPM system employing RS code using Field Programmable Gate Array (FPGA).

# Acknowledgements

Praise belongs to God, the Lord of Mercy and the Giver of Mercy, for his blessing that made this work possible and completed.

I would like to take the opportunity to express my sincere gratitude to Dr Martin M J IX Sibley, my supervisor, for his continuous guidance and support throughout the research work and particularly during the writing up stage. His useful critiques and valuable suggestions have always been very much appreciated.

I would also like to thank Dr Peter J Mather, my second supervisor for his assistance with a software program for the research work.

My special thanks and appreciation must go to the Graqi Ministry of Kigher Education and Scientific Research, for awarding me the fee-waiver scholarship to purse this PhD. It would have been difficult for me to pursue a research degree without this great opportunity.

A very special thanks to my family for all their constant support and encouragement that made my research easier.

I can hardly overlook the co-operation, timely help and moral support extended by my friends, colleagues, and university staff. Acknowledgements are inherently endless and incomplete, and I request indulgence from many friendly and helpful people whom I could not name here, due to paucity of space.

# **Contents**

| ABSTRACT                                                                          | III   |

|-----------------------------------------------------------------------------------|-------|

| ACKNOWLEDGEMENTS                                                                  | v     |

| CONTENTS                                                                          | VI    |

| LIST OF FIGURES                                                                   | XI    |

| LIST OF TABLES                                                                    | XVII  |

| LIST OF ABBREVIATIONS                                                             | XVIII |

| CHAPTER1: INTRODUCTION                                                            | 20    |

| 1.1. OPTICAL COMMUNICATIONS                                                       | 20    |

| 1.1.1. Lasers                                                                     | 20    |

| 1.1.2. Optical fibre Transmitter                                                  | 20    |

| 1.1.3. Optical fibre Receiver                                                     | 22    |

| 1.1.4. Optical fibre                                                              | 23    |

| 1.1.5. Principle of dispersion                                                    | 24    |

| 1.1.6. Wave division multiplexing principle                                       | 24    |

| 1.1.7. Coding Schemes                                                             | 25    |

| 1.2. Error Correction                                                             | 25    |

| 1.3. Design Automation                                                            | 26    |

| 1.4. AIMS AND OBJECTIVES                                                          | 27    |

| 1.5. Thesis Layout                                                                | 28    |

| 1.6. ORIGINAL WORK CONTRIBUTIONS                                                  | 29    |

| CHAPTER2: LITERATURE REVIEW                                                       | 31    |

| 2.1. Introduction                                                                 | 31    |

| 2.2. CODING SCHEMES IN OPTICAL FIBRE                                              | 31    |

| 2.2.1. Characteristics of Line Coding                                             | 32    |

| 2.2.2. Rate Adaptive Modulation and Coding for Optical Fibre Transmission Systems | 34    |

| 2.2.3. Pulse Position Modulation                                                  | 36    |

| 2.3. DIPPM CODING SCHEME FOR OPTICAL FIBRE COMMUNICATIONS                         | 37    |

| 2.3.1. Maximum Likelihood Sequence Detector                                       | 39    |

| 2.3.2. Implementation                                                             | 42    |

| 2.3.3. Performance Analysis                                                       | 43    |

| 2.3.4. Suboptimal Filtering in Zero Guard DiPPM                                   | 47    |

| 2.4. PPM EMPLOYING REED SOLOMON CODES                                             | 48    |

| 2.4.1. Reed Solomon Codes                                                         | 49    |

| 2.4.2. Reed Solomon Encoding and Decoding                                         | 52    |

| 2.4.3. Reed Solomon Codes Applications                             | 55                       |

|--------------------------------------------------------------------|--------------------------|

| 2.4.4. Implementation and Performance of Reed Solomon Codes        | 56                       |

| 2.5. FIELD PROGRAMMABLE GATE ARRAY (FPGA)                          | 58                       |

| 2.5.1. VHDL and Applications                                       | 61                       |

| 2.6. Summary                                                       | 64                       |

| CHAPTER3: DICODE PULSE POSITION MODULATION                         | 65                       |

| 3.1. Introduction                                                  | 65                       |

| 3.2. DICODE PULSE POSITION MODULATION: UNDERSTANDING OF THE THEORY | 66                       |

| 3.2.1. DiPPM system optical power                                  | 69                       |

| 3.3. ERRORS AFFECTING DIPPM                                        | 71                       |

| 3.3.1. Wrong-slot Errors                                           | 71                       |

| 3.3.2. Erasure Errors                                              | 72                       |

| 3.3.3. False Alarm Errors                                          | 73                       |

| 3.3.4. DiPPM Error Probabilities                                   |                          |

| 3.4. CODER AND DECODER CIRCUITS FOR THE DIPPM                      | 77                       |

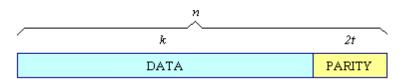

| CHAPTER4: FINDING OPTIMUM PARAMETERS FOR REED SOLOMON CODE W       | ORKING WITH DICODE PULSE |

| POSITION MODULATION SYSTEM                                         | 81                       |

| 4.1. INTRODUCTION                                                  | 81                       |

| 4.2. FORWARD ERROR CORRECTION SYSTEM MODEL                         | 81                       |

| 4.2.1. Slope Detection Approach                                    | 82                       |

| 4.2.2. Central Detection Approach                                  | 83                       |

| 4.2.3. DiPPM Employing RS vs PCM Employing RS                      | 84                       |

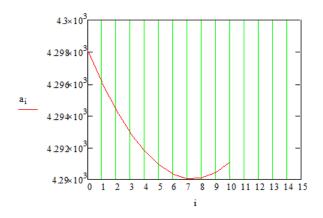

| 4.3. RESULTS                                                       | 86                       |

| 4.3.1. Finding Optimum RS System Parameters                        | 86                       |

| 4.3.2. DiPPM Employing RS vs DiPPM Employing MLSD                  | 92                       |

| 4.3.3. PCM Employing RS                                            | 95                       |

| 4.4. Summary                                                       | 100                      |

| CHAPTER5: MATLAB SIMULATION FOR THE DICODE PULSE POSITION MODUL    | ATION SYSTEM WITH REED   |

| SOLOMON CODE                                                       |                          |

| 5.1. Introduction                                                  | 101                      |

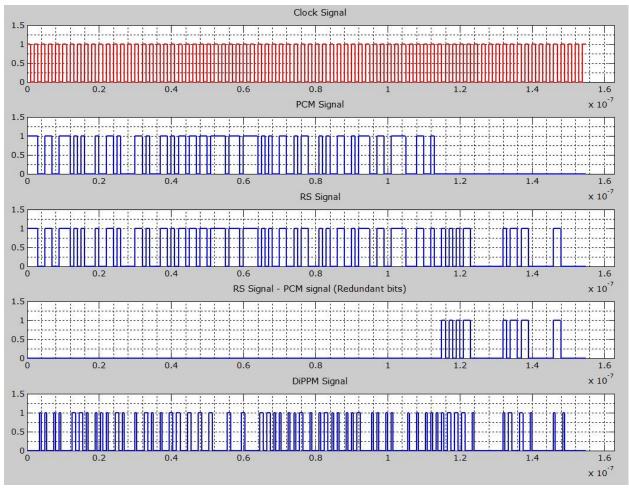

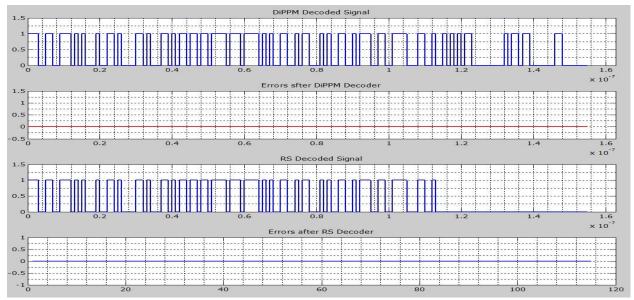

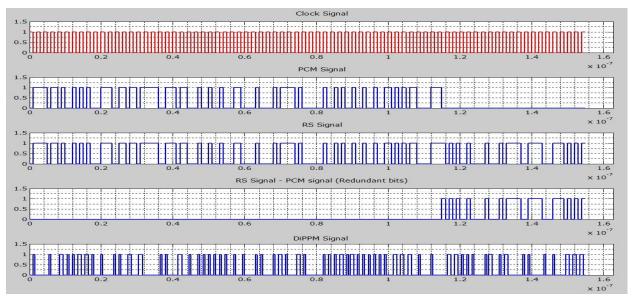

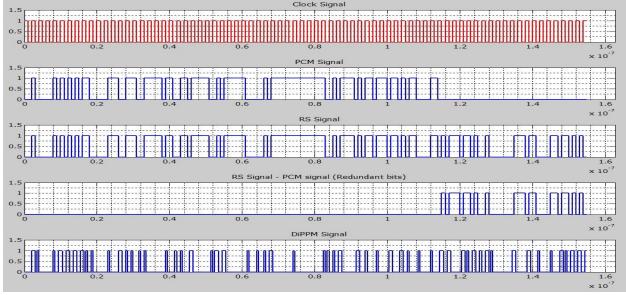

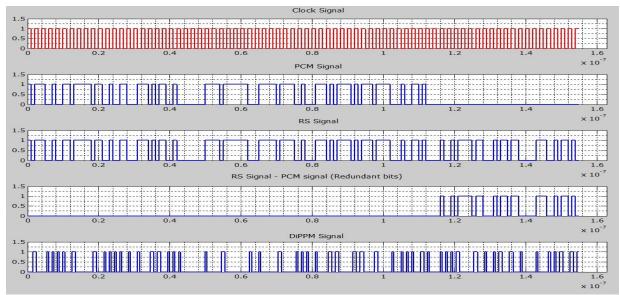

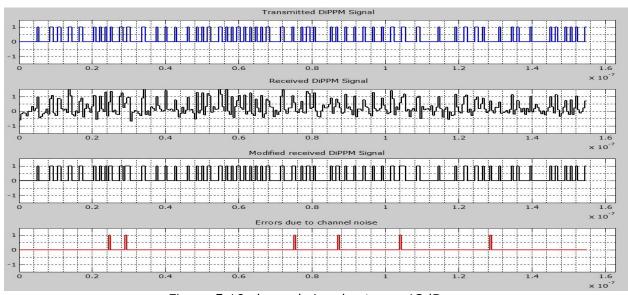

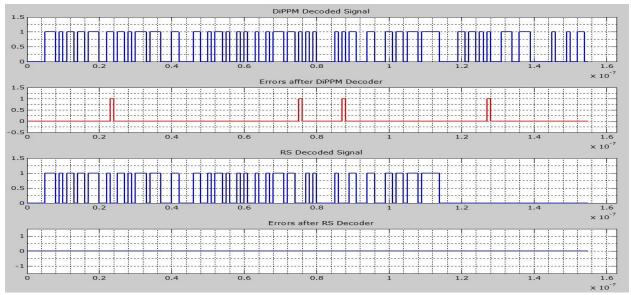

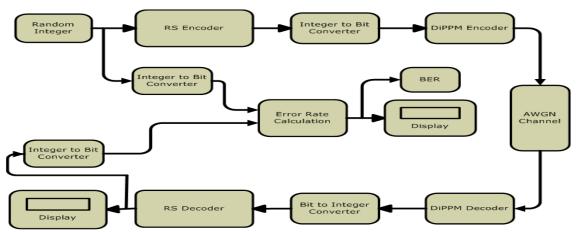

| 5.2. DIPPM SYSTEM SIMULATION                                       | 101                      |

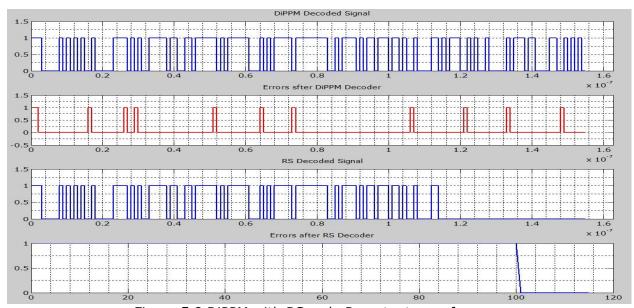

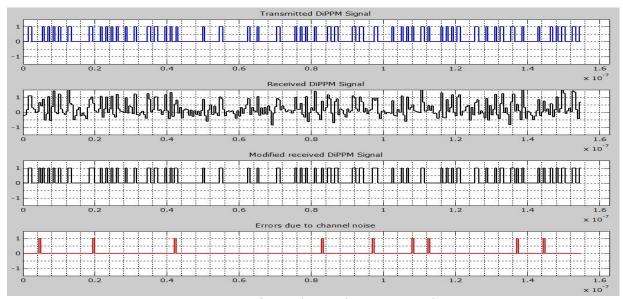

| 5.3. DIPPM WITH RS CODE SYSTEM SIMULATION                          | 103                      |

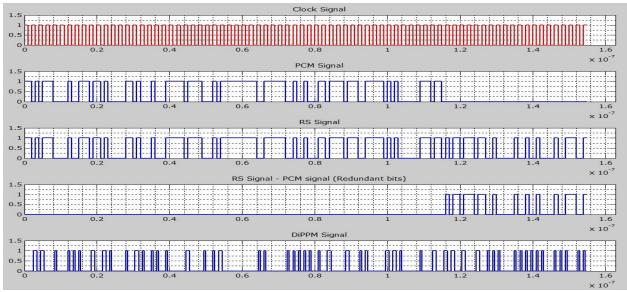

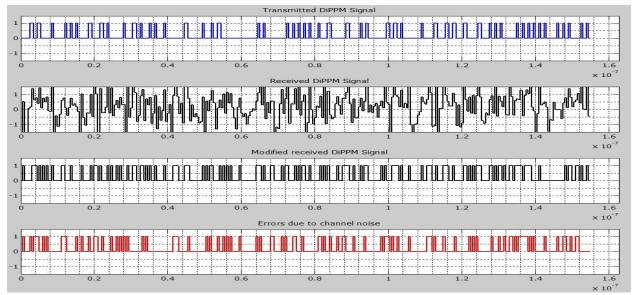

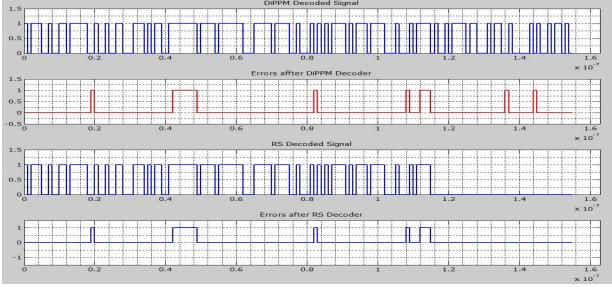

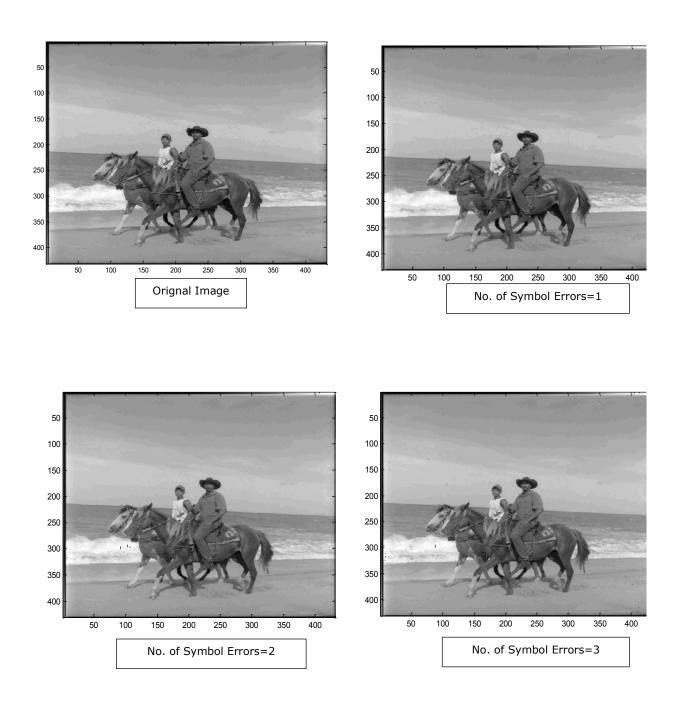

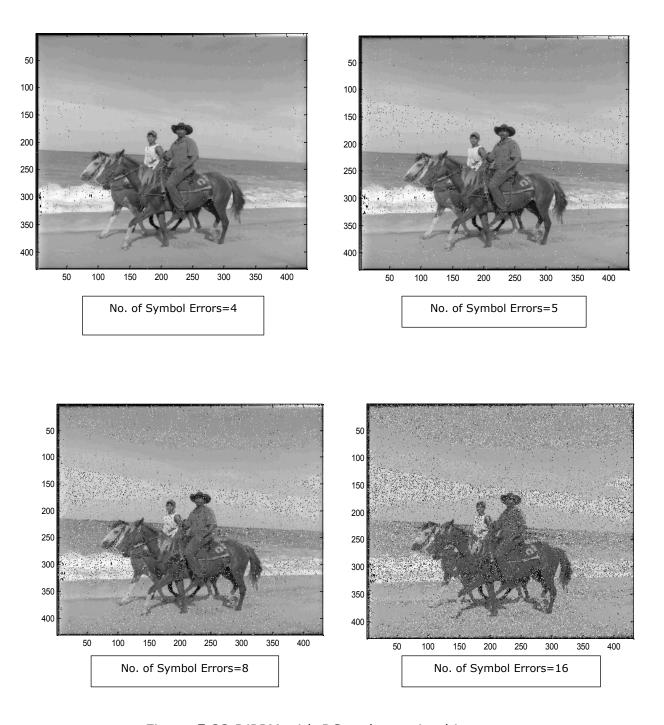

| 5.4. DIPPM WITH RS SYSTEM IN AWGN CHANNEL                          | 108                      |

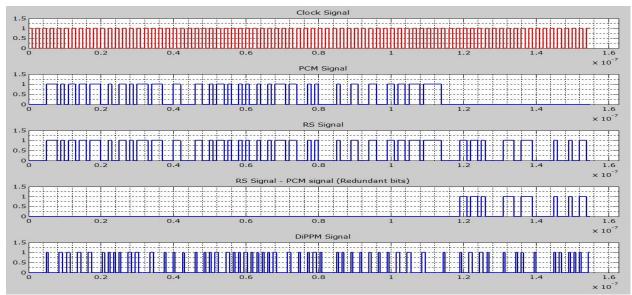

| 5.5. DIPPM WITH RS SYSTEM (UPGRADED VERSION)                       | 113                      |

|                                                                    |                          |

| MODULATION SYSTEM WITH REED SOLOMON CODE                                    |        |

|-----------------------------------------------------------------------------|--------|

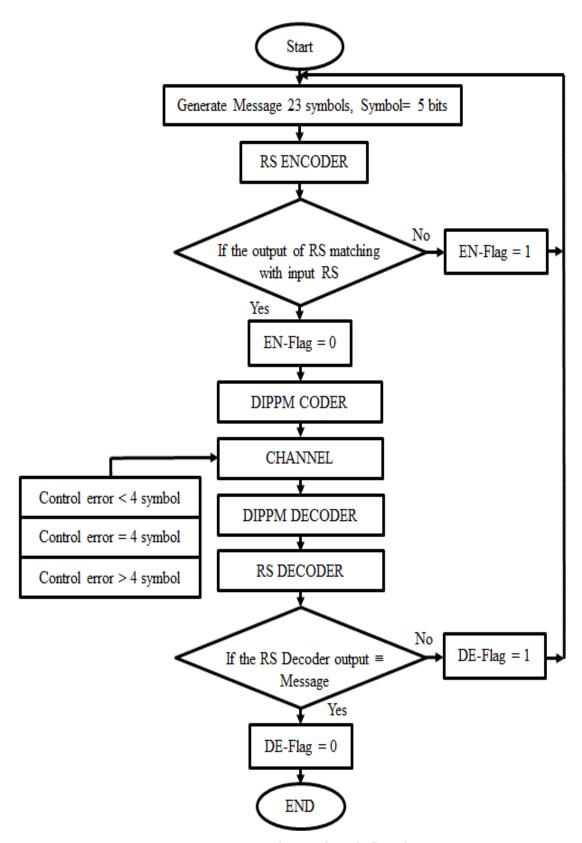

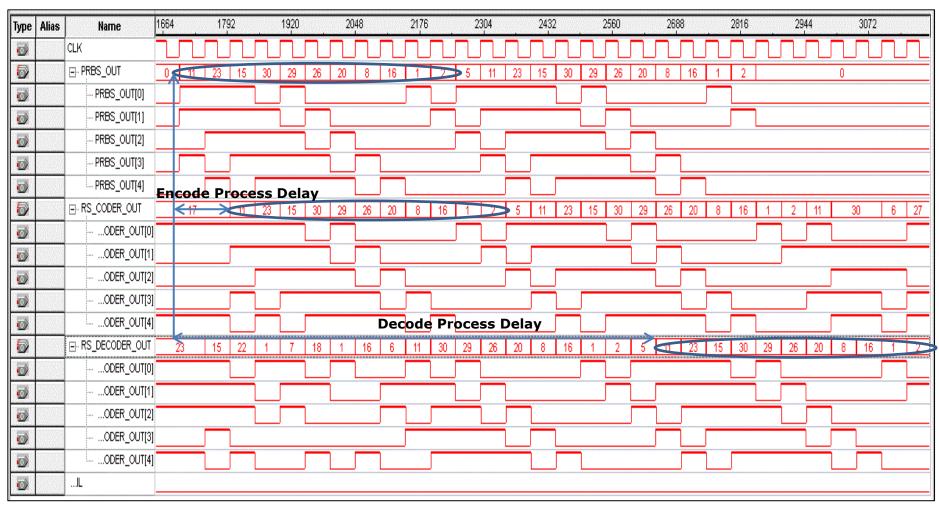

| 6.1. Introduction                                                           | 117    |

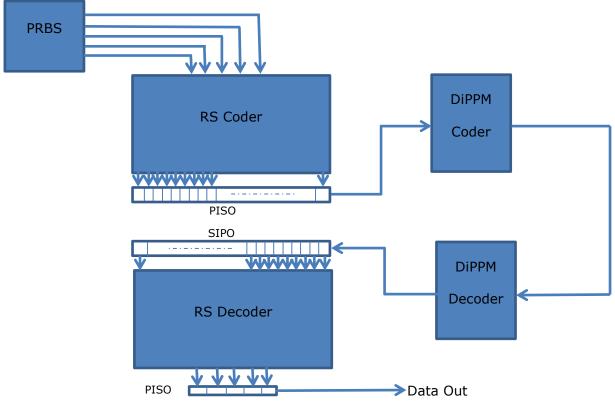

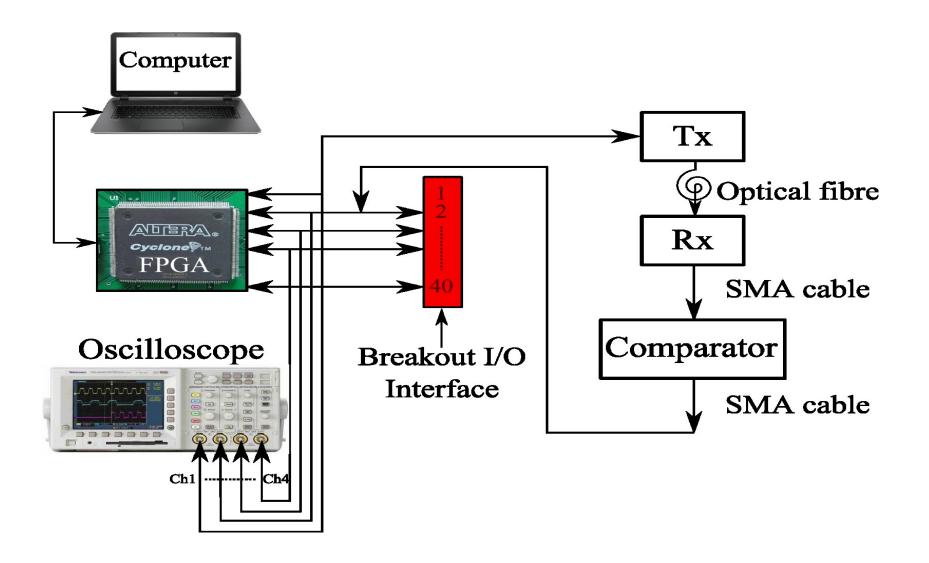

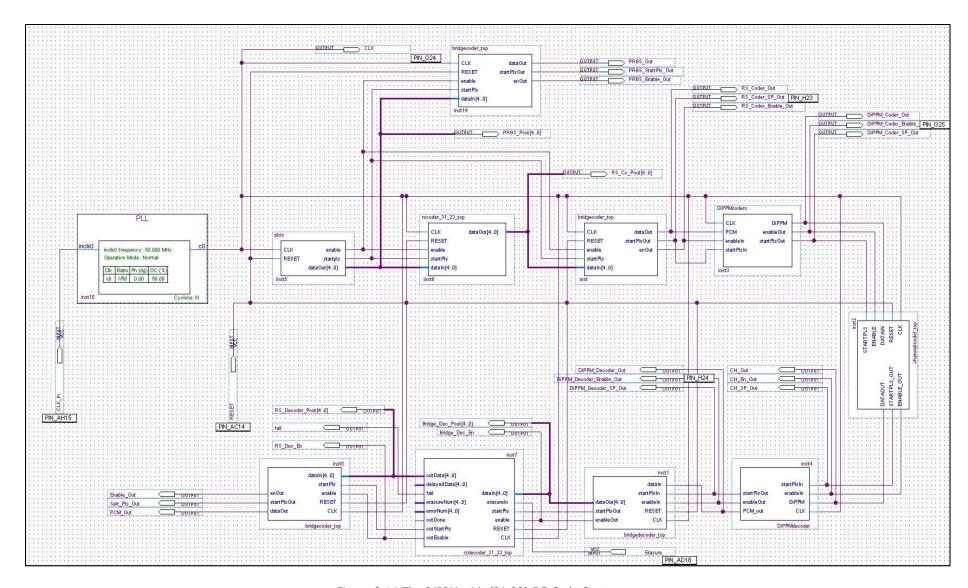

| 6.2. System Schematic                                                       |        |

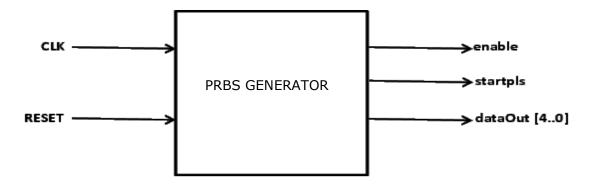

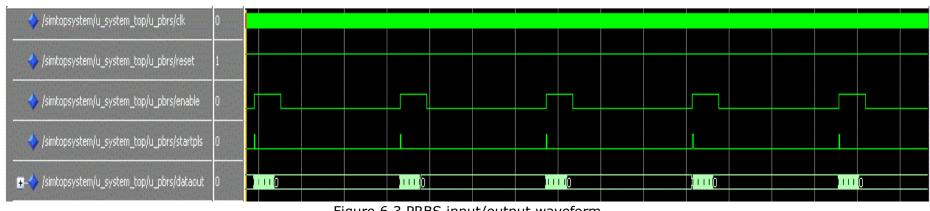

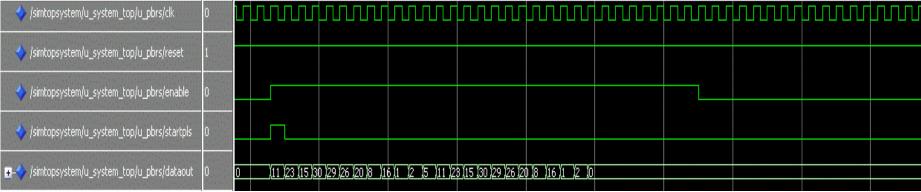

| 6.2.1. Pseudo Random Binary Sequence (PRBS)                                 | 118    |

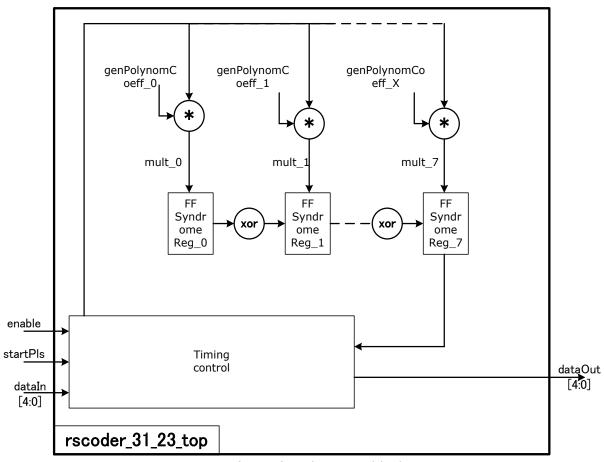

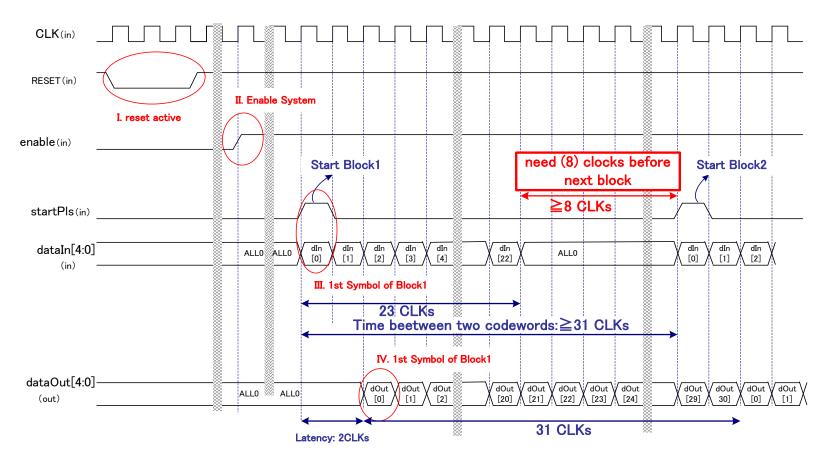

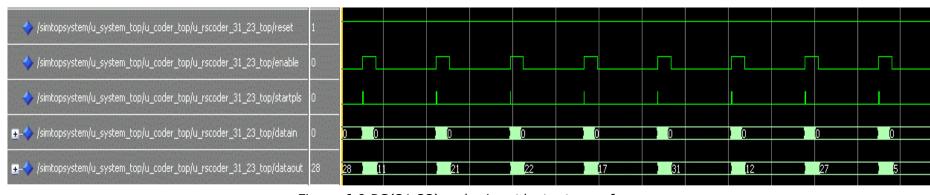

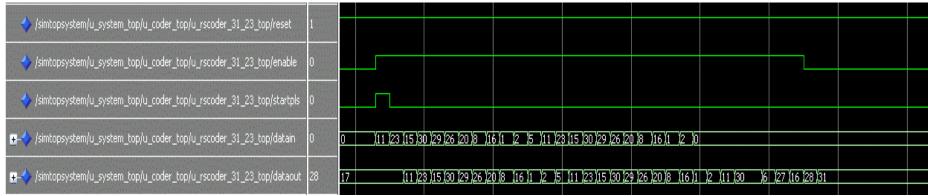

| 6.2.2. Reed Solomon Coder                                                   |        |

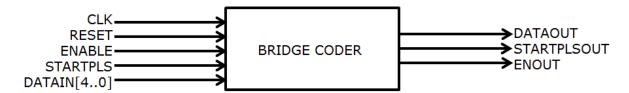

| 6.2.3. Bridge Coder (Parallel Input Serial Output)                          | 127    |

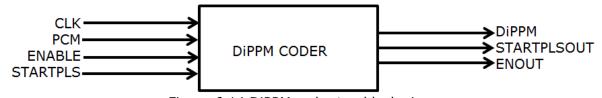

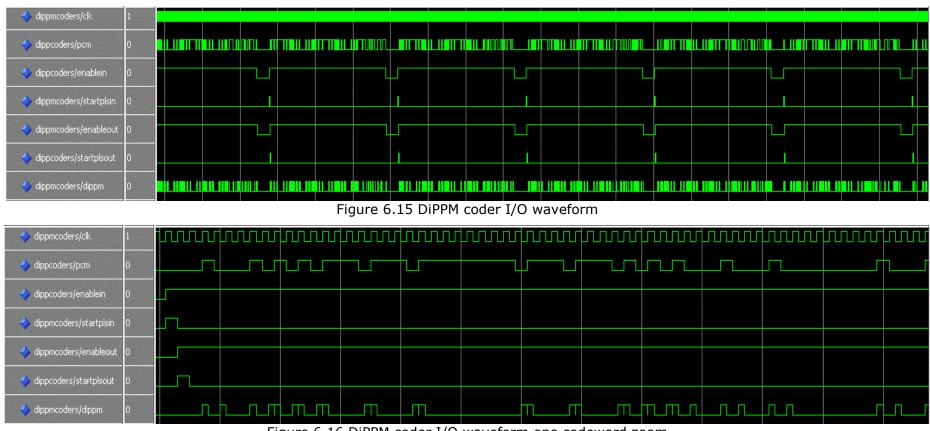

| 6.2.4. DiPPM Coder                                                          |        |

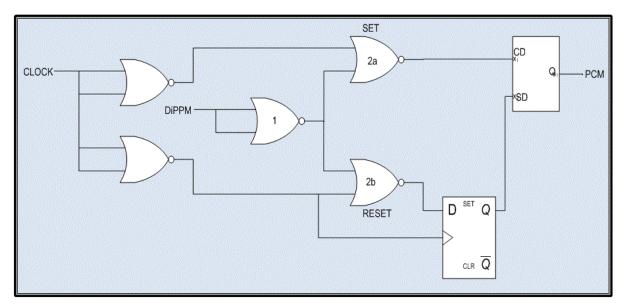

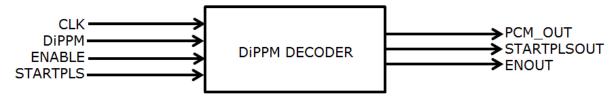

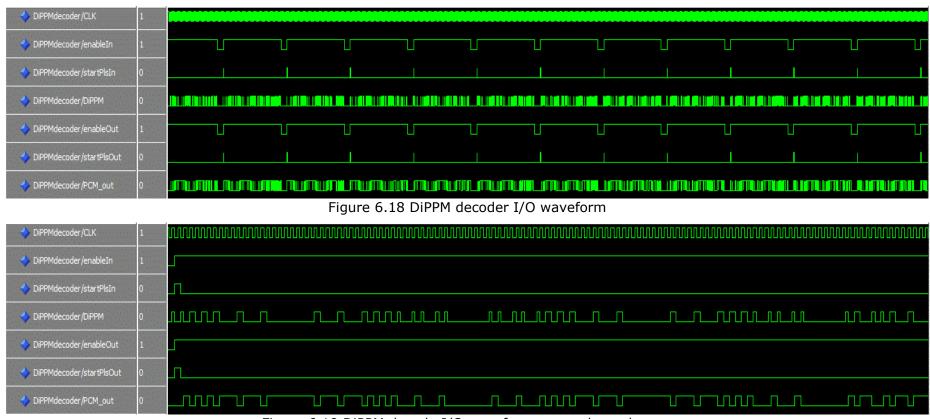

| 6.2.5. DiPPM Decoder                                                        | 131    |

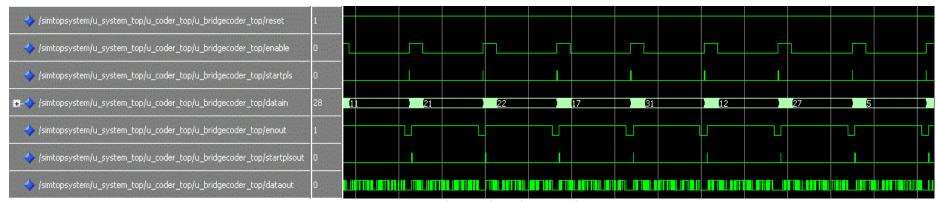

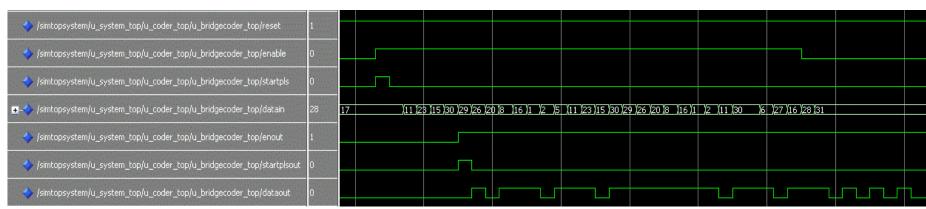

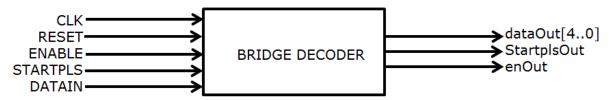

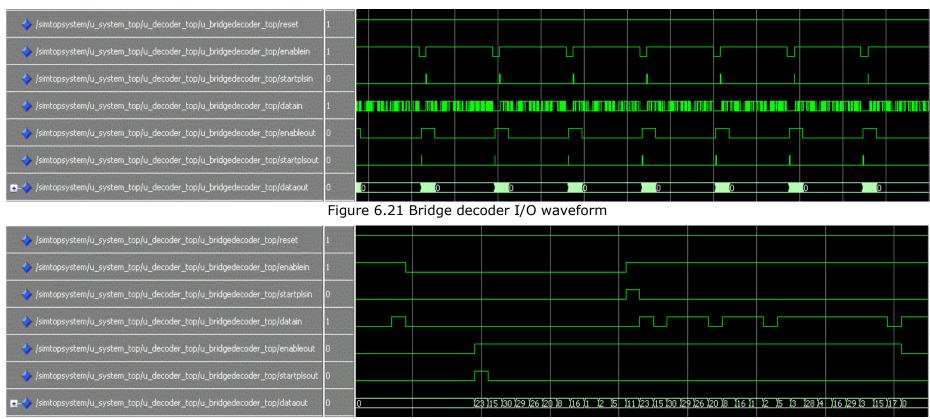

| 6.2.6. Bridge Decoder (Serial Input Parallel Output)                        | 133    |

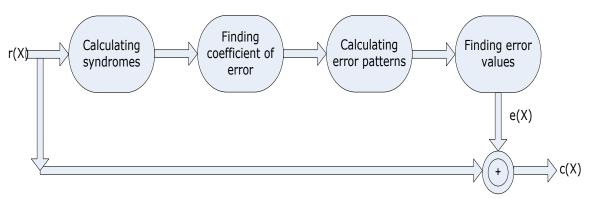

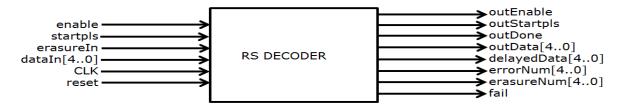

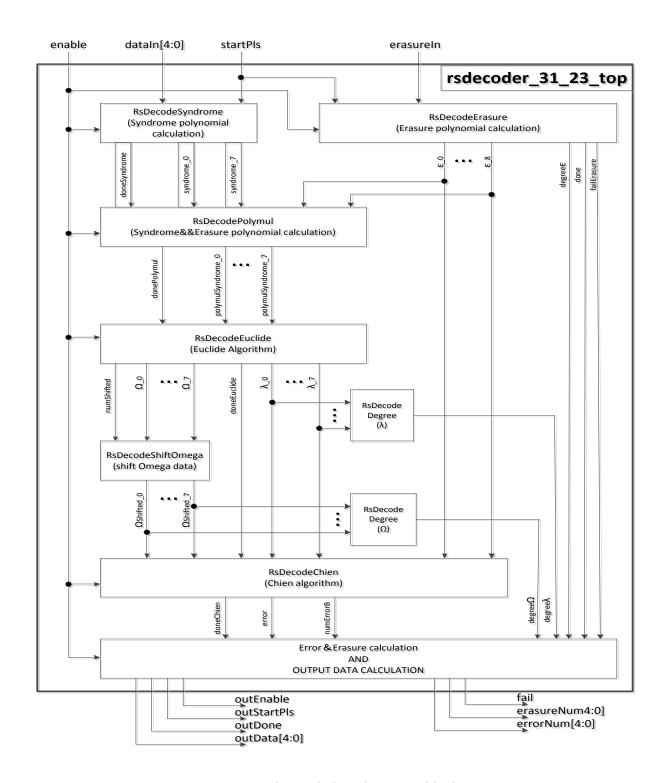

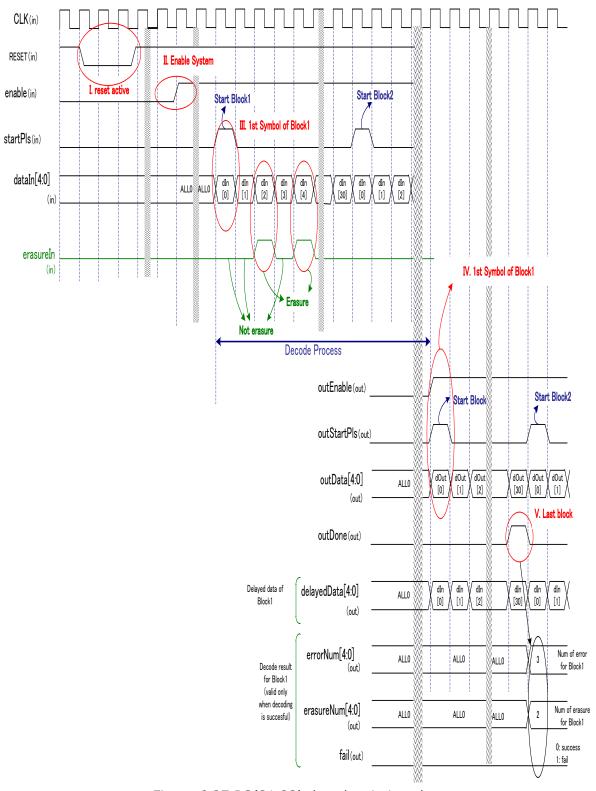

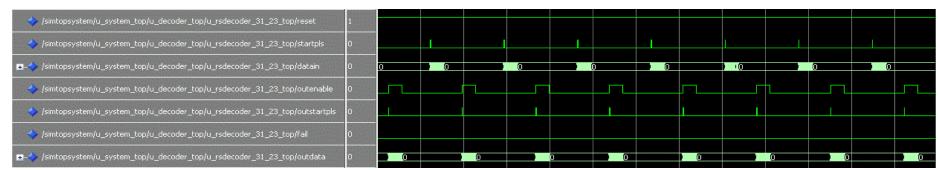

| 6.2.7. Reed Solomon Decoder                                                 | 135    |

| 6.3. SUMMARY                                                                | 141    |

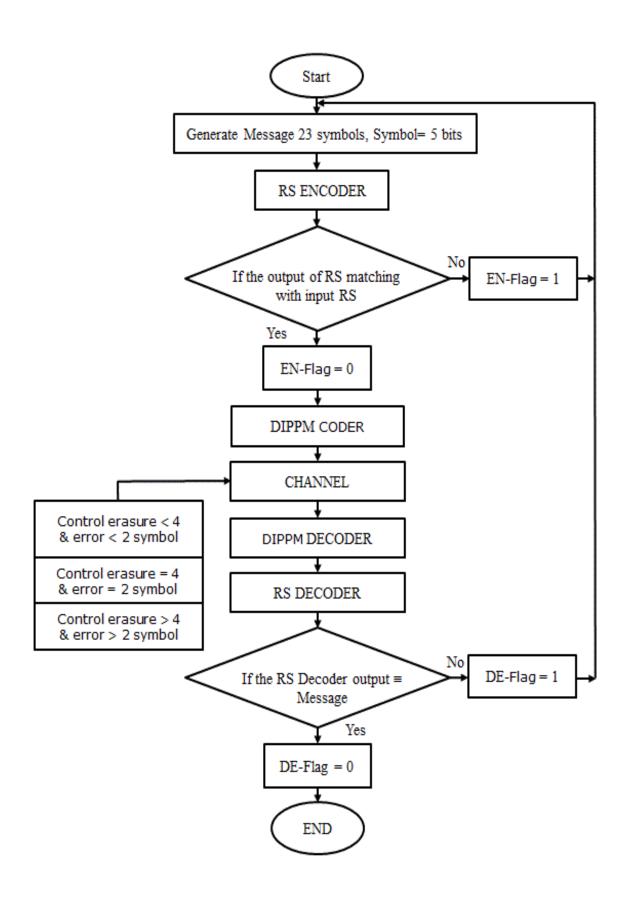

| CHAPTER7: ERASURE AND ERROR SIMULATION ENVIRONMENTS FOR THE DICODE PULSE PO | SITION |

| MODULATION SYSTEM WITH REED SOLOMON CODE                                    | 142    |

| 7.1. Introduction                                                           | 142    |

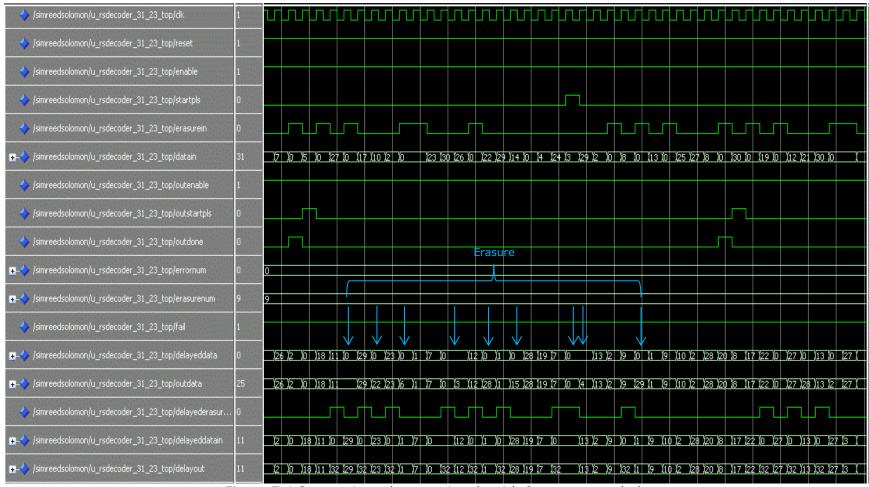

| 7.2. Erasure Only Test Bench                                                | 142    |

| 7.2.1. Correctable codeword                                                 | 142    |

| 7.2.2. Uncorrectable codeword                                               | 143    |

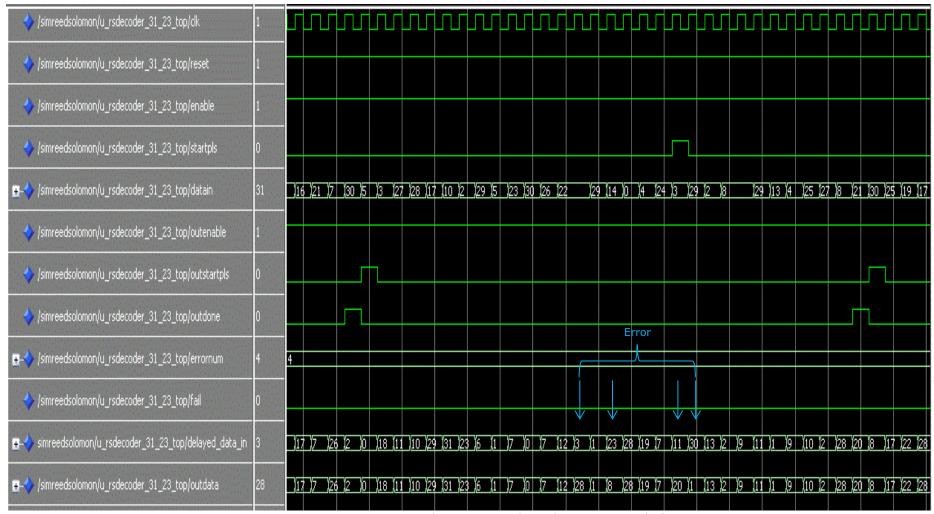

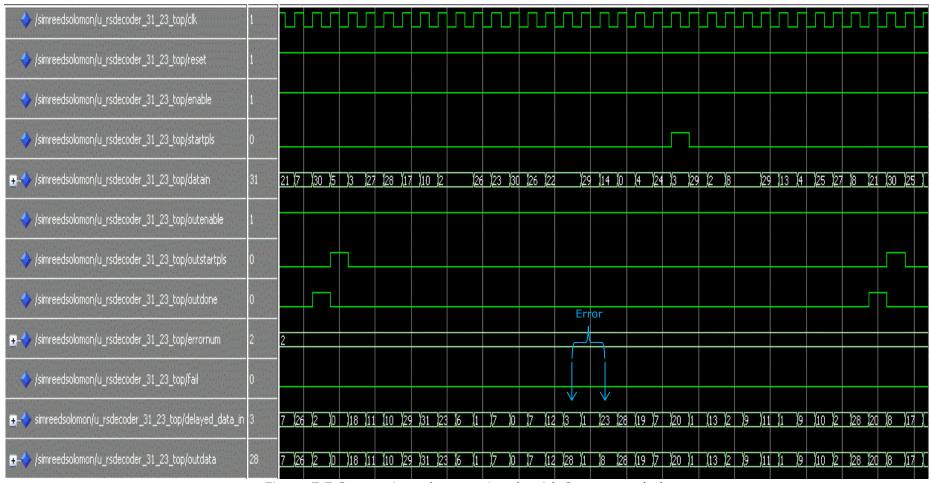

| 7.3. Error Only Test Bench                                                  | 147    |

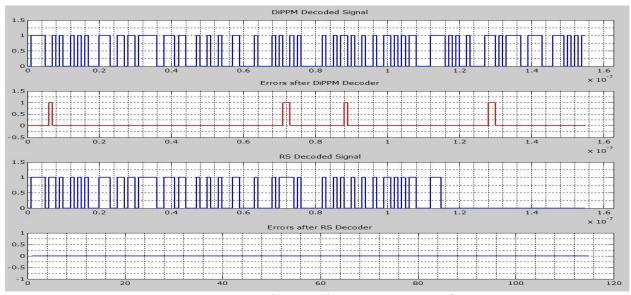

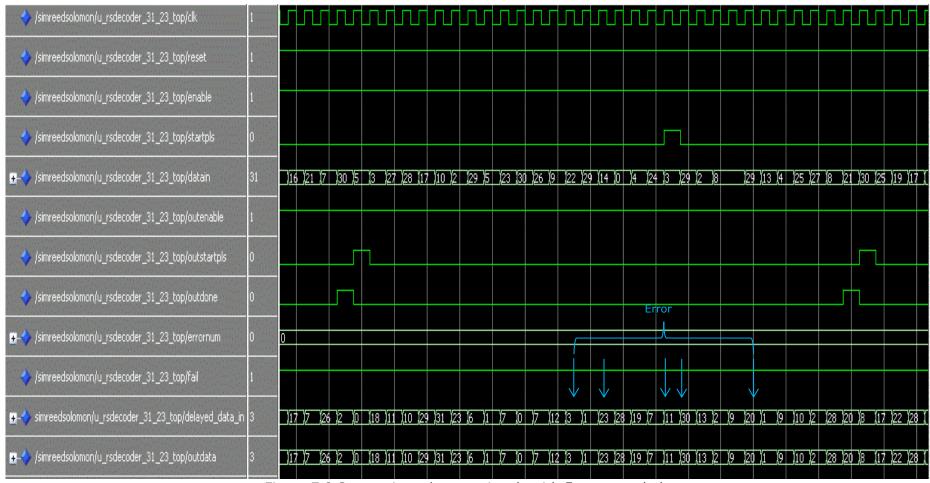

| 7.3.1. Correctable codeword                                                 | 147    |

| 7.3.2. Uncorrectable codeword                                               | 147    |

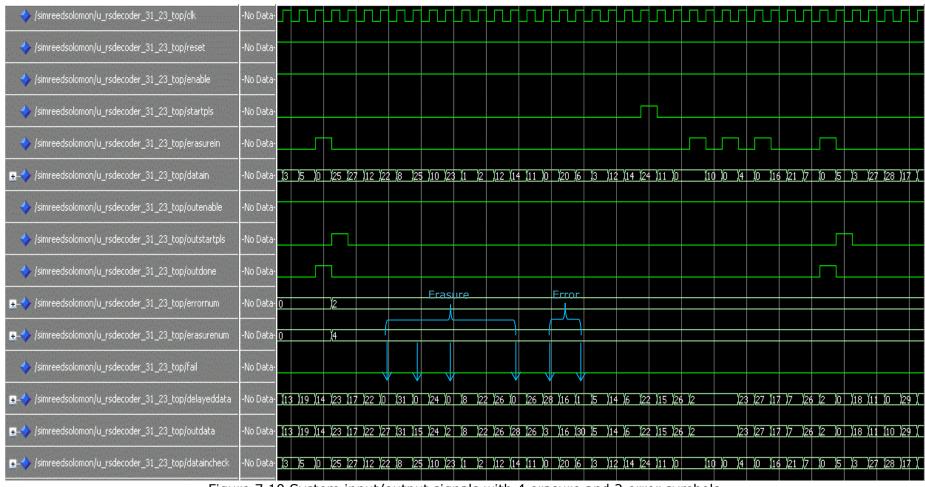

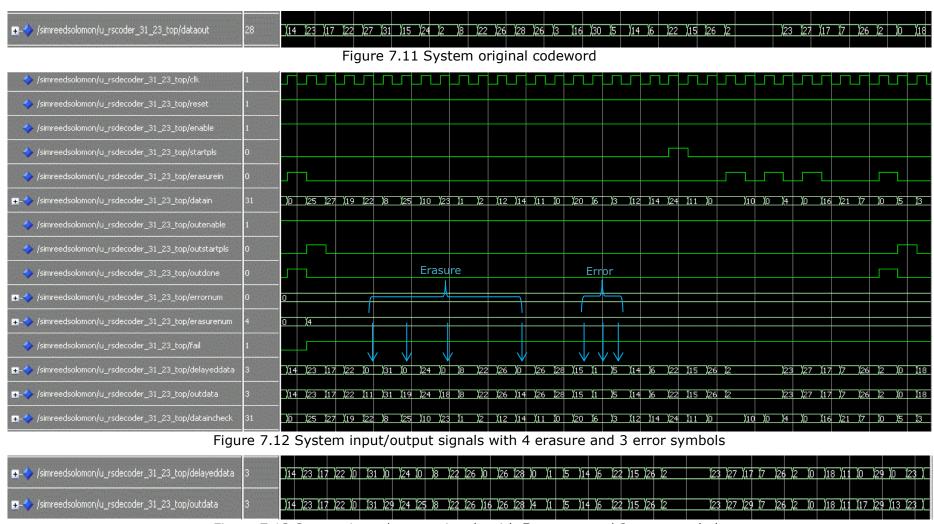

| 7.4. Erasure and Error Test bench                                           | 152    |

| 7.4.1. Correctable codeword                                                 | 152    |

| 7.4.2. Uncorrectable codeword                                               | 152    |

| 7.5. Summary                                                                | 156    |

| CHAPTER8: DIPPM EMPLOYING RS CODE SYSTEM IMPLEMENTATION BY USING FPGA       | 157    |

| 8.1. Introduction                                                           | 157    |

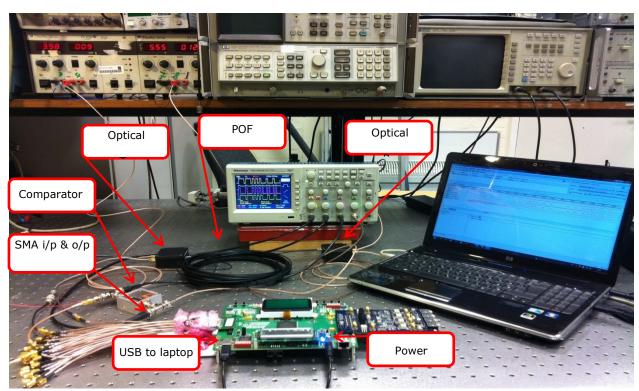

| 8.2. Experiment Hardware Resources                                          | 159    |

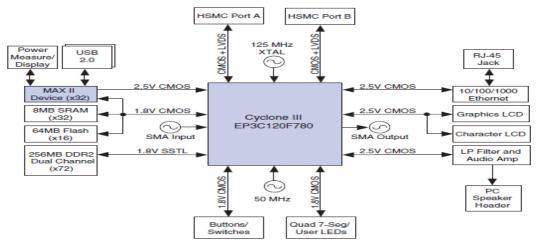

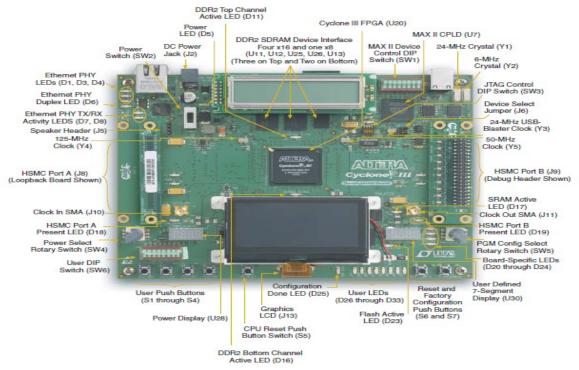

| 8.2.1. Cyclone III Development Board                                        | 159    |

| 8.2.1.1. Board Component Blocks                                             | 159    |

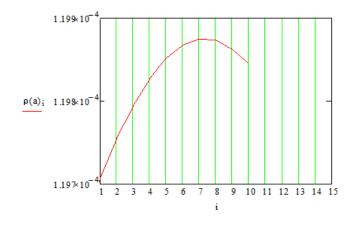

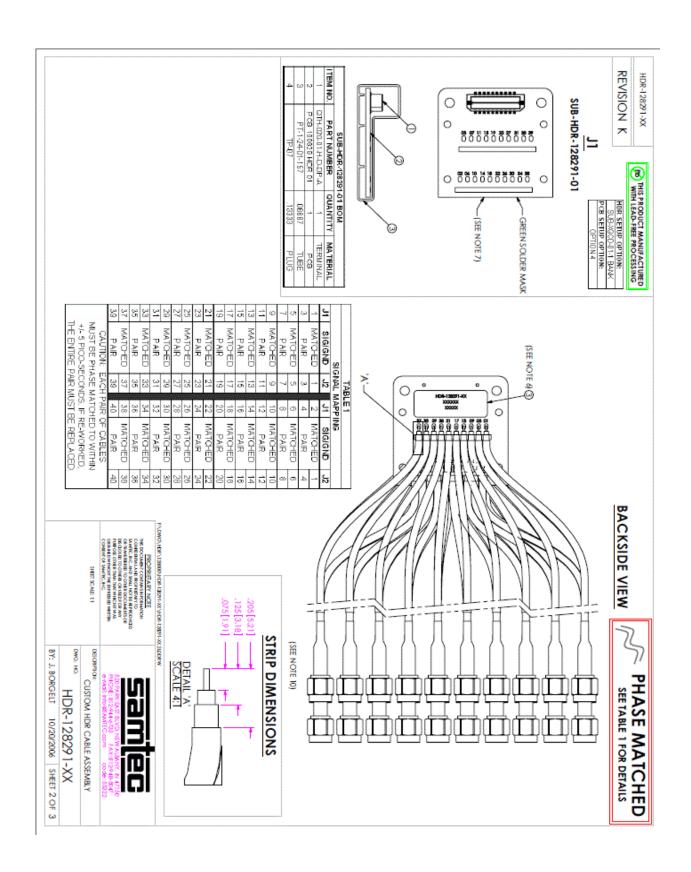

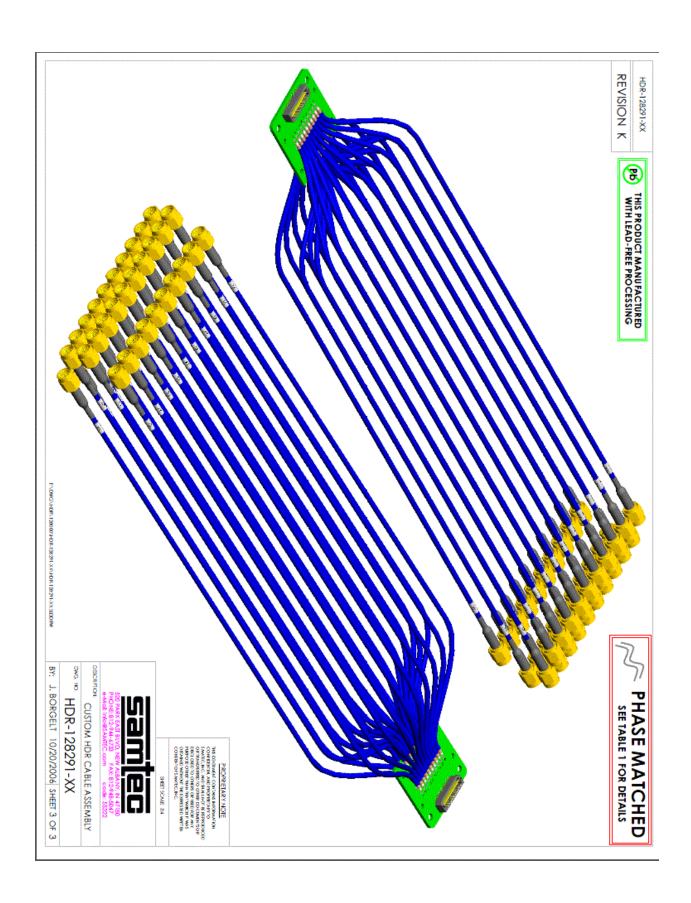

| 8.2.2. SMA Breakout Cables                                                  | 161    |

| 8.2.3. Optical Fibre Communication System                                   | 162    |

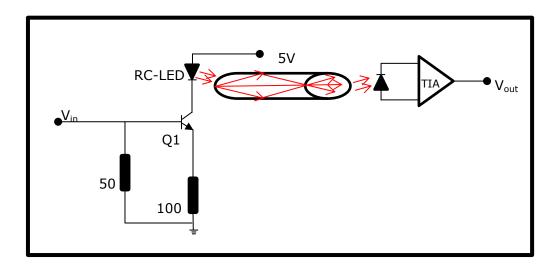

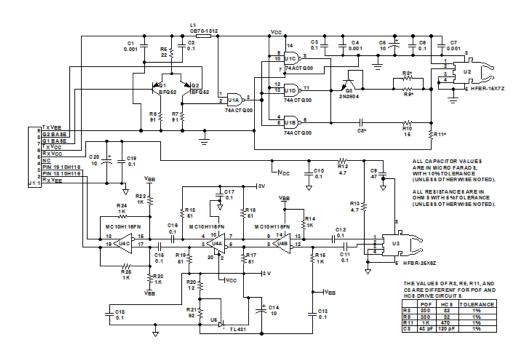

| 8.2.3.1. Optical Transmitter                                                | 162    |

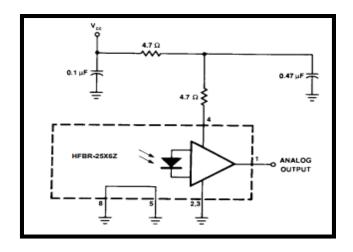

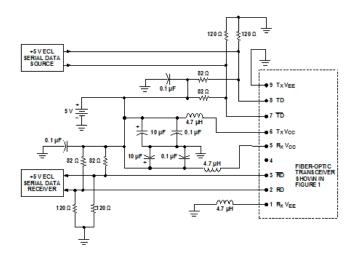

| 8.2.3.2. Optical Receiver                                                   |        |

| 8.2.3.3. The Comparator                                                     |        |

| 8.2.3.4. Plastic Optical Fibre (POF)                                        |        |

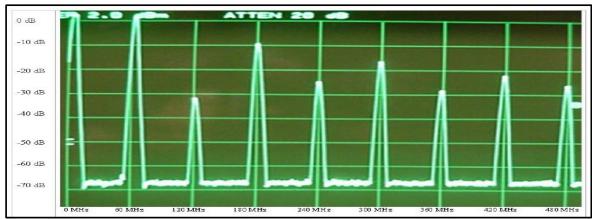

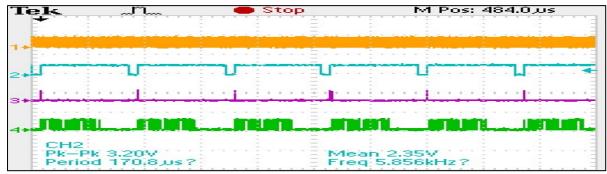

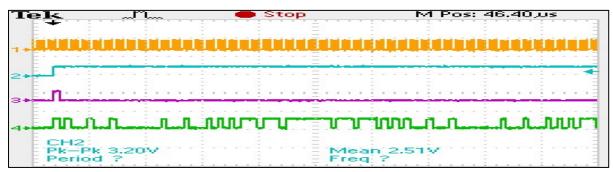

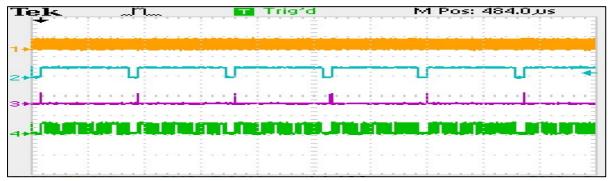

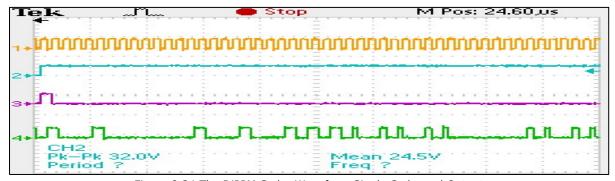

| 8.3. Test One: Implementation of DIDDM System                               | 166    |

| 8.4. TEST TW | O IMPLEMENTATION OF DIPPM WITH RS CODE SYSTEM             | 168 |

|--------------|-----------------------------------------------------------|-----|

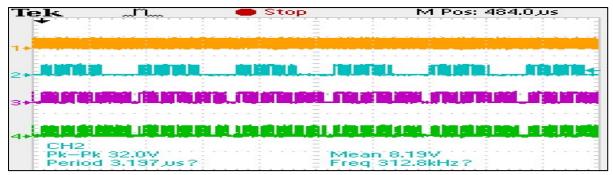

| 8.4.1. PRI   | BS Entity                                                 | 170 |

| 8.4.2. RS    | Coder Entity                                              | 171 |

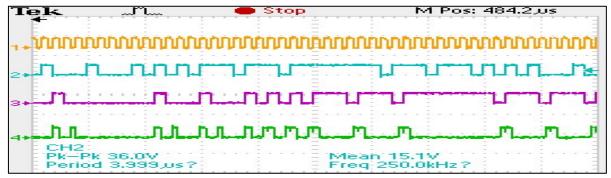

| 8.4.3. DiP   | PPM Coder Entity                                          | 172 |

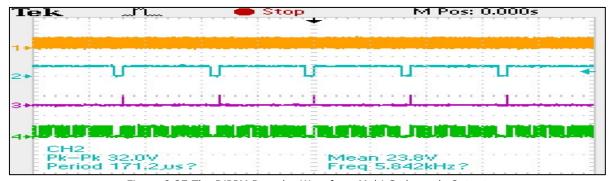

| 8.4.4. DiP   | PPM Decoder Entity                                        | 173 |

| 8.4.5. RS    | Decoder Entity                                            | 175 |

| 8.4.6. Sur   | mmary                                                     | 177 |

| CHAPTER9:    | CONCLUSION AND FURTHER WORK                               | 178 |

| 9.1. Conclus | SION                                                      | 178 |

| 9.2. FURTHER | R WORK                                                    | 180 |

| CHAPTER10:   | APPENDICES                                                | 181 |

| 10.1. Append | DIX 1                                                     | 181 |

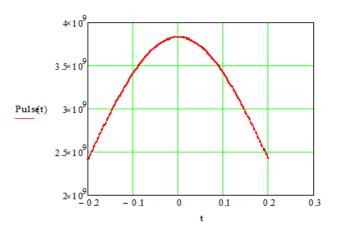

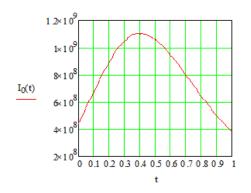

| 10.1.1. Di   | iPPM & RS Mathcad simulation for slope detection method   | 181 |

| 10.1.2. Di   | iPPM & RS Mathcad simulation for central detection method | 195 |

| 10.2. APPENI | DIX 2                                                     | 228 |

| 10.2.1. Di   | iPPM Matlab simulation                                    | 228 |

| 10.2.2. Fι   | unction of DiPPM coder                                    | 231 |

| 10.2.3. Fι   | unction of DiPPM decoder                                  | 232 |

| 10.2.4. Di   | iPPM & RS Matlab Simulation                               | 233 |

| 10.2.5. Fι   | unction of Galois field to decimal transformation         | 238 |

| 10.3. APPEND | 3                                                         | 239 |

| 10.3.1. PI   | RBS VHDL source code                                      | 239 |

| 10.3.2. RS   | S coder VHDL source code                                  | 241 |

| 10.3.3. Po   | arallel to searial bridge VHDL source code                | 246 |

| 10.3.4. Di   | iPPM coder VHDL source code                               | 250 |

| 10.3.5. Cl   | hannel model VHDL source code                             | 252 |

| 10.3.6. Di   | iPPM decoder VHDL source code                             | 254 |

| 10.3.7. Se   | earial to parallel bridge VHDL source code                | 256 |

| 10.3.8. RS   | S decoder VHDL source code                                | 260 |

| 10.4. APPENI | 4                                                         | 277 |

| 10.4.1. Er   | rasure only test bench VHDL source code                   | 277 |

| 10.4.2. Er   | rror only test bench VHDL source code                     | 284 |

| 10.4.3. Er   | rasure & Error test bench VHDL source code                | 291 |

| 10.5. APPENI | DIX 5                                                     | 298 |

| 10.5.1. Fi   | eld of (31,23)RS code                                     | 298 |

| 10.6. APPENI | MIX 6                                                     | 299 |

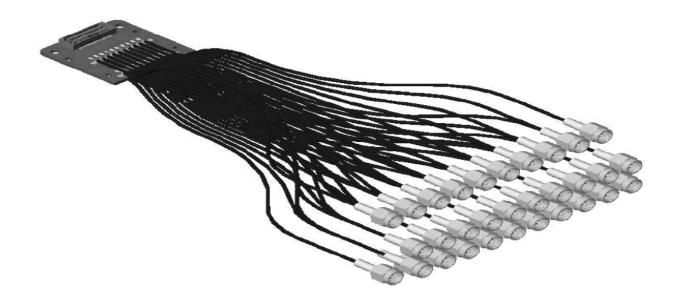

| 1061 (1      | MA breakout cables data sheet                             | 200 |

| 10.6.2. Op  | tical transmitter & receiver data sheet | 302 |

|-------------|-----------------------------------------|-----|

| 10.6.3. Coi | mparator data sheet                     | 314 |

| 10.6.4. PO  | PF data sheet                           | 325 |

| CHAPTER11:  | REFERENCES                              | 334 |

# **List of Figures**

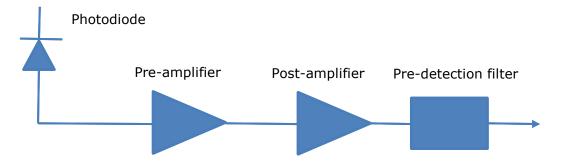

| FIGURE 1.1 THE BASIC STRUCTURE OF AN OPTICAL RECEIVER (SIBLEY, 1995)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 22          |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

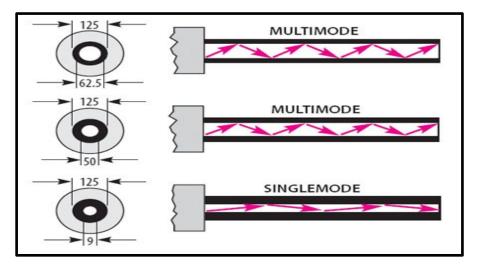

| FIGURE 1.2 TYPES OF OPTICAL FIBRE (SIBLEY, 1995)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 23          |

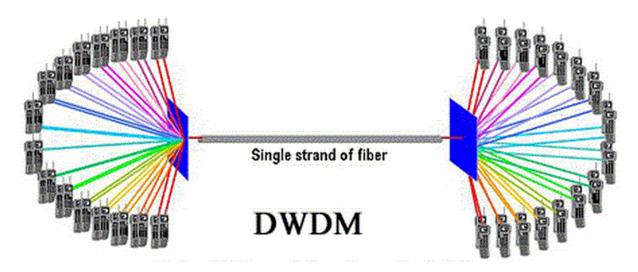

| FIGURE 1.3 40 VIRTUAL HIGH SPEED CHANNELS PER PHYSICAL FIBRE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 24          |

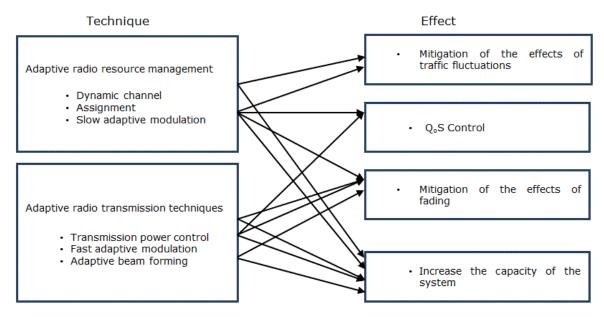

| FIGURE 2.1 OVER OF ADAPTIVE MODULATION SYSTEM (SASAOKA, 2000)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 35          |

| Figure 2.2 Pulse Position Modulation (Liu, 2002)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 37          |

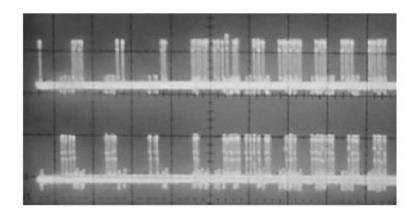

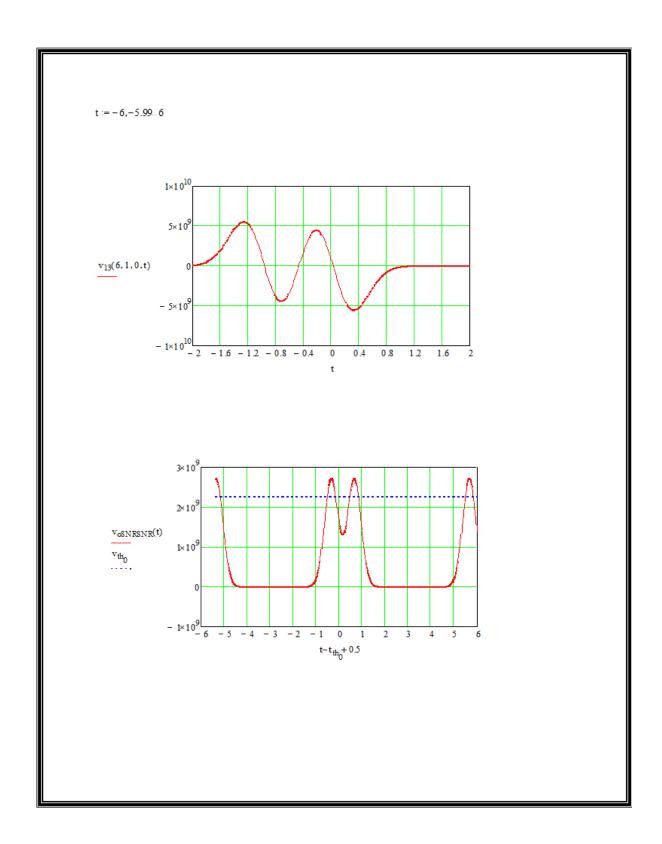

| FIGURE 2.3 ABOVE IMAGE REPRESENTING DECODER INPUT, BELOW IMAGE REPRESENTING MLSD RESULTS (CHARITOPOUL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | OS, SIBLEY, |

| & Mather, 2011)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 40          |

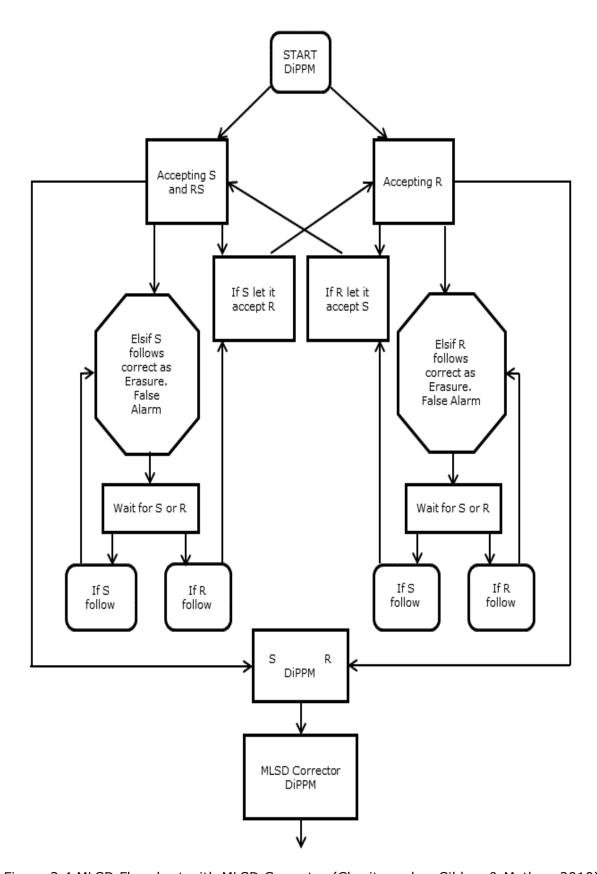

| FIGURE 2.4 MLSD FLOWCHART WITH MLSD CORRECTOR (CHARITOPOULOS, SIBLEY, & MATHER, 2010)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 41          |

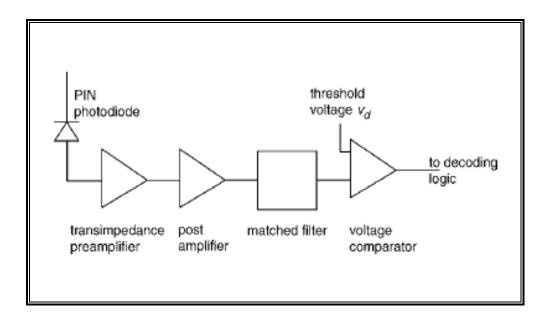

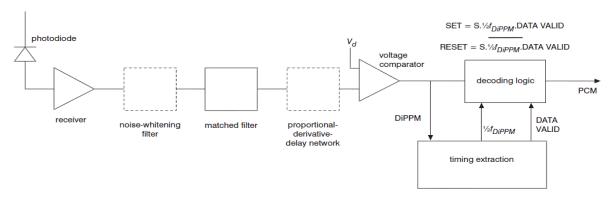

| Figure 2.5 Block diagram of receiver system (Sibley, 2005)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 45          |

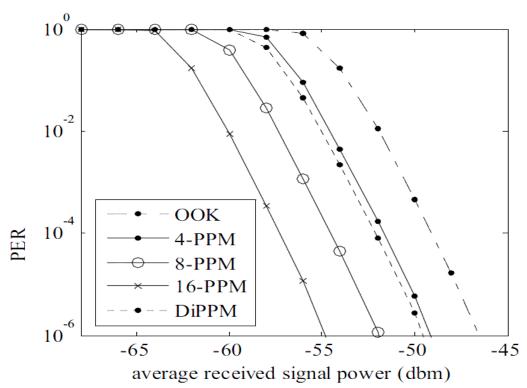

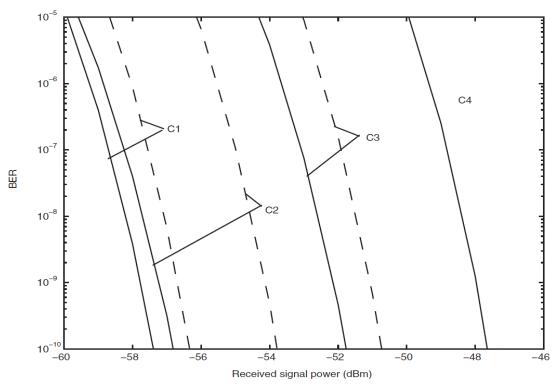

| FIGURE 2.6 PACKET ERROR RATE COMPARISONS OF OOK, 4-PPM, 8-PPM, 16-PPM AND DIPPM (WANG ET AL, 2007                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | )46         |

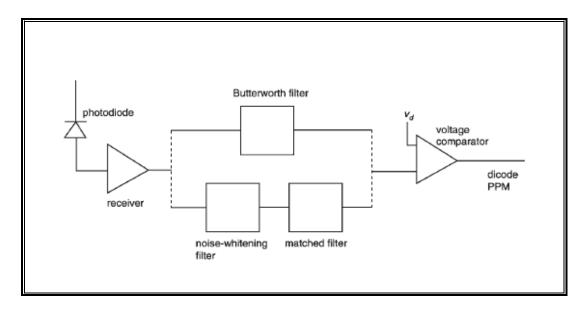

| FIGURE 2.7 BLOCK DIAGRAM OF DICODE PPM RECEIVER USED IN SIMULATIONS (SIBLEY, 2004)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 47          |

| FIGURE 2.8 SYSTEM OF REED SOLOMON CODE (RILEY & RICHARDSON, 1998)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 51          |

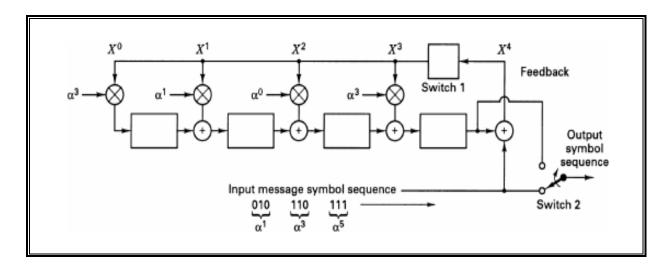

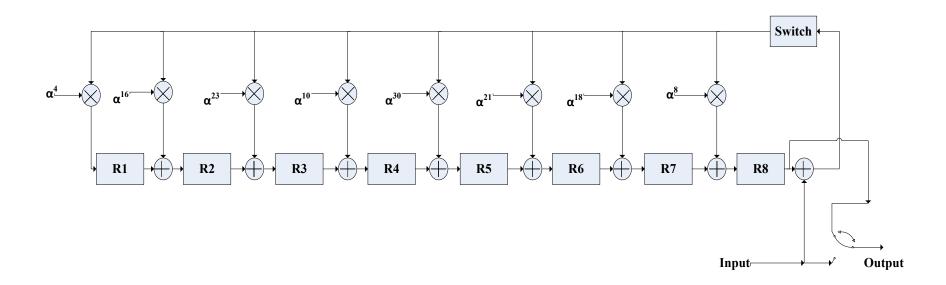

| Figure 2.9 Systematic Encoding with an (n - k)—Stage Shift Register (Sklar, n.d)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 53          |

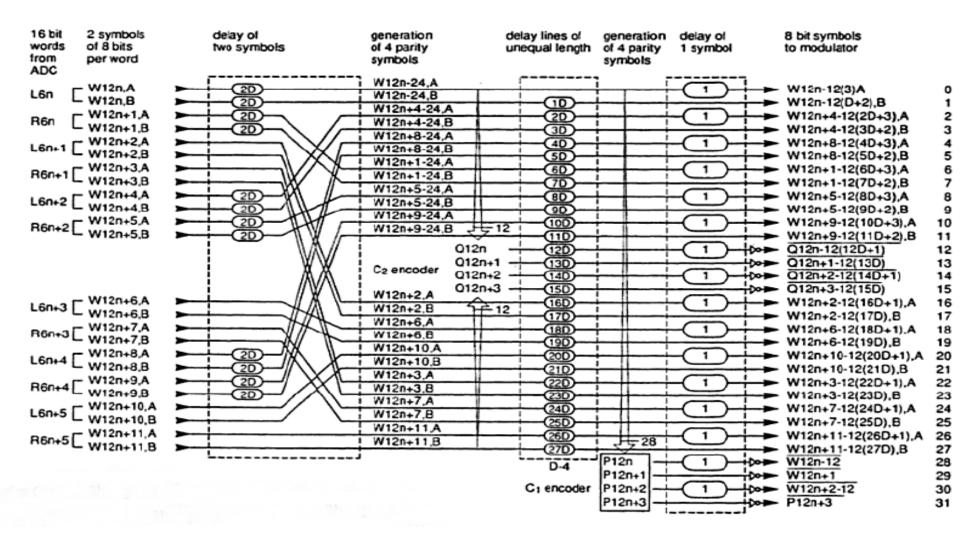

| FIGURE 2.10 BLOCK DIAGRAM OF CIRC (PAVERT, 2011)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 54          |

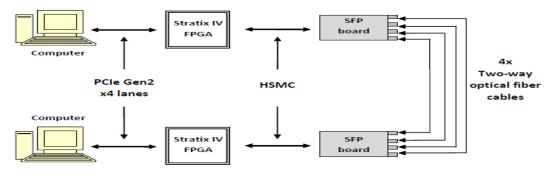

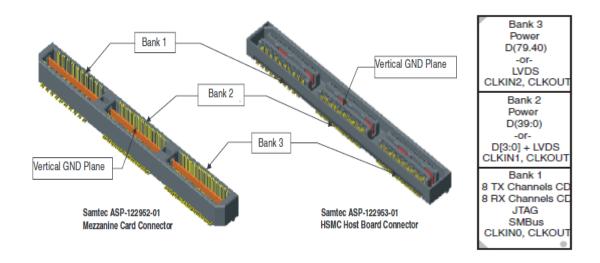

| FIGURE 2.11 THE HARDWARE SETUP FOR LINKAGE AND PERFORMANCE OF THE FPGA WITH COMMUNICATION CHANNELS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | (KADRIC,    |

| 2011)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 58          |

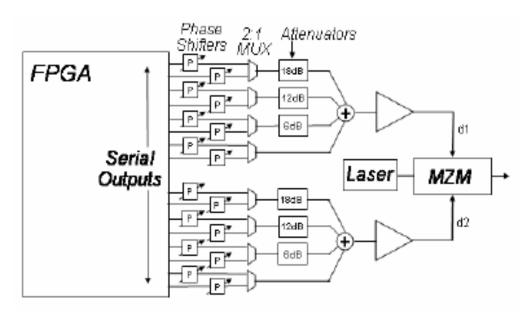

| FIGURE 2.12 MICROWAVE AND OPTICAL COMPONENTS OF THE DIGITALLY PROGRAMMABLE OPTICAL TRANSMITTER (WATER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | rs et al,   |

| 2006.)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 59          |

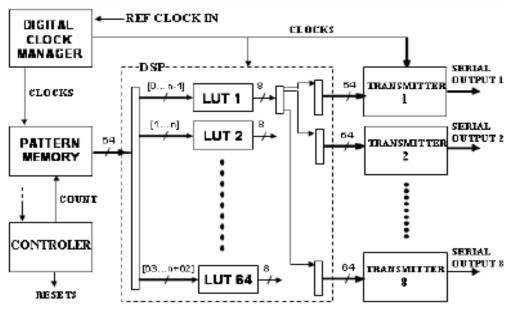

| FIGURE 2.13 THE DESIGN OF THE FPGA (WATTS ET AL, 2006)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 60          |

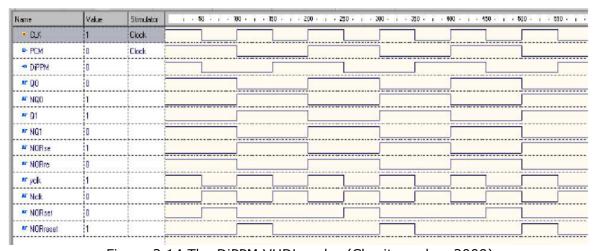

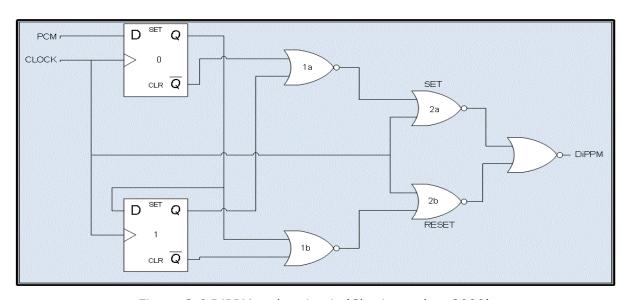

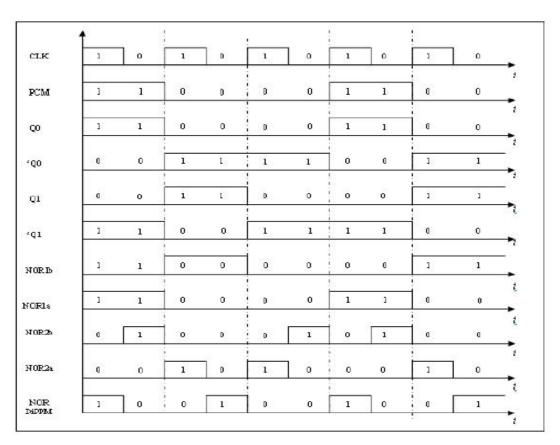

| FIGURE 2.14 THE DIPPM VHDL CODER (CHARITOPOULOS, 2009)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 61          |

| FIGURE 2.15 DIPPM UPGRADED VERSIONS OF CODER DECODER (CHARITOPOULOS, 2009)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 62          |

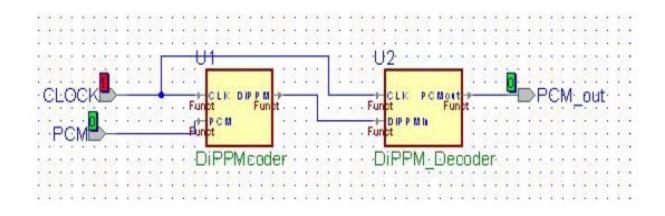

| FIGURE 2.16 VHDL: DIPPM CODER PROCESS IN QUARTUS (CHARITOPOULOS, 2009)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 63          |

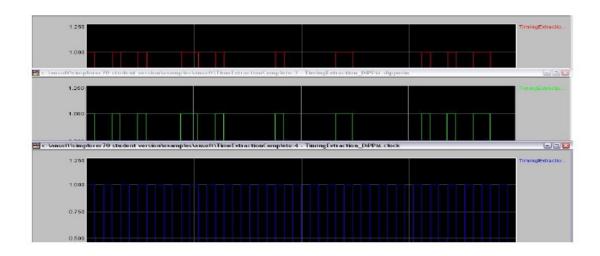

| FIGURE 2.17 DIPPM IN (TOP TRACE), DIPPM OUT (MIDDLE TRACE), CLOCK RECOVERED (BOTTOM TRACE) (CHARITOPOU                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | LOS, 2009)  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 64          |

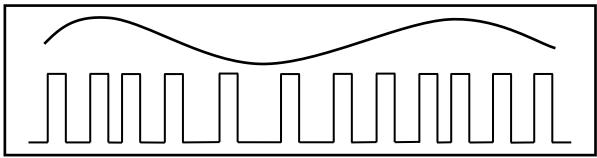

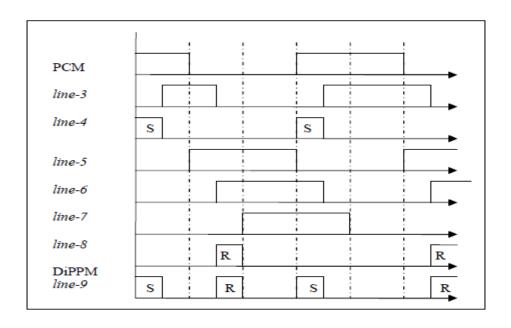

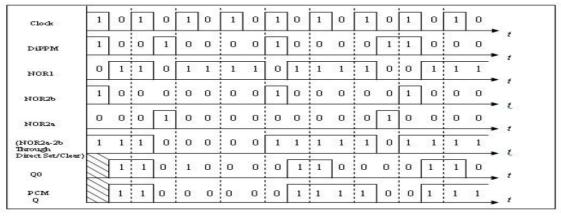

| FIGURE 3.1 PCM DATA (TOP TRACE), DICODE TECHNIQUE (MIDDLE TRACE), AND DICODE PPM (BOTTOM TRACE)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 66          |

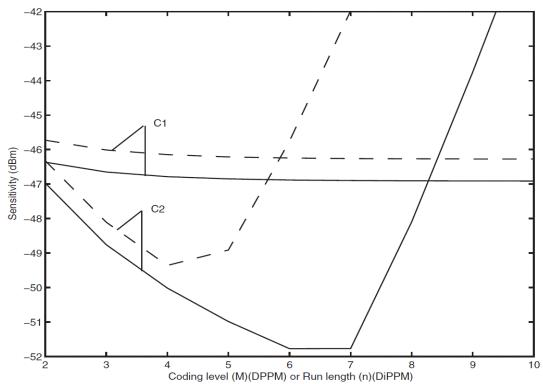

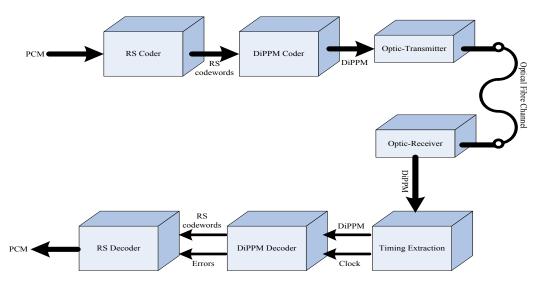

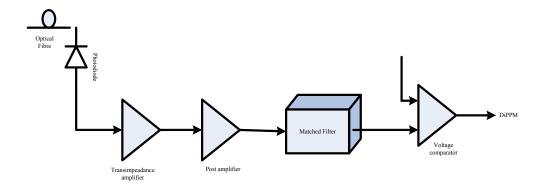

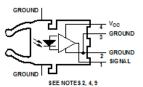

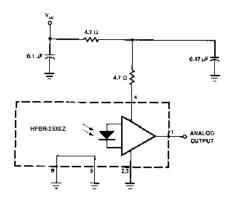

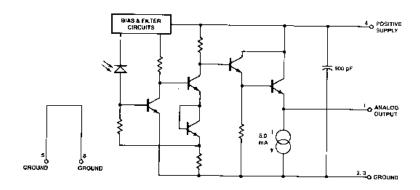

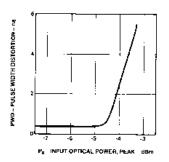

| FIGURE 3.2 SCHEMATIC REPRESENTATION OF THE DICODE PPM RECEIVER (SIBLEY, 2003)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 68          |

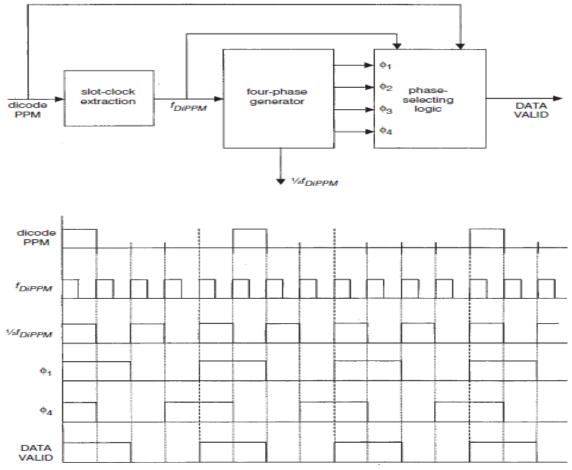

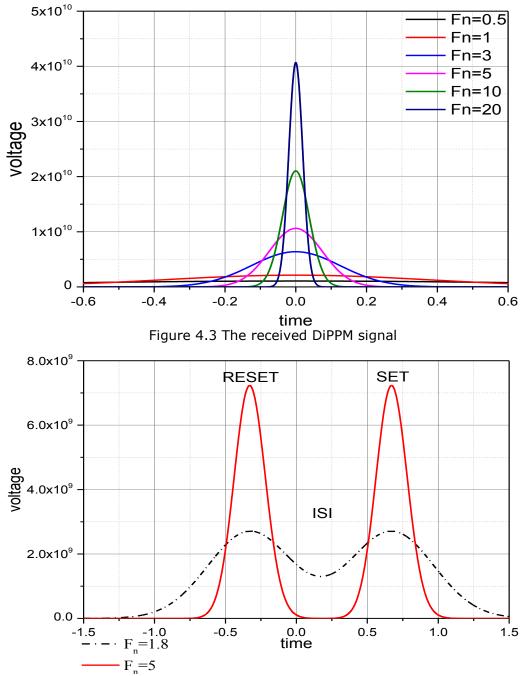

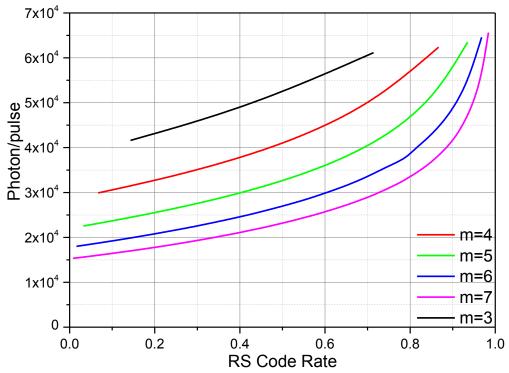

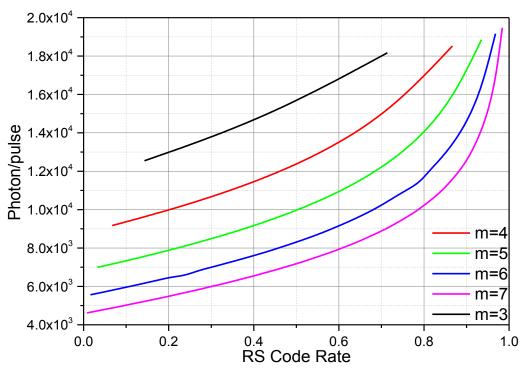

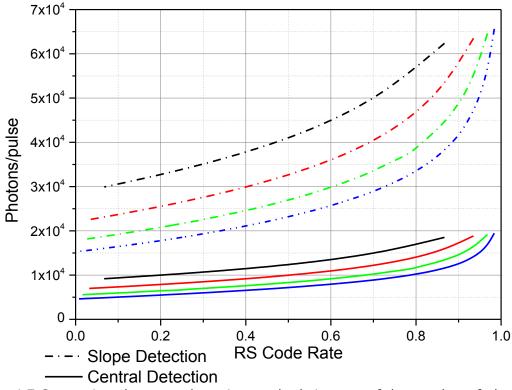

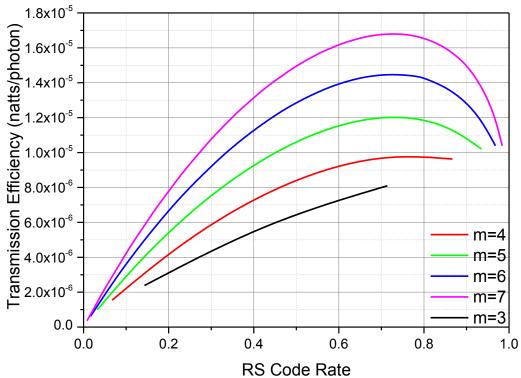

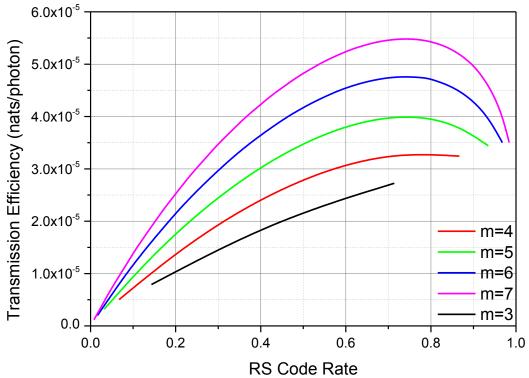

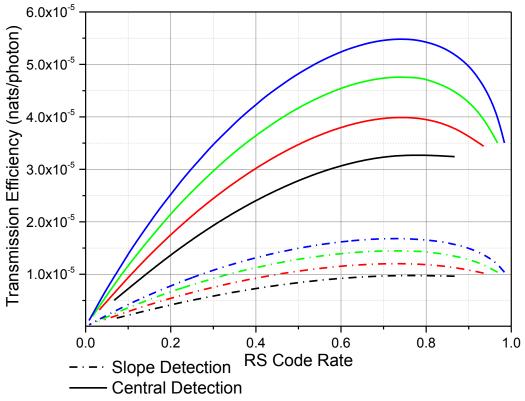

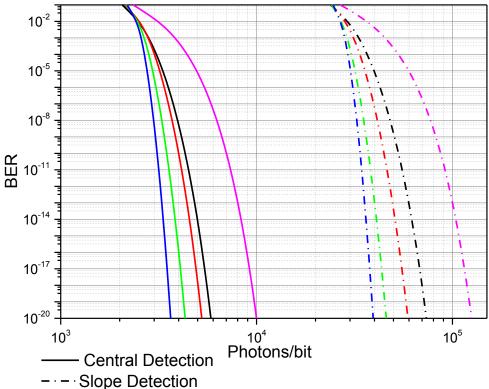

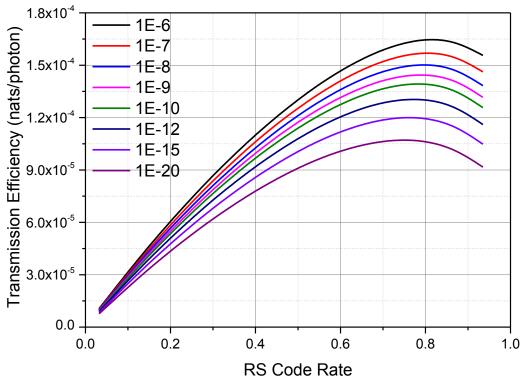

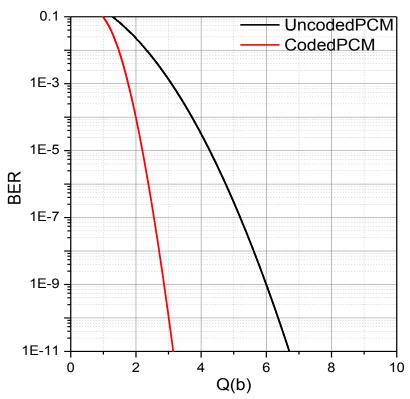

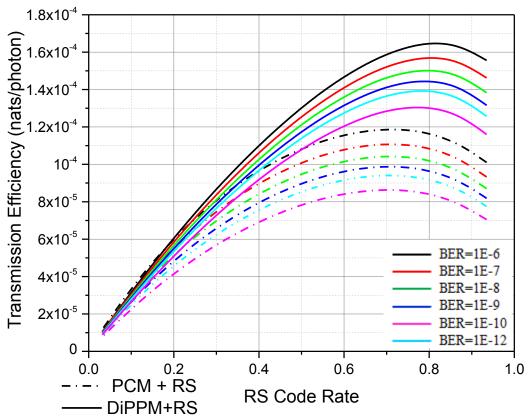

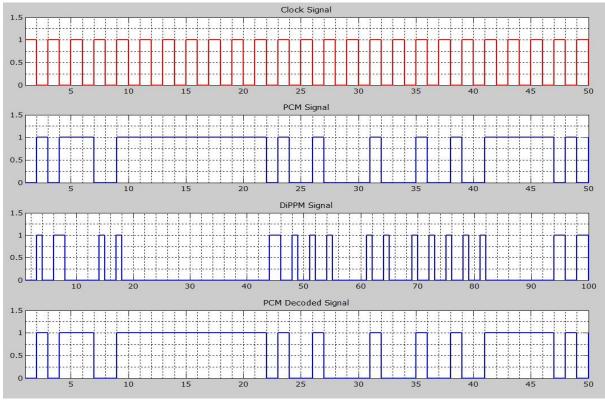

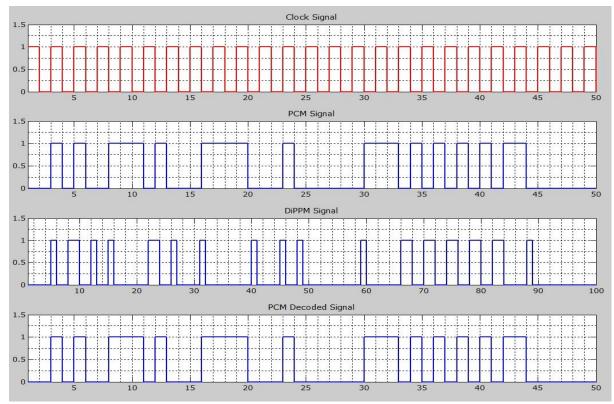

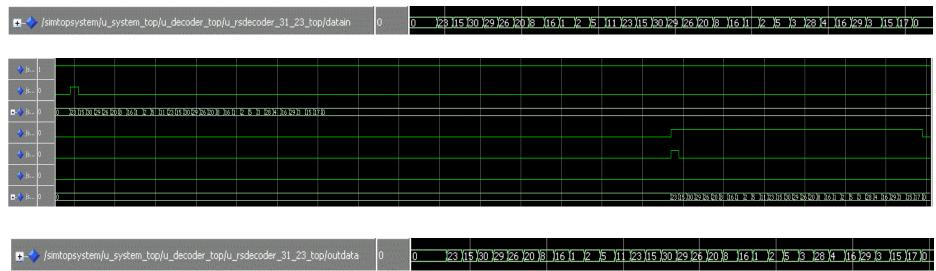

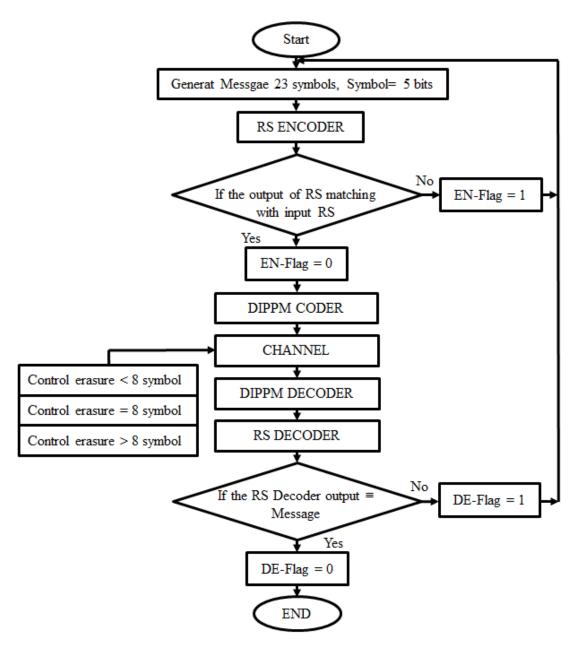

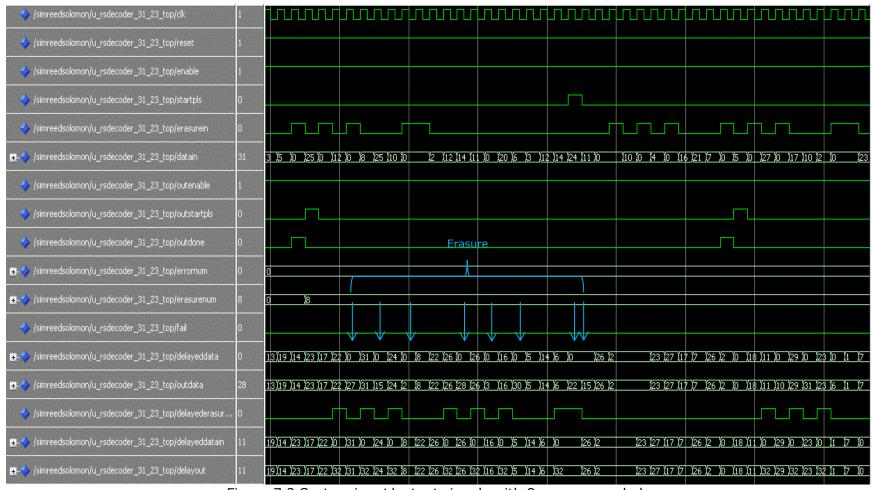

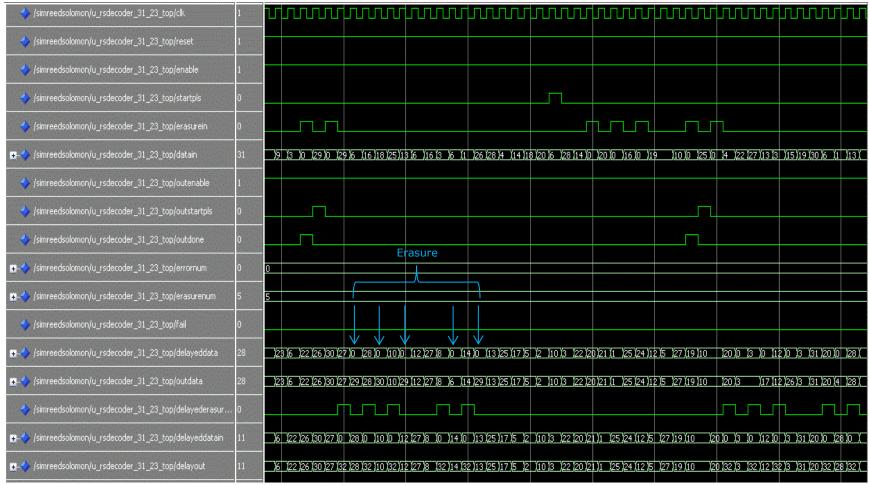

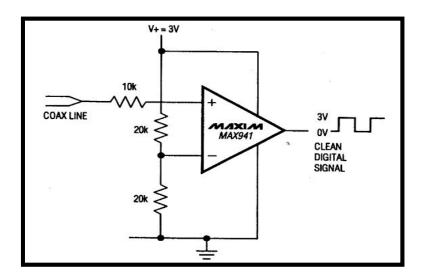

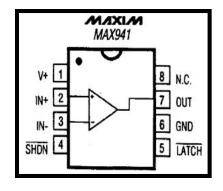

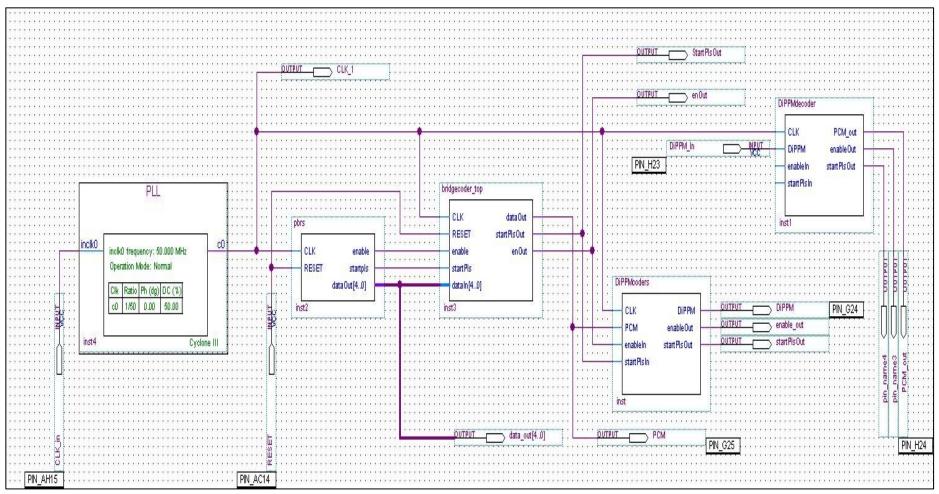

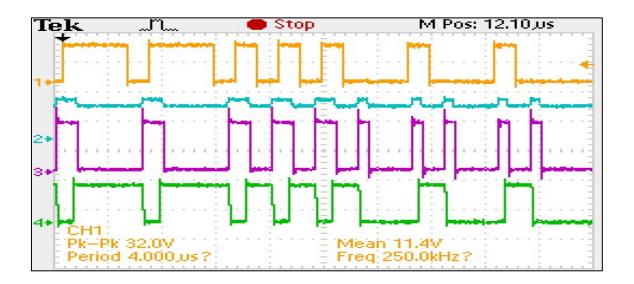

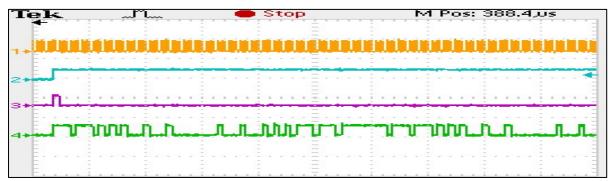

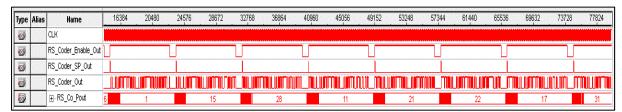

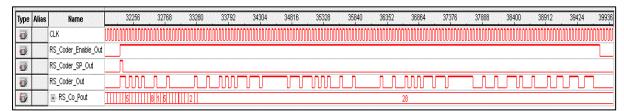

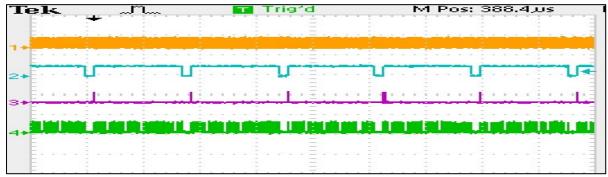

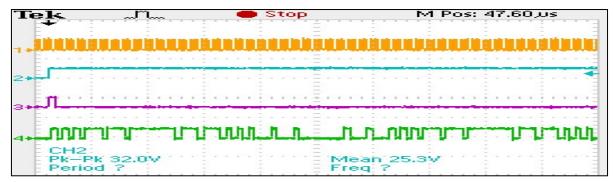

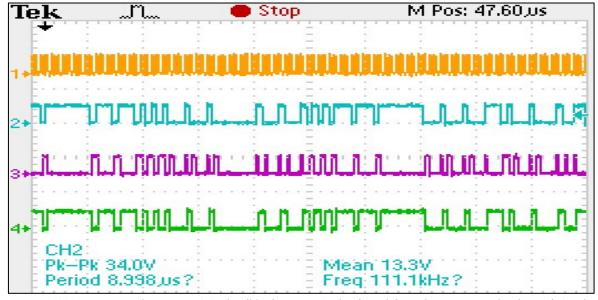

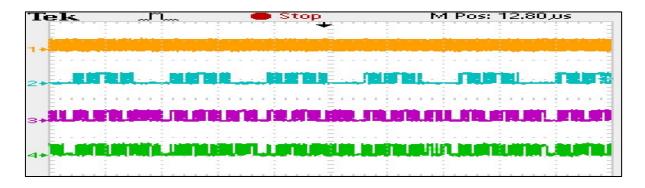

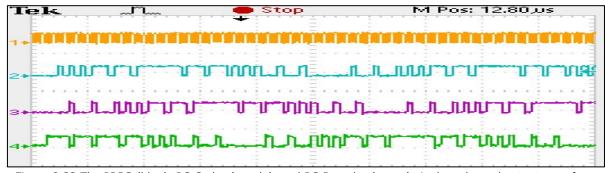

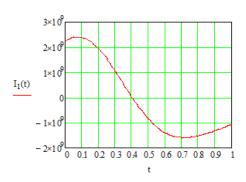

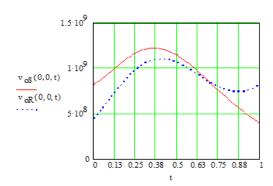

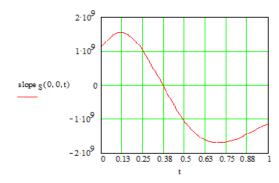

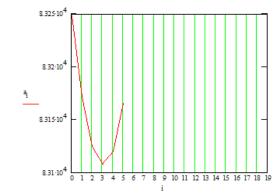

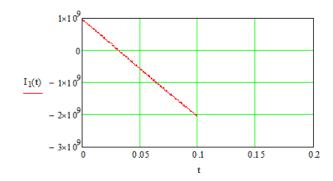

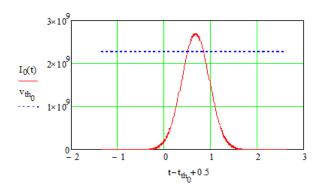

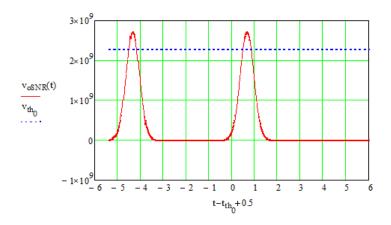

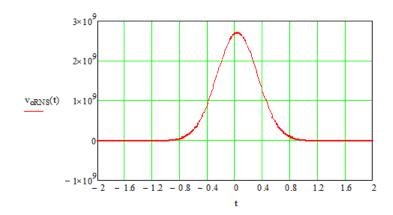

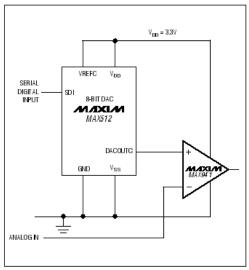

| FIGURE 3.3 BLOCK DIAGRAM OF PROPOSED TIMING EXTRACTION SYSTEM AND RELATED TIMING DIAGRAM (SIBLEY, 2003)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 68          |