## **University of Huddersfield Repository**

Farhat, Zohaib Ali

DESIGN AND SYSTEM IMPLEMENTATION OF PULSE POSITION MODULATION (PPM) BASED CODING SYSTEMS

#### **Original Citation**

Farhat, Zohaib Ali (2021) DESIGN AND SYSTEM IMPLEMENTATION OF PULSE POSITION MODULATION (PPM) BASED CODING SYSTEMS. Doctoral thesis, University of Huddersfield.

This version is available at http://eprints.hud.ac.uk/id/eprint/35703/

The University Repository is a digital collection of the research output of the University, available on Open Access. Copyright and Moral Rights for the items on this site are retained by the individual author and/or other copyright owners. Users may access full items free of charge; copies of full text items generally can be reproduced, displayed or performed and given to third parties in any format or medium for personal research or study, educational or not-for-profit purposes without prior permission or charge, provided:

- The authors, title and full bibliographic details is credited in any copy;

- A hyperlink and/or URL is included for the original metadata page; and

- The content is not changed in any way.

For more information, including our policy and submission procedure, please contact the Repository Team at: E.mailbox@hud.ac.uk.

http://eprints.hud.ac.uk/

# DESIGN AND SYSTEM IMPLEMENTATION OF PULSE POSITION MODULATION (PPM) BASED CODING SYSTEMS

by

## Zohaib Ali Farhat

A thesis submitted to the University of Huddersfield in partial fulfilment of the requirements for the degree of Doctor of Philosophy

School of Computing and Engineering

University of Huddersfield

UK

May 2021

# Abstract

The physical layer or modulation scheme plays a key role in a communication system, where performance features like Bit-Error Rate (BER), bandwidth efficiency and sensitivity are all dependent on the type of modulation scheme used. Currently, there are numerous modulation schemes for any given communication system, requiring the designer to decide which modulation scheme to apply. Many researchers propose different modulation schemes as the optimal for a given system with the aid of mathematical models and equations. However, there is minimal evidence on the practical implementation and testing of difference schemes to fully justify the selection. The scope of this research is to practically analyse, compare and validate the performance of different Pulse Position Modulation (PPM) schemes, where PPM is preferred for modulating and demodulating the signal in optical communications. This work presents, for the first time, practical analysis and comparison of different PPM techniques including Digital PPM (DPPM), Multipulse PPM (MPPM), Offset PPM Dicode (DiPPM) and Duobinary PPM (DuoPPM). The (OPPM), svstem implementation of these PPM techniques was carried under identical operational system conditions using Hardware-in-loop (HIL) approach, to validate the performance.

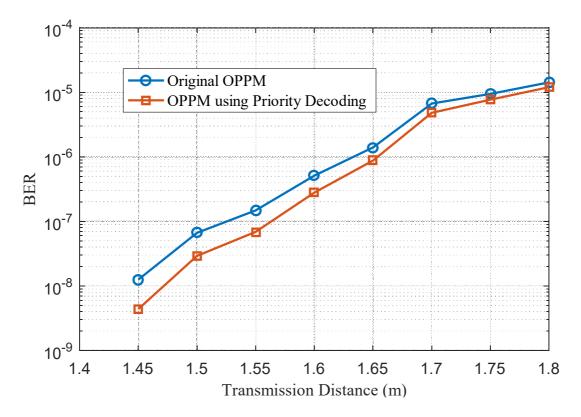

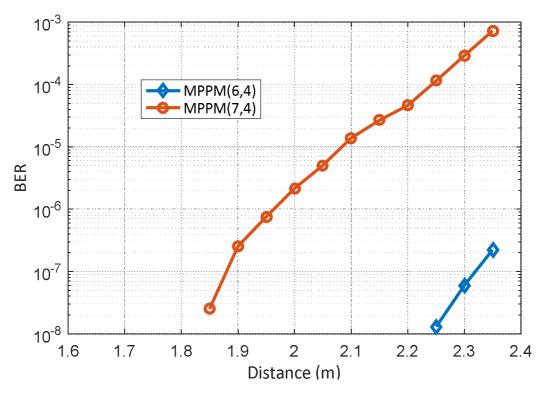

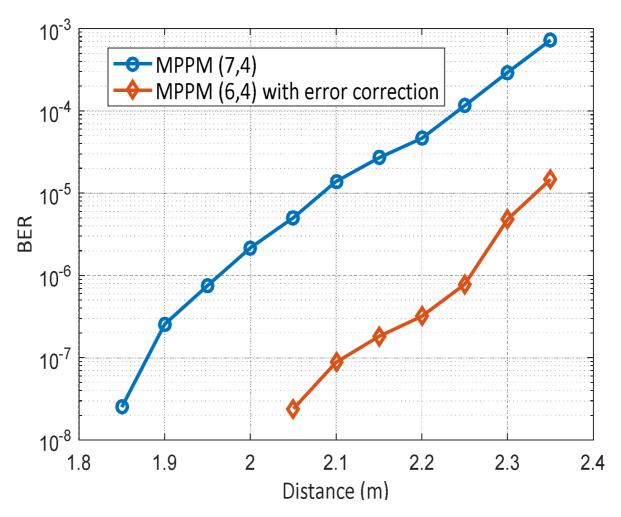

A visible light communication (VLC) system incorporating a high power commercial 20 W LED was used for the implementation of PPM schemes. An FPGA was used to encode the message into PPM formats and to transmit it over the LED. A comprehensive comparison was performed between several PPM schemes in terms of BER, power estimation and bandwidth utilisation. Additionally, a new modified form of MPPM, called modified MPPM (MPPM64), was proposed in this study, which improves the bandwidth utilisation of the communication system by 14.28%. Furthermore, a new error correction method for OPPM, called Priority Decoding, was proposed to improve the BER of OPPM. Experimentation revealed the improved performance of OPPM by achieving 10 times fewer errors with BER of less than 10<sup>-8</sup>.

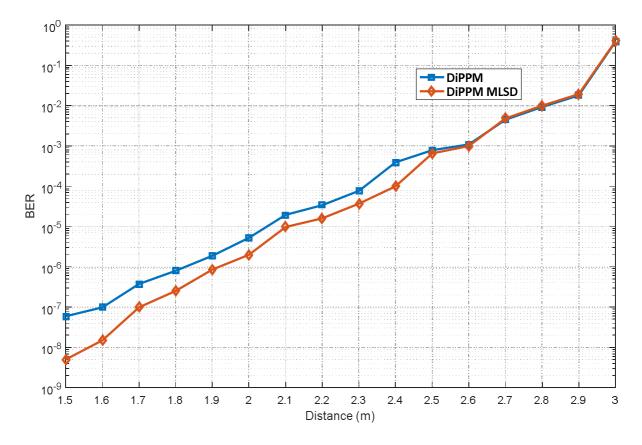

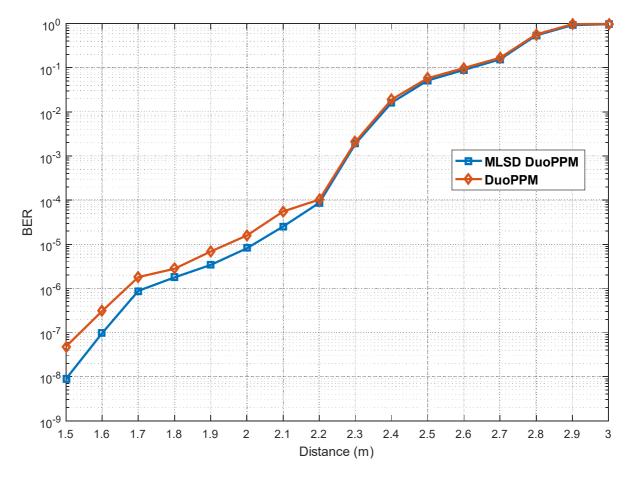

A testbench was developed, which enables the user to apply any PPM from the given PPM schemes to a communication system. This testbench can be used to evaluate the performance of the communication system and to find the suitable PPM scheme which will deliver the best performance. Error correction techniques including Parity check and Cyclic Redundancy Check (CRC) were implemented to improve system performance. MPPM64 was implemented with Parity check and CRC achieving 0.4 m in transmission distance at identical transmission speeds when compared with the original scheme. Maximum Likelihood Detection (MLSD) was implemented with DiPPM and DuoPPM, showing 40% and 37.4% theoretical improved performance, respectively. In the practical implementation of MLSD, a 10 times achievement was recorded in BER at 1.5 m, outperforming original DiPPM and DuoPPM schemes.

Determining the most appropriate PPM scheme for a VLC or any given system is not straight forward as it depends on many system parameters. However, this work enables the user to identify the most appropriate scheme for any given VLC system. This work enables different system parameters such as BER, transmission distance, power estimation and bandwidth utilization to be taken into account when determining the most appropriate setup. A detailed comparison is shown to guide modulation scheme selection in optical applications based on different parameter limitations.

# Acknowledgement

I would like to offer my sincere acknowledgement to my supervisor Dr Peter Mather, for his experience, patience and assistance which helped me to reach the required level for this research. I would also like to thank my second supervisor Dr Martin Sibley for his continued support.

I would like to thank my colleges Yuxiang, Mostafa, Wahab, faculty members, research administration and other research colleges, who have made my experience wonderful during my time at the university.

I would particularly like to thank my parents, my wife and my siblings. Special thanks and gratitude to my mother and father and for their high expectations and faith in me. I would like to especially thank my wife, Haleema, who was very supportive, motivating and encouraging me during my research.

# COPYRIGHT

- I. The author of this thesis (including any appendices and/or schedules to this thesis) owns any copyright in it (the "Copyright") and he s/has given The University of Huddersfield the right to use such copyright for any administrative, promotional, educational and/or teaching purposes.

- II. Copies of this thesis, either in full or in extracts, may be made only in accordance with the regulations of the University Library. Details of these regulations may be obtained from the Librarian. This page must form part of any such copies made.

- III. The ownership of any patents, designs, trademarks and any and all other intellectual property rights except for the Copyright (the "Intellectual Property Rights") and any reproductions of copyright works, for example graphs and tables ("Reproductions"), which may be described in this thesis, may not be owned by the author and may be owned by third parties. Such Intellectual Property Rights and Reproductions cannot and must not be made available for use without the prior written permission of the owner(s) of the relevant Intellectual Property Rights and/or Reproductions.

# **List of Publications**

- Farhat, Z. A., Ahfayd, M. H., Mather, P. J., & Sibley, M. J. "Improved BER for offset pulse position modulation using priority decoding over VLC system," Wireless Days (WD), Manchester, United Kingdom, 24-26 April 2019, pp. 1-4.

*Contribution:* Proposed a new method of error correction, called Priority decoding, for Offset PPM; which improved the overall performance of Offset PPM.

- Ahfayd, M. H., Farhat, Z. A., Sibley, M. J., Mather, P. J., & Lazaridis, P. I. "Selection of high power LEDs for Li-Fi applications," 25th International Conference on Telecommunications (ICT), Saint Malo, France, 26-28 June 2018, pp. 170-174.

*Contribution:* Contributed in setting up the hardware circuitry, specifically the

comparator circuitry, and identified the 20 W and 30 W LEDs outperform high and low power LEDs.

Farhat, Z. A., Ahfayd, M. H., Mather, P. J., & Sibley, M. J. "Practical implementation of duobinary pulse position modulation using FPGA and visible light communication," *IEEE 15th Student Conference on Research and Development (SCOReD),* Putrajaya, Malaysia, 13-14 December 2017, pp. 253-256.

**Contribution:** Design and implementation of Duobinary PPM modulation scheme on the FPGA. Identified Intersymbol interference as the main source of error.

Ahfayd, M. H., Farhat, Z. A., Sibley, M. J., Mather, P. J., & Lazaridis, P. I. "Visible light communication based system using high power LED and dicode pulse position modulation technique," *25th Telecommunication Forum* (*TELFOR*), Belgrade, Serbia, 21-22 November 2017, pp. 1-4.

*Contribution:* Design and implementation of Dicode PPM modulation scheme on the FPGA.

# Contents

| Abstract                                                          | 2  |

|-------------------------------------------------------------------|----|

| Acknowledgement                                                   | 3  |

| COPYRIGHT                                                         | 4  |

| List of Publications                                              | 5  |

| Contents                                                          | 6  |

| List of Figures                                                   |    |

| List of Tables                                                    | 12 |

| List of Abbreviations                                             | 13 |

| Chapter 1 Introduction                                            | 15 |

| 1.1 Introduction                                                  | 15 |

| 1.2 Different types of PPM schemes                                |    |

| 1.2.1 Motivation and Novel aspects of the research                |    |

| 1.3 Aims                                                          |    |

| 1.4 Objectives                                                    |    |

| 1.5 Novel contributions                                           | 21 |

| 1.6 Thesis Structure                                              |    |

| Chapter 2 Background and Literature Review                        |    |

| 2.1 Introduction                                                  |    |

| 2.2 Types of communication systems                                | 24 |

| 2.3 Importance of modulation in communication systems             | 24 |

| 2.4 Optical Communications and its advantages                     | 25 |

| 2.5 Basic elements of a communication system                      | 27 |

| 2.5.1 The transmitter                                             | 27 |

| 2.5.2 The transmission channel                                    |    |

| 2.5.3 The receiver                                                |    |

| 2.6 Basic modulation techniques for digital communication systems |    |

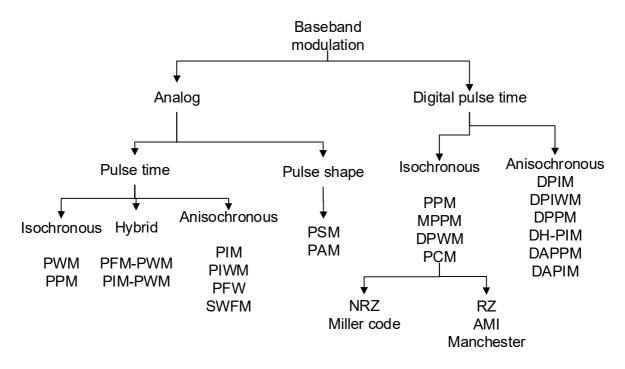

| 2.6.1 Baseband modulation tree                                    |    |

| 2.7 Pulse Position Modulation                                     |    |

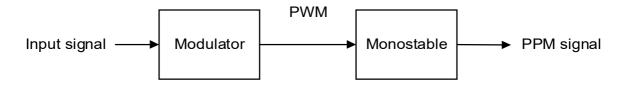

| 2.7.1 System model of PPM                                         |    |

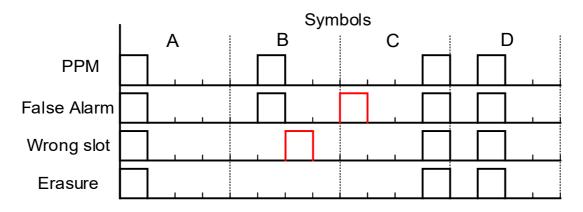

| 2.8 Types of errors in PPM schemes                                | 31 |

| 2.8.1 False Alarm                                                 |    |

| 2.8.2 Wrong Slot                                                  |    |

| 2.8.3 Erasure                                                     |    |

| 2.8.4 Intersymbol Interference                                    | 33 |

| 2.9 Standard for choosing modulation schemes                            |       |

|-------------------------------------------------------------------------|-------|

| 2.10 Summary                                                            |       |

| Chapter 3 Pulse Position Modulation Schemes                             |       |

| 3.1 Introduction                                                        |       |

| 3.2 Digital PPM (DPPM)                                                  |       |

| 3.3 Multipulse PPM (MPPM)                                               |       |

| 3.4 Offset PPM (OPPM)                                                   |       |

| 3.5 Dicode PPM (DiPPM)                                                  |       |

| 3.6 Duobinary PPM (DuoPPM)                                              | 40    |

| 3.7 Priority Decoding for OPPM- a novel method for improving BER in OPF | ۲M 41 |

| 3.7.1 Limitations                                                       |       |

| 3.7.2 Evaluation methodology                                            |       |

| 3.8 Modified MPPM- a novel modified form of MPPM to reduce bandwidth ex | -     |

| 3.8.1 Limitations                                                       |       |

| 3.8.2 Evaluation methodology                                            | 45    |

| 3.9 Summary                                                             | 45    |

| Chapter 4 VLC principle and experimental setup                          |       |

| 4.1 Introduction                                                        |       |

| 4.2 Applications of VLC                                                 |       |

| 4.3 Advantages of VLC                                                   |       |

| 4.4 VLC principle and system description                                |       |

| 4.5 Basic elements of VLC system                                        |       |

| 4.5.1 Physical layer (modulation/demodulation)                          |       |

| 4.5.2 LED                                                               |       |

| 4.5.3 Photodiode                                                        |       |

| 4.6 Experimental setup                                                  |       |

| 4.7 Receiver circuit design                                             | 51    |

| 4.7.1 Photodiode selection                                              | 51    |

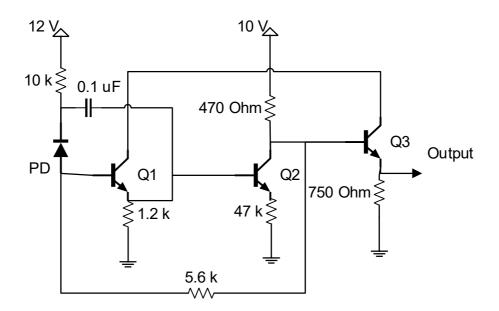

| 4.7.2 Design of TIA                                                     | 52    |

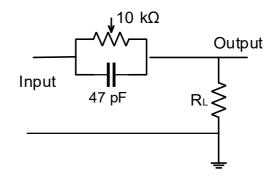

| 4.7.3 Compensator design                                                |       |

| 4.7.4 Comparator circuit design                                         |       |

| 4.7.5 Selection of LED                                                  |       |

| 4.8 FPGA testbench and HIL approach                                     | 55    |

| 4.9 Summary                                                             | 56    |

| Chapter 5 Design and System Implementation of PPM schemes                          | . 57 |

|------------------------------------------------------------------------------------|------|

| 5.1 Introduction                                                                   | . 57 |

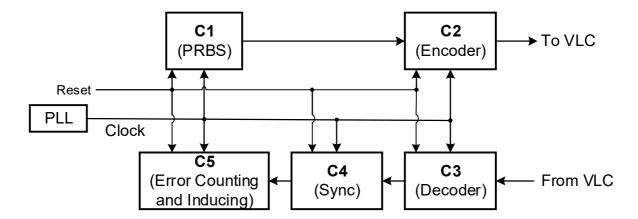

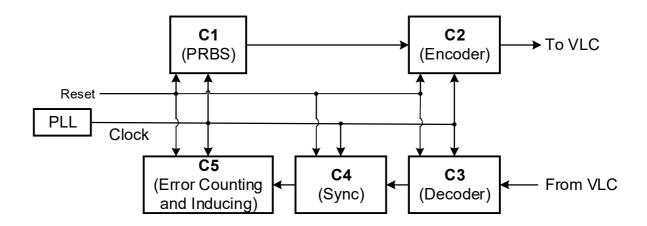

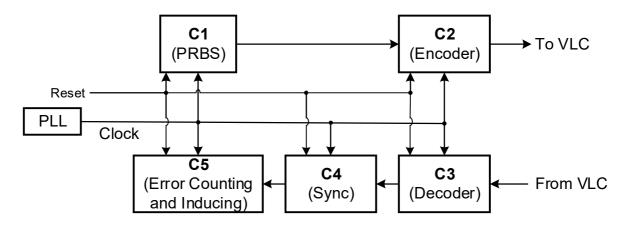

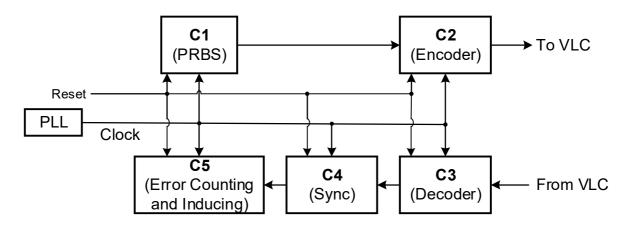

| 5.2 A typical PPM scheme design                                                    | . 57 |

| 5.2.1 PRBS module                                                                  | . 60 |

| 5.2.2 Synchronisation module                                                       | . 61 |

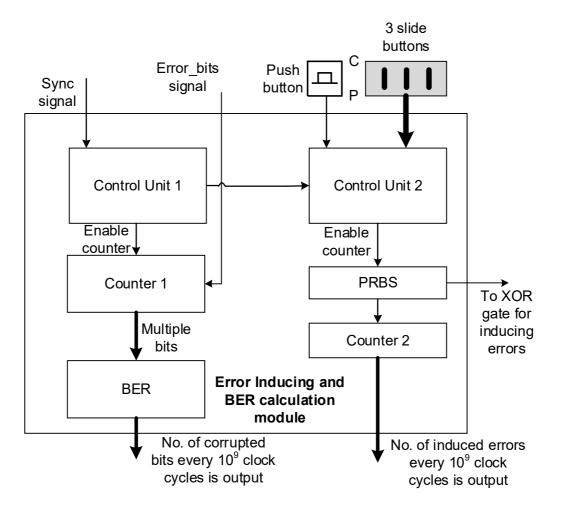

| 5.2.3 Error Inducing and BER calculation module                                    | . 61 |

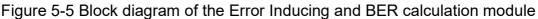

| 5.3 Full Testbench Design and Implementation on FPGA                               | . 62 |

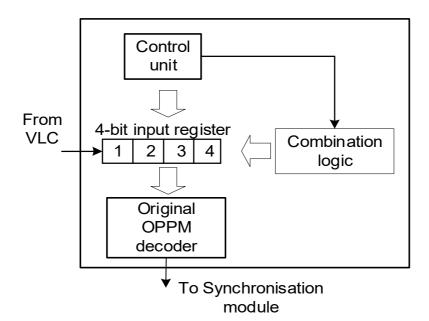

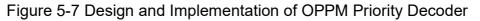

| 5.4 Design and Implementation of Priority Decoder for OPPM                         | . 64 |

| 5.5 Design and Implementation of CRC and Parity check with Modified MPPM64<br>FPGA |      |

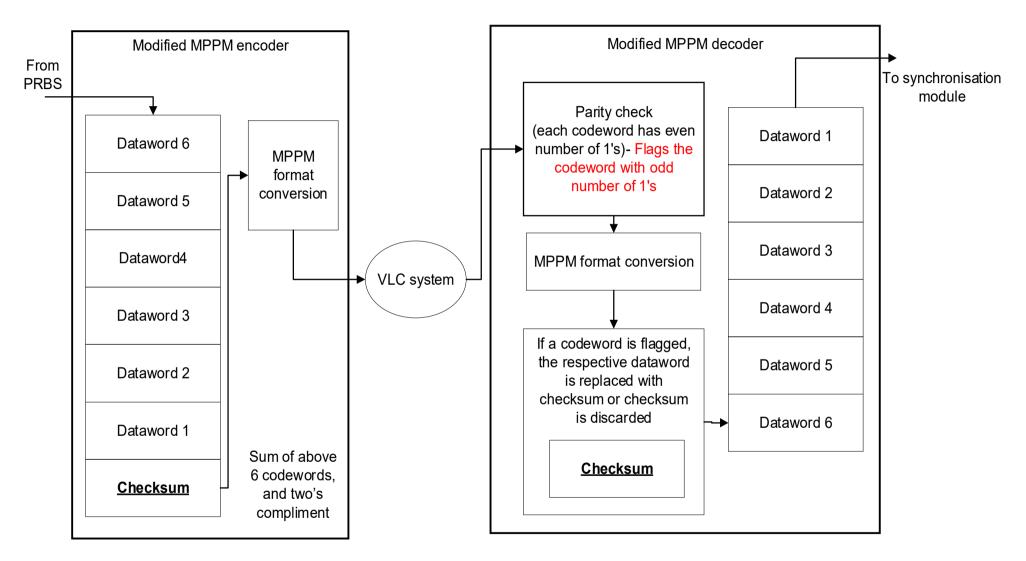

| 5.6 Design and Implementation of MLSD decoder                                      | . 67 |

| 5.7 Design and Implementation for power estimation of any given PPM                | . 68 |

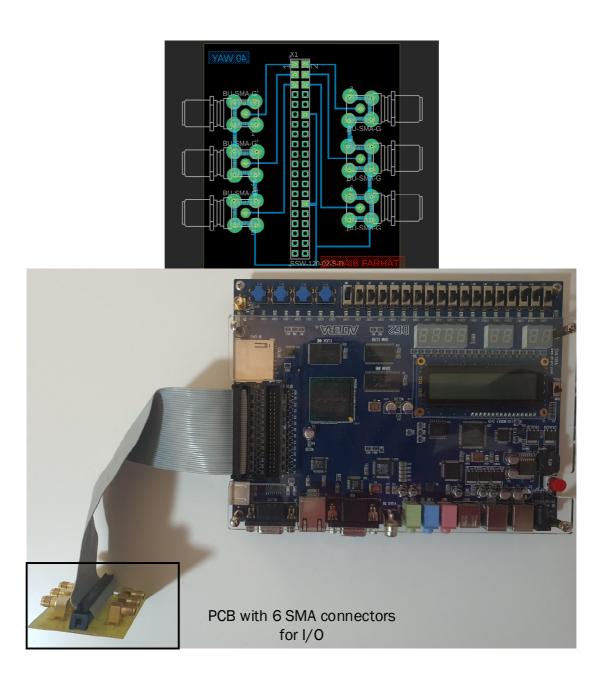

| 5.8 Development kit and Programming language                                       | . 69 |

| 5.9 Summary                                                                        | . 69 |

| Chapter 6 Results and Discussions                                                  | . 70 |

| 6.1 Introduction                                                                   | . 70 |

| 6.2 System testbench                                                               | . 70 |

| 6.3 Priority decoding OPPM                                                         | . 73 |

| 6.4 Modified MPPM                                                                  | . 75 |

| 6.4.1 Modified MPPM with CRC and Parity check                                      | . 77 |

| 6.5 MLSD                                                                           | . 79 |

| 6.6 Other tests                                                                    | . 81 |

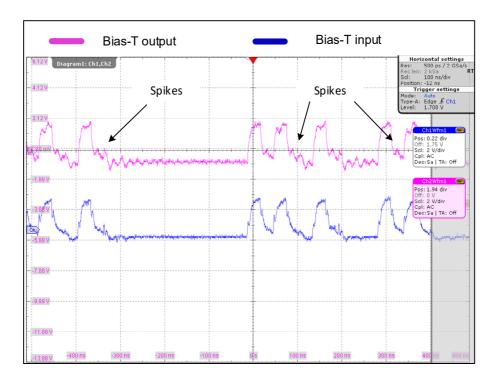

| 6.6.1 Bias-Tee                                                                     | . 81 |

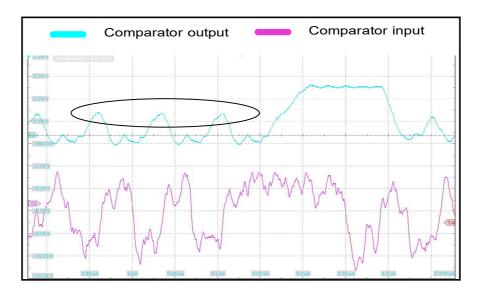

| 6.6.2 Comparator                                                                   | . 82 |

| 6.6.3 FPGA PLL signal                                                              | . 83 |

| 6.6.4 Types of errors detected                                                     | . 84 |

| 6.7 Summary                                                                        | . 84 |

| Chapter 7 Conclusion and Future Work                                               | . 86 |

| 7.1 Conclusions                                                                    | . 86 |

| 7.2 Future Work and recommendations                                                | . 89 |

| References                                                                         | . 91 |

| Appendices                                                                         | . 98 |

| Appendix A                                                                         | . 98 |

| Appendix B                                                                         | . 99 |

| Appendix C                                                                         | 100  |

| 107 |

|-----|

| 115 |

| 121 |

| 127 |

| 130 |

|     |

| 139 |

|     |

|     |

|     |

|     |

# List of Figures

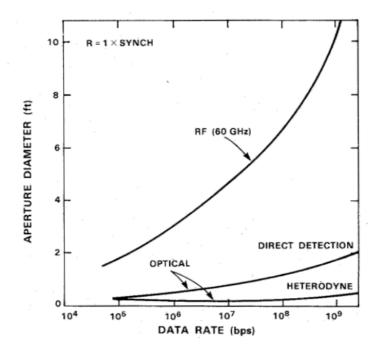

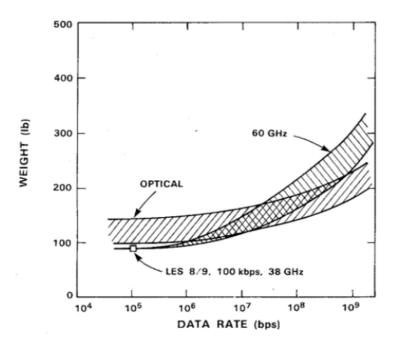

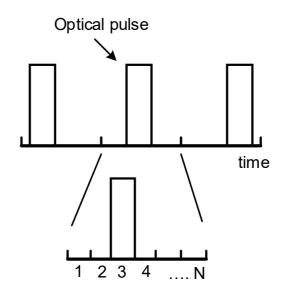

| Figure 1-1 A typical PPM based communication system       18         Figure 2-1 Communication architecture by Shannon [36]       24         Figure 2-2 Aperture diameter vs data rate of different systems. Reproduced from: [46]       26         Figure 2-3 Weight comparison of different systems vs data rate. Reproduced from: [46]       26         Figure 2-4 Baseband modulation tree [53]       29         Figure 2-5 PPM system model. Reproduced from [67]       30         Figure 2-6 Different types of signal format compared to PPM [68]       31         Figure 2-8 Intersymbol interference: A- signal before ISI; B- signal after ISI effect.       33         Figure 2-9 Optical pulse. Reproduced from [22]       34         Figure 3-1 PCM to DiPPM conversion [79]       40         Figure 3-2 PCM to DuoPPM conversion [80]       41 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 26Figure 2-3 Weight comparison of different systems vs data rate. Reproduced from:[46][46]26Figure 2-4 Baseband modulation tree [53]29Figure 2-5 PPM system model. Reproduced from [67]30Figure 2-6 Different types of signal format compared to PPM [68]31Figure 2-7 Error sources in PPM schemes [53]32Figure 2-8 Intersymbol interference: A- signal before ISI; B- signal after ISI effect.Reproduced from [72]33Figure 2-9 Optical pulse. Reproduced from [22]34Figure 3-1 PCM to DiPPM conversion [79]                                                                                                                                                                                                                                                                                                                                                |

| [46]26Figure 2-4 Baseband modulation tree [53]29Figure 2-5 PPM system model. Reproduced from [67]30Figure 2-6 Different types of signal format compared to PPM [68]31Figure 2-7 Error sources in PPM schemes [53]32Figure 2-8 Intersymbol interference: A- signal before ISI; B- signal after ISI effect.Reproduced from [72]33Figure 2-9 Optical pulse. Reproduced from [22]34Figure 3-1 PCM to DiPPM conversion [79]40                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Figure 2-4 Baseband modulation tree [53]29Figure 2-5 PPM system model. Reproduced from [67]30Figure 2-6 Different types of signal format compared to PPM [68]31Figure 2-7 Error sources in PPM schemes [53]32Figure 2-8 Intersymbol interference: A- signal before ISI; B- signal after ISI effect.Reproduced from [72]33Figure 2-9 Optical pulse. Reproduced from [22]34Figure 3-1 PCM to DiPPM conversion [79]40                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Figure 2-5 PPM system model. Reproduced from [67]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

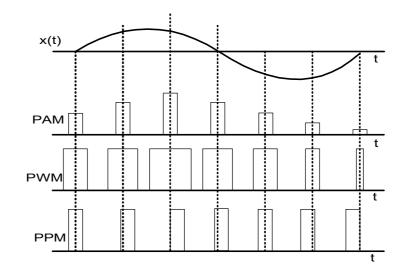

| Figure 2-6 Different types of signal format compared to PPM [68]31Figure 2-7 Error sources in PPM schemes [53]32Figure 2-8 Intersymbol interference: A- signal before ISI; B- signal after ISI effect.Reproduced from [72]33Figure 2-9 Optical pulse. Reproduced from [22]34Figure 3-1 PCM to DiPPM conversion [79]40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Figure 2-7 Error sources in PPM schemes [53]32Figure 2-8 Intersymbol interference: A- signal before ISI; B- signal after ISI effect.Reproduced from [72]33Figure 2-9 Optical pulse. Reproduced from [22]34Figure 3-1 PCM to DiPPM conversion [79]40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

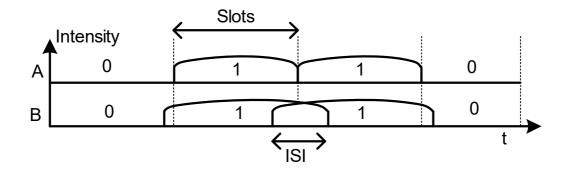

| Figure 2-8 Intersymbol interference: A- signal before ISI; B- signal after ISI effect.Reproduced from [72]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Reproduced from [72]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

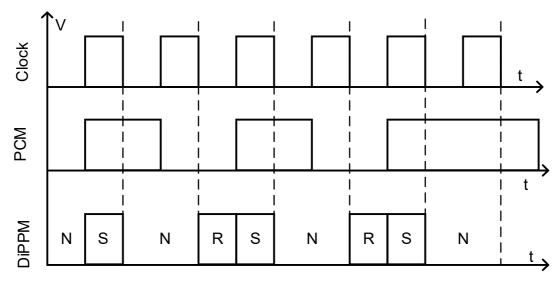

| Figure 3-1 PCM to DiPPM conversion [79]40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Figure 3-1 PCM to DiPPM conversion [79]40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

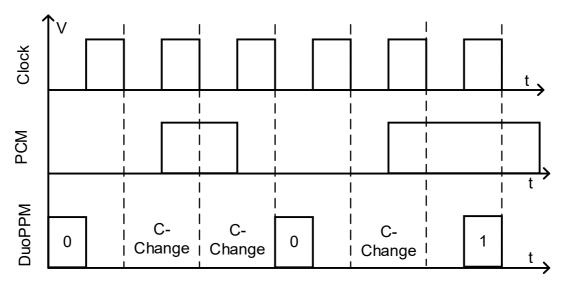

| Figure 3-2 PCM to DuoPPM conversion [80]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Figure 3-3 OPPM conversion format                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

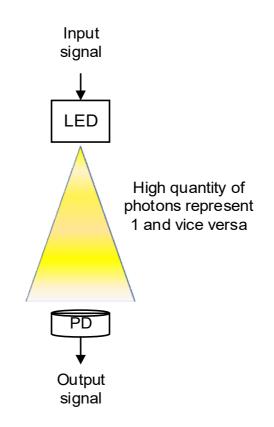

| Figure 4-1 Visible Light Communications principle [45]48                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

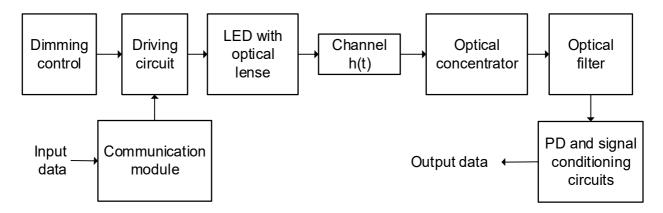

| Figure 4-2 Block diagram of a VLC system [53] 48                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

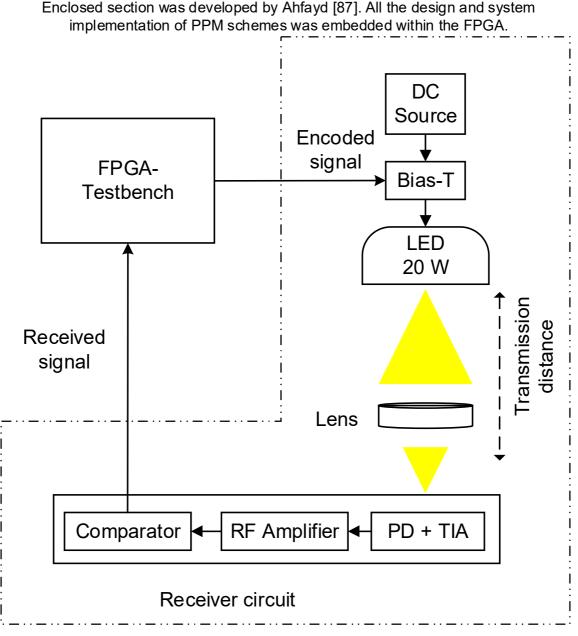

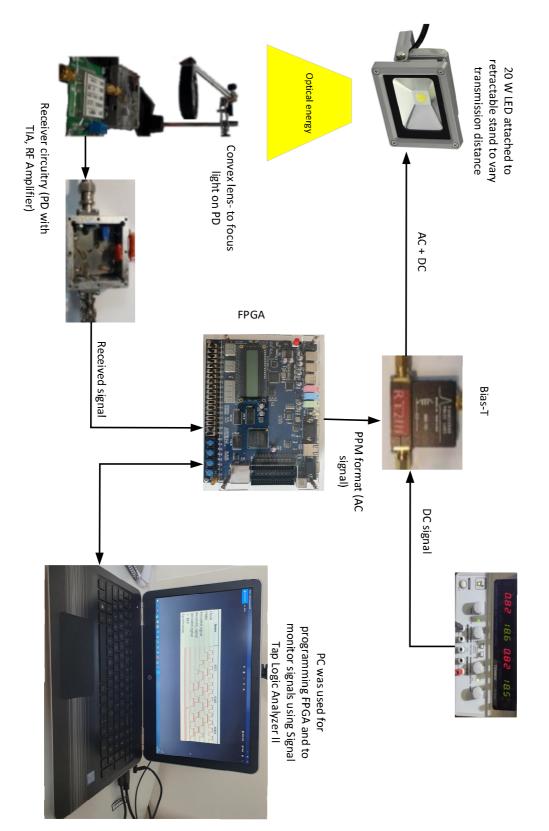

| Figure 4-3 Experimental link used in this research                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

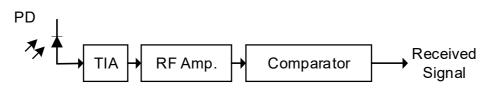

| Figure 4-4 Receiver circuitry51                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

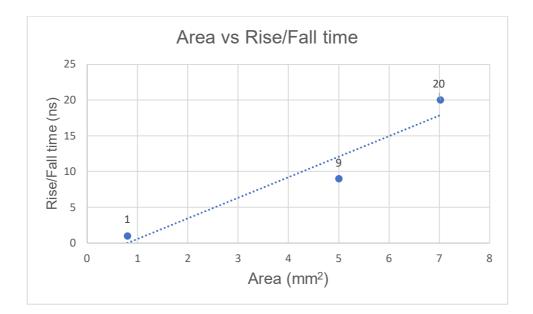

| Figure 4-5 PD area vs rise and fall time comparison52                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Figure 4-6 TIA circuit design52                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

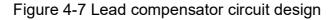

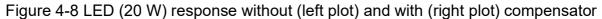

| Figure 4-7 Lead compensator circuit design53                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

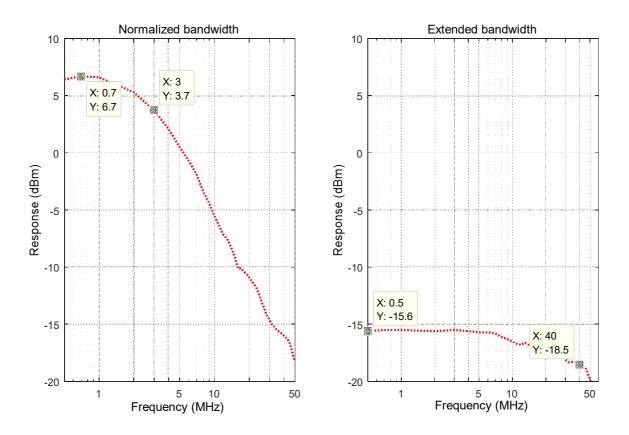

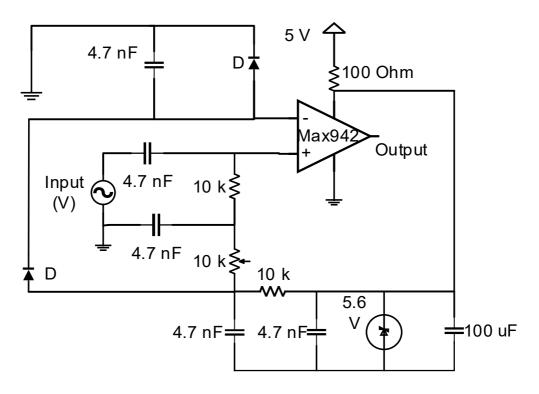

| Figure 4-8 LED (20 W) response without (left plot) and with (right plot) compensator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Figure 4-9 Comparator circuitry with Max942                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

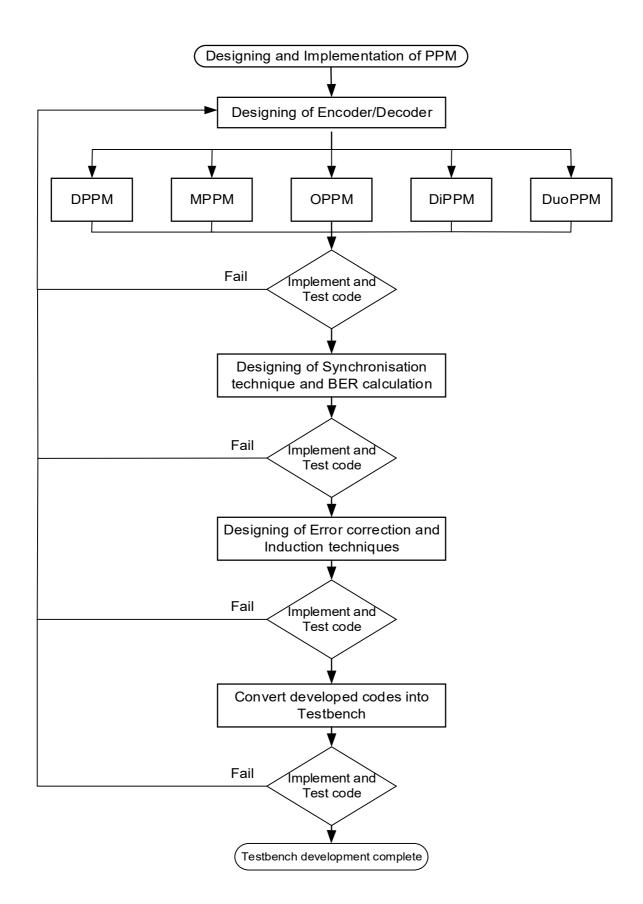

| Figure 5-1 Flowchart of designing and system implementation of PPM schemes 59                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

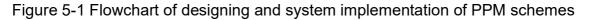

| Figure 5-2 A typical PPM design for FPGA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

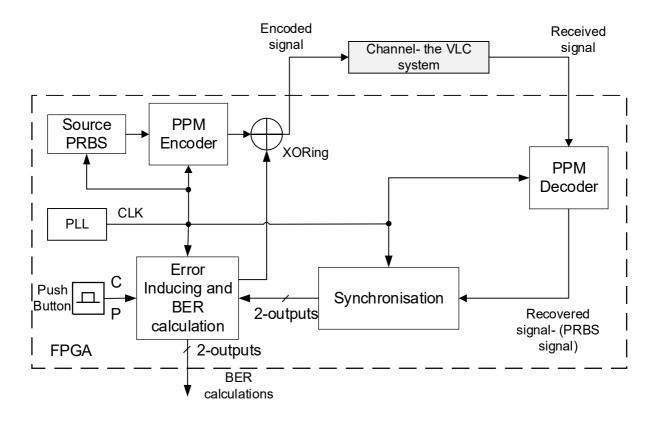

| Figure 5-3 Block diagram of PRBS module                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

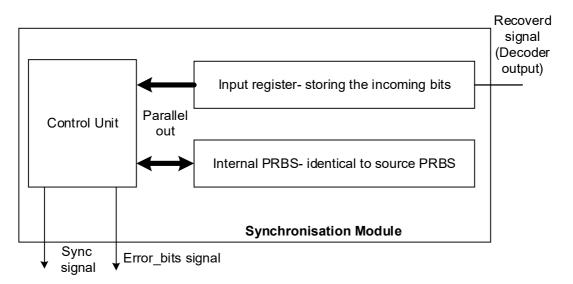

| Figure 5-4 Block diagram of the synchronisation module                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Figure 5-5 Block diagram of the Error Inducing and BER calculation module                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

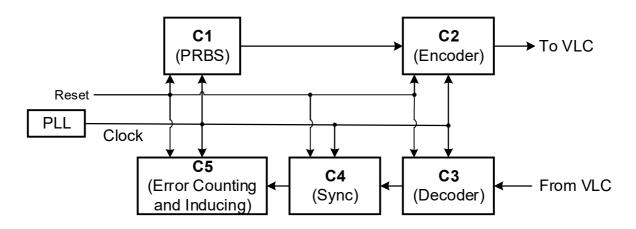

| Figure 5-6 Block diagram of developed full Testbench                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Figure 5-8 Design and Implementation of CRC and Parity check with Modified MPPM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

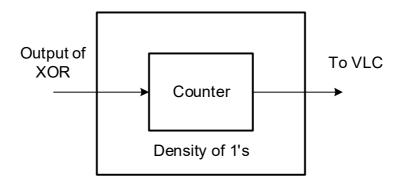

| Figure 5-10 Design and Implementation of Power Estimation for given PPM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

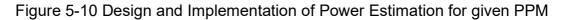

| Figure 6-1 BER vs Distance measurements using Full testbench setup                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

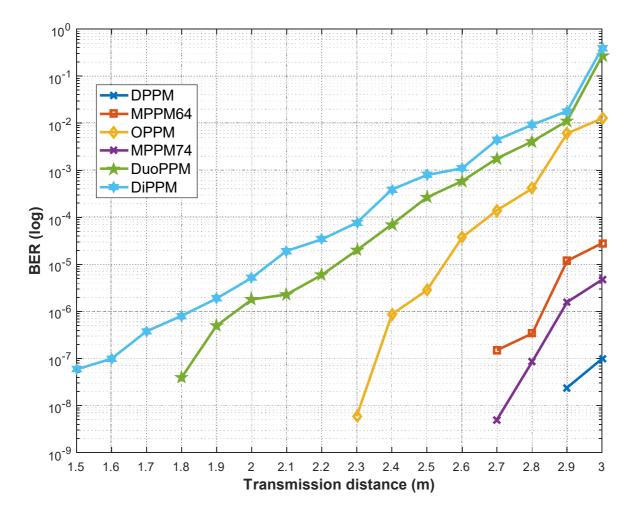

| Figure 6-2 BER vs Data Rate measurements using full testbench setup                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Figure 6-3 OPPM and OPPM Priority Decoding BER comparison [100]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

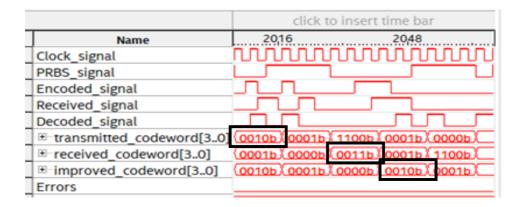

| Figure 6-4 Priority decoding OPPM error corrections                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Figure 6-5 MPPM vs Modified MPPM BER comparison                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Figure 6-6 Modified MPPM with CRC and Parity check                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

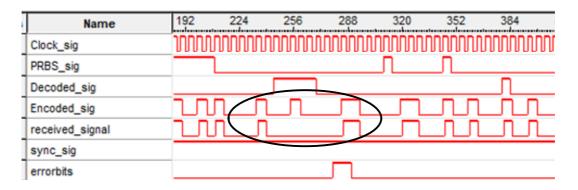

| Figure 6-7 Signal simulations of MPPM with CRC and parity check                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Figure 6-8 DiPPM and DiPPM MLSD BER comparison                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Figure 6-9 MLSD DiPPM signal simulations                  | 81 |

|-----------------------------------------------------------|----|

| Figure 6-10 Bias-T output and input signals               | 82 |

| Figure 6-11 Comparator input and output signal waveforms  | 83 |

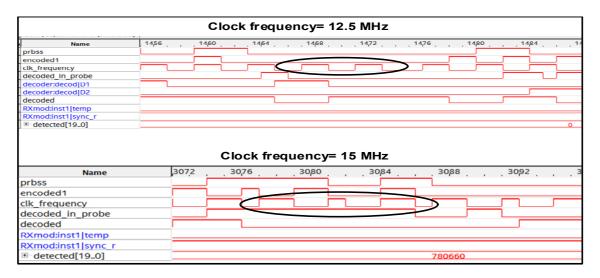

| Figure 6-12 PLL clock signal at 12.5 MHz and 15 MHz       | 83 |

| Figure 6-13 ISI detected in the received signal           | 84 |

| Figure 6-14 Erasure error detected at the received signal |    |

# List of Tables

| Table 1-I Electromagnetic spectrum [3]                                 | . 16 |

|------------------------------------------------------------------------|------|

| Table 3-I DPPM symbol format                                           | . 37 |

| Table 3-II MPPM symbol format                                          | . 38 |

| Table 3-III OPPM symbol format                                         | . 39 |

| Table 3-IV DiPPM symbol format                                         | . 39 |

| Table 3-V DuoPPM symbol format                                         | . 40 |

| Table 3-VI PCM to OPPM and DPPM conversion                             | . 42 |

| Table 3-VII OPPM with Priority Decoding method                         | . 43 |

| Table 3-VIII MPPM and Modified MPPM comparison                         | . 44 |

| Table 4-I Different types of PD [88-90]                                | . 51 |

| Table 4-II Comparators specifications[92, 93]                          | . 54 |

| Table 4-III Comparison between different types of LEDs [94]            | . 55 |

| Table 5-I MLSD control and correction technique                        | . 67 |

| Table 6-I PRBS rates for fixed line rate                               | .71  |

| Table 6-II Power and bandwidth comparisons of different PPM schemes    | . 73 |

| Table 6-III OPPM vs OPPM with Priority Decoding                        | . 75 |

| Table 6-IV Line rates of original and modified MPPM                    | . 76 |

| Table 6-V Original and Modified MPPM comparison                        | . 76 |

| Table 6-VI Modified MPPM with CRC and parity check line and data rates | . 78 |

| Table 6-VII DiPPM and DuoPPM MLSD comparison                           | . 80 |

| Table 7-I Weighted sum approach for PPM selection                      | . 87 |

# List of Abbreviations

| AMI:    | Alternate Mark Inversion                             |

|---------|------------------------------------------------------|

| BER:    | Bit-Error Rate                                       |

| DAPIM:  | Dual Amplitude and Pulse Interval Modulation         |

| DPWM:   | Discontinuous Pulse Width Modulation                 |

| DAPPM:  | Differential Amplitude and Pulse Position Modulation |

| DH-PIM: | Dual-Header Pulse Interval Modulation                |

| DPIM:   | Digital Pulse Interval Modulation                    |

| DPIWM:  | Digital Pulse Interval and Width Modulation          |

| DiPPM:  | Dicode PPM                                           |

| DPPM:   | Digital PPM                                          |

| DuoPPM: | Duobinary PPM                                        |

| FA:     | False Alarm                                          |

| HD:     | Heterodyne Detection                                 |

| HIL:    | Hardware-in-the-loop                                 |

| IMDD:   | Intensity Modulation with Direct Detection           |

| ISI:    | Inter-symbol Interference                            |

| ITU:    | International Telecommunication Union                |

| LOS:    | Line-of-sight                                        |

| MDPIM:  | Modified Digital Pulse Interval Modulation           |

| MPPM:   | Multiple Pulse Position Modulation                   |

| MLSD:   | Maximum Likelihood Sequence Detection                |

| NRZ:    | Non-Return to Zero                                   |

| OOK:    | On-Off Keying                                        |

|         |                                                      |

| OPPM: | Offset PPM                       |

|-------|----------------------------------|

| PAM:  | Pulse Amplitude Modulation       |

| PCM:  | Pulse Code Modulation            |

| PD:   | Photodiode                       |

| PFM:  | Pulse-Frequency Modulation       |

| PIWW: | Pulse Interval Width Modulation  |

| PPM:  | Pulse Position Modulation        |

| PSM:  | Pulse Shift Modulation           |

| PRBS: | Pseudo-Random Binary Sequence    |

| RZ:   | Return to Zero                   |

| SWFM: | Square-wave Frequency Modulation |

| SNR:  | Signal to Noise Ratio            |

| TIA : | Trans-impedance preamplifier     |

| VLC:  | Visible Light Communication      |

| VPPM: | Variable PPM                     |

# Chapter 1 Introduction

#### **1.1 Introduction**

Data communication plays an important role in daily life through emails, texts, social media and calls etc. Humans exchange data daily and the technology used in the transmission of information from one point to another is called a communication system. There are mainly two types of communication systems i.e., analogue and digital. In an analogue communication system, a continuous signal is transmitted from A to B; examples of analogue signals are voice and video signals such as Television signals. A signal in the form of an analogue signal is multiplied with a carrier signal, with different frequency, and transmitted. Analogue communication has seen a decline in recent years due to cost and space, as it requires relatively larger physical receivers and transmitters. In the digital communication system, a stream of 1's and 0's, often called a symbol, is transmitted. The sequence of 1's and 0's typically are formatted to represent information consisting of audio, video, textual or a combination of all. However, digital communication uses standard electronics and software for the transmission and reception of data which are relatively cheaper and easy to replace. Applications of digital communication systems mainly include optical fibre and optical wireless systems. [1, 2].

From the electromagnetic spectrum, given in table 1-I, the sources of Radio waves and Microwave include AM radio towers, TV and FM radio towers, mobile phones and towers [3]. Electromagnetic spectrum with frequencies ranging from 3 kHz to 300 GHz, also called Radio Frequency (RF) waves, are used in analogue communication systems. Conventional RF bands are used for broadcasting commercial television, radio and wireless communications. There are a limited number of RF bands available for broadcasting and communication purposes. Therefore, RF is becoming expensive and overcrowded. If two systems are using the same frequency band, over a shared communication channel such as air, both systems will suffer from distortion and noise due to superposition and destructive interference. Hence, RF bands are highly regulated by national laws and international telecommunication union (ITU), preventing interference between bands [4, 5]. However, optical wireless systems remain unregulated leading to becoming a trending topic in the field of communications.

| Common name         | Frequency range    |

|---------------------|--------------------|

| Radio and Microwave | 3 Hz to 300 GHz    |

| Infrared            | 300 GHz to 430 THz |

| Visible light       | 430 THz to 790 THz |

| Ultraviolet         | 790 THz to 30 PHz  |

| X-ray               | 30 PHz to 30 EHz   |

| Gamma rays          | >30 EHz            |

Table 1-I Electromagnetic spectrum [3]

Optical systems use laser or light-emitting diodes (LEDs) to transmit information, by varying the intensity of the signal. LEDs have a frequency range of 430 THz to 790 THz [3]. Despite the frequencies in hundreds of THz, the possible biological effects on the human body due to optical communications may include tissue damage and damage to the immune system, which are far below the threshold levels when compared with the RF systems. These possible biological effects due to optical systems occur when an optical transmitter is applied with very high power, which is not usually applied near humans. On other hand, continuous or daily exposure to electromagnetic or RF waves may lead to chromosomal damage or DNA errors which may result in cancer [6-8]. Some optical systems based on LEDs, also known as Visible Light Communication (VLC) system, can be used for illumination purposes. On other hand, RF systems are only used for communication purposes. Optical wireless communication consisting of laser beams can provide extremely high-speed transmission rates in line of sight (LOS) systems when compared with RF [9]. In LOS, RF waves or optical energy travels in a direct path from the transmitter to the receiver. Considering above mentioned advantages of optical systems over RF, researchers are trying to develop an alternative system that can replace RF.

There is a continuous demand to achieve higher data rates and longer transmission distance in optical communications. Researchers seek to improve the transmission rates of communication systems in every possible way including integrated circuits, signal modulation techniques and physical links used for

16

transmission. To reduce interference, researchers propose different methods for efficient transmission of information including modulation techniques, receiver designs and channel optimisations [2]. Usually, an ideal channel in any optical system with no external interference or noise and with LOS can achieve optimal performance. It is not possible to achieve a perfect noiseless channel with zero losses in the real world, due to interference from surroundings like weather or walls of a building, this can reduce signal intensity. A modulation scheme plays an integral role in the performance of an optical system, a modulation scheme must use any given channel and achieve the optimum possible performance. Several modulation schemes are used with optical systems such as Pulse Amplitude Modulation (PAM), Pulse Position Modulation (PPM), Pulse Interval modulation (PIM) and Orthogonal frequency division multiplexing (OFDM) [10]. PPM is considered an attractive and widely used method of signal modulation in optical communications. There are several variations of PPM, e.g., Digital PPM (DPPM), Multi-pulse PPM (MPPM) etc. A PPM scheme uses the available bandwidth of the channel to achieve good performance in terms of sensitivity and error rates. VLC and other optical systems are susceptible to ambient light noise, high signal attenuation, and Intersymbol interference (ISI). ISI results in the deformation of the signal when one symbol or pulse interferes with the adjacent symbol or pulse. High optical power levels are one way to overcome these errors [11]. However, high optical power levels are not desirable in optical systems, for example, a portable system with batteries or an energy-efficient system running on low power. High optical power is also not desirable for the human eye as this could result in retina damage, hence, due to health and safety reasons only limited optical power can be applied to an optical system [12, 13].

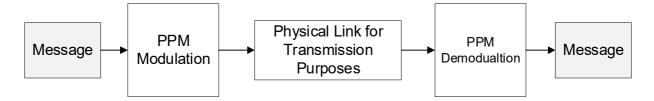

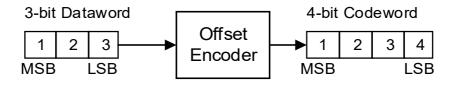

DPPM is considered the most appropriate modulation method in optical systems, due to the low mark:space ratio and low average power of the transmitted signal [12, 14]. In PPM, a message is transmitted by positioning a single pulse or pulses in fixed time duration. Signal modulation plays a prime role in the overall performance of an optical communication system. A typical PPM scheme is given in figure 1-1. A message or data is encoded into the PPM format at the transmitter end before transmission and decoded back into the original message at the receiver end.

17

Figure 1-1 A typical PPM based communication system

## **1.2 Different types of PPM schemes**

DPPM was proposed to utilize the bandwidth available in optical fibre and wireless systems. DPPM showed 5-11 dB improvement in the sensitivity when compared with pulse code modulation (PCM) [15]. The level of sensitivity reveals the weakest signal which will be detected by the receiver, the sensitivity of a receiver can be increased by improving the bandwidth and reducing the noise level [16]. The PCM represents the sampled analogue signal in a digital form. DPPM has been widely investigated by researchers, the only drawback DPPM offers is the large bandwidth expansion. PPM trades the bandwidth for improved sensitivity and low average power. To transmit mbits in DPPM format, 2<sup>m</sup> bits are required [17-21]. With the demand for data growing fast, DPPM is not suitable where limited bandwidth is available. If m=3, 8-bits are required to transmit 3-bits of data. To overcome the large bandwidth expansion, researchers have been proposing alternate PPM schemes with improved bandwidth utilization. The ideal modulation scheme must offer low average power, improved sensitivity and a reduced bandwidth expansion. However, each proposed PPM scheme inevitably comes with its advantages and disadvantages. DPPM was the earliest scheme to be investigated, which offered better average power and sensitivity than On-Off Keying (OOK) [17]. OOK is another widely investigated scheme for optical systems. OOK is the simplest form of PAM, a binary one is represented by a high voltage level, and binary zero with a low voltage level. To overcome the large bandwidth expansion and minimise average power many alternate PPM schemes were proposed. To name a few well-known PPM schemes, a list is given below:

- Multiple PPM (MPPM) [22]

- Digital Pulse Interval Modulation (DPIM) [11]

- Dual Header Pulse Interval Modulation (DH-PIM) [23]

- Offset PPM (OPPM) [24]

- Dicode PPM (DiPPM) [25]

- Duobinary PPM (DuoPPM) [26]

- Variable PPM (VPPM) [27]

- Overlapping PPM [28]

Furthermore, hybrid schemes have been proposed based on the above mentioned schemes, a hybrid scheme involves the combination of multiple modulation schemes. For example, a hybrid modulation called hybrid binary phase-shift keying modified MPPM (hybrid BPSK-modified MPPM) was proposed to improve the performance of a binary phase-shift keying (BPSK) and MPPM for optical fibre systems [29]. A hybrid PPM scheme is usually more complicated than the parent PPM scheme and results in a complex modulation/demodulation process and transmitter/receiver circuits [30]. Usually, each scheme is proposed and recommended based on the theoretical analysis. Since the DPPM proposal in the 80s, there has been a great interest in overcoming the large bandwidth expansion problems of DPPM, this has led to the discovery of many alternate and hybrid PPM schemes. However, there is very little evidence focusing on practicality and implementation concerning real-world scenarios [31-34].

### **1.2.1 Motivation and Novel aspects of the research**

The motivation for this research comes from the insufficient published evidence of existing schemes in terms of practical implementation and measurements. The practical implementation is principally overlooked, and proposals are being based on theoretical calculations and equations. This research is an undertaking to fill this gap, along with Hardware-in-the-loop (HIL) experimentation approach which can be used to evaluate the performance of the given PPM schemes without the physical link. The most effective way to test and evaluate a PPM scheme is to implement it over a physical link. However, in some cases practical implementation is not possible in laboratory based environment, due to limited resources or to reduce cost and development time. HIL approach can be applied in such cases before implementing it over the practical system. HIL can also be applied to enhance the quality of testing, reduce development time and reduce time-to-market. In this research, a testbench serves the purpose of implementing the individual PPM schemes, enabling the performance measurement of the schemes under uniform system parameters to be evaluated. Furthermore, this testbench will be able to simulate the characteristics of a real physical link such as inducing targeted or random errors using a pseudo-random binary sequence generator (PRBS).

In this research, a range of PPM schemes were studied and investigated over an identical communication system configuration using a developed testbench. This resulted in an enhanced understanding of PPM schemes and VLC circuitry, enabling the performance features of a given digital communication system to be investigated and validated.

Several of the PPM schemes, to the author's knowledge, were first time practically implemented and studied in a research environment. Meanwhile, this implementation also provided support in the investigation and improvement of the practical VLC circuitry. A novel PPM scheme, called Priority decoding, for error correction in OPPM, was also proposed. Furthermore, a modified form of MPPM called modified MPPM (MPPM64), was proposed which requires reduced bandwidth for data transmission, resulting in improved system efficiency. Error correction using MLSD, CRC and parity check techniques are also investigated and results analysed.

### 1.3 Aims

Modulation schemes play key role in the performance of any communication system and PPM schemes have always been traditionally identified as the most appropriate schemes for optical communication systems [35]. This research aims to develop a test bench to investigate, measure and enhance the performance of different PPM schemes. The developed test bench will be practically implemented over a VLC system incorporating a High Power LED light. For enhancement of PPM schemes, different error correction techniques are implemented such as CRC, Parity check, MLSD and Priority decoding.

One of the key aspects of the research was practically implementing and comparing different schemes on an identical system to identify the optimal scheme for a given VLC or any optical system. The developed test bench is scalable to add more modulation schemes and features for more comprehensive analysis in future.

#### 1.4 Objectives

In achieving the research aim following objectives were identified:

- Investigate and gather information on different modulation schemes, with a particular focus on PPM modulation schemes used for optical communication systems.

- Identify the gaps in PPM studies regarding practical implementation.

- Investigate different PPM schemes and study the advantages and disadvantages of the schemes.

- Develop VHDL codes for different PPM schemes including DPPM, MPPM, OPPM, DiPPM and DuoPPM, to encode and decode PCM into respective PPM format.

- Design a synchronization technique using VHDL, to synchronise the incoming data from the receiver.

- Develop error detection and counting system using VHDL, to identify the total number of corrupted bits, one of the most important information when comparing modulation schemes.

- Convert developed codes into a testbench, to allow comparison and validation under identical conditions. Practically, implement, test, debug and verify the correct operation of testbench over the VLC system using FPGA.

- Develop and implement error correction VHDL codes such as MLSD, parity check and CRC, to improve the overall efficiency of the communication system.

- Using the developed testbench, investigate and improve VLC hardware circuitry.

- Examine and identify the optimal PPM scheme for the VLC system implementations.

- Identify the optimal PPM schemes in terms of error rate and complexity.

# **1.5 Novel contributions**

The novel contributions of this research are;

- First-time practical implementation and practical analysis of OPPM, DiPPM and DuoPPM schemes.

- Implementing and evaluating the performance of multiple PPM schemes over a VLC system under identical system conditions.

- Proposing a modified version of the MPPM scheme to reduce bandwidth expansion.

- Proposing a novel method called Priority decoding to improve the BER of the OPPM scheme.

- Developing testbench using HIL approach, to test and evaluate the performance features of PPM schemes.

- Identifying VLC system component performance limitations and identifying the main sources of induced system errors.

- Future research direction recommendations have been made on the VLC system, test strategies and the novel proposed enhanced PPM schemes.

## **1.6 Thesis Structure**

- Chapter 1 gives an overview of the research aims and objectives, and identifies the gaps in previous research. This chapter also identifies the novelty of this research.

- **Chapter 2** gives the background information and history of communication systems. The importance of a modulation scheme in a communication system is discussed, including modulation schemes for optical systems.

- Chapter 3 Includes an introduction to the PPM scheme and its system model. This chapter includes a study of several types of PPM schemes identified and practised in this research. Two proposed novel schemes are discussed including modified MPPM64 and Priority decoding for OPPM.

- **Chapter 4** gives a detailed overview of a VLC system and its key components. The design of the VLC setup used in this research is discussed in this chapter.

- Chapter 5 includes designing and system implementation of different PPM schemes on FPGA over the VLC setup. Block diagrams of each modulation schemes and the test bench are included in this chapter.

- Chapter 6 includes Results and Discussions.

- **Chapter 7** contains conclusions and recommendations for future work.

## **Chapter 2**

## **Background and Literature Review**

#### **2.1 Introduction**

The reason behind why humans have become the most developed species is that humans produce data, store it on paper or in electronic gadgets, and trade. Particularly, the trade and dispersion of data have changed the way of life fundamentally. For example, before the phones were invented, to visit a place, one needed to plan the visit cautiously, from flight to the hotel booking and physically gather all this data about the location beforehand. After the invention of mobile phones, identical tasks can be done in minutes. Moreover, with the availability of Internet and mobile device user can check email or stock price wherever and whenever. This radical change in way of life is because of high-speed remote correspondence.

In early ages, smoke signals were used to transmit a message from one place to another place. However, the range was limited to visual distance and highly depended on weather conditions. There were also other forms of communication such as drums, carrier pigeons and the semaphore flags. These old forms of communications were highly unreliable. A Scottish physicist named C.J. Maxwell described the idea of electromagnetic waves between 1861 and 1862. To prove Maxwell's idea, a German physicist built an experimental setup in 1887, this proved the existence of electromagnetic waves. A French scientist, E. Brainly in the 1890s, invented a device consisting of a tube with two electrodes, this could detect electromagnetic waves. A revolution came in the communications field when a transistor was developed by Bell Labs. In 1954, a transistor-based radio system was developed, this was a portable wireless receiver [1, 36-38].

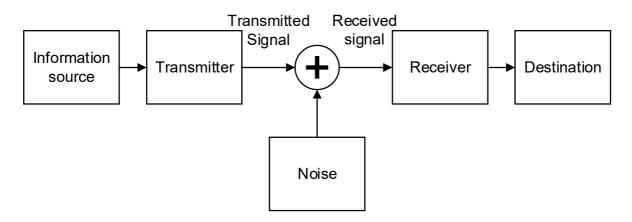

C. E. Shannon from Bell Labs, a scientist proposed the information theory which includes processing, extraction and utilisation of information. Shannon presented the idea of measuring the information and adopted the concept of Entropy from thermodynamics. Entropy in information theory means the level of uncertainty of a random variable. Shannon also defined the concept of channel capacity and designed the communication architecture. Channel capacity is defined as the maximum rate of reliable communications over a noisy channel. The communication architecture is

23

shown in figure 2-1, and this is used by all communication systems i.e., Wireline and Wireless communication systems [36, 39].

Figure 2-1 Communication architecture by Shannon [36]

#### 2.2 Types of communication systems