#### **University of Huddersfield Repository**

Mahmood, Faaiz Hadi

Implementation of Offset Pulse Position Modulation

#### **Original Citation**

Mahmood, Faaiz Hadi (2017) Implementation of Offset Pulse Position Modulation. Doctoral thesis, University of Huddersfield.

This version is available at http://eprints.hud.ac.uk/id/eprint/34409/

The University Repository is a digital collection of the research output of the University, available on Open Access. Copyright and Moral Rights for the items on this site are retained by the individual author and/or other copyright owners. Users may access full items free of charge; copies of full text items generally can be reproduced, displayed or performed and given to third parties in any format or medium for personal research or study, educational or not-for-profit purposes without prior permission or charge, provided:

- The authors, title and full bibliographic details is credited in any copy;

- A hyperlink and/or URL is included for the original metadata page; and

- The content is not changed in any way.

For more information, including our policy and submission procedure, please contact the Repository Team at: E.mailbox@hud.ac.uk.

http://eprints.hud.ac.uk/

# IMPLEMENTATION OF OFFSET PULSE POSITION MODULATION

## **FAAIZ HADI MAHMOOD**

A thesis submitted to The University of Huddersfield in partial fulfilment of the requirements for the degree of Doctor of Philosophy

The University of Huddersfield

February 2017

#### **Copyright Statement**

i. The author of this thesis (including any appendices and/or schedules to this thesis) owns any copyright in it (the "Copyright") and he has given The University of Huddersfield the right to use such Copyright for any administrative, promotional, educational and/or teaching purposes.

ii. Copies of this thesis, either in full or in extracts, may be made only in accordance with the regulations of the University Library. Details of these regulations may be obtained from the Librarian. This page must form part of any such copies made.

iii. The ownership of any patents, designs, trademarks and any and all other intellectual property rights except for the Copyright (the "Intellectual Property Rights") and any reproductions of copyright works, for example graphs and tables ("Reproductions"), which may be described in this thesis, may not be owned by the author and may be owned by third parties. Such Intellectual Property Rights and Reproductions cannot and must not be made available for use without the prior written permission of the owner(s) of the relevant Intellectual Property Rights and/or Reproductions.

#### Acknowledgment

All thanks and praises are due to Almighty God for granting me the wisdom, health and strength to undertake this research task and enabling me to its completion.

The work presented in this thesis would not have been possible without my close association with many people. I take this opportunity to extend my sincere gratitude and appreciation to all those who made this Ph.D. thesis possible.

First and foremost, I would like to extend my sincere gratitude to my research supervisor Dr. Martin Sibley for introducing me to this exciting field of science and for him dedicated help, advice, inspiration, encouragement and continuous support, throughout my Ph.D.

Special thanks are also given to Dr. Peter Mather, whose enthusiasm and technical guidance have been greatly appreciated, his encouragement and help made me feel confident with during my PhD course. Through his depth of knowledge and enthusiasm, he such as a spot light inspiration and enlightened my way in this project whenever I needed to help me whether in theoretical or practical investigation during this project.

I would like to express my special appreciation and thanks to present and past members of the School Research & Administration Office staff: Cathie Raw, Gwen Wood, Chris Sentence, Nicola Williams, Belinda Perfitt, and Liz Rees.

Nobody has been more important to me in the pursuit of this project than my parents. Words cannot express how grateful I am to my Mum, Dad, whose love and guidance are with me in whatever I pursue. They are the ultimate role models.

A special thanks to my younger sisters Dr. Ban, and Dr. Aseel, have all extended their support in a very special way, and I gained a lot from them, through their personal and scholarly interactions, their suggestions at various points of my research.

A special thanks to my brothers and sisters. Words cannot express how grateful I am to them. Your prayer for me was what sustained me thus far.

Most importantly, I Wish to thank my loving and supportive wife, Sarah, and my two wonderful children, Yusur, and Abdulhadi, Who provide unending inspiration.

Dr. Mothana Amaar Hassan was kind enough to undertake the editing work and I acknowledge the meticulous work he has done. Mothana, had finely sketched out the map of the study area, and I thank and appreciate his efforts.

I am grateful to Dr. Basman Monther Al-Nedawe for sharing his knowledge that influenced the work.

#### **Abstract**

Optical fibre systems have played a key role in making possible the extraordinary growth in world-wide communications that has occurred in the last 25 years, and are vital in enabling the proliferating use of the Internet. Its high bandwidth capabilities, low attenuation characteristics, low cost, and immunity from the many disturbances that can afflict electrical wires and wireless communication links make it ideal for gigabit transmission and a major building block in the telecommunication infrastructure.

The main concern of this thesis is a full and detailed investigation and implementation of the Offset Pulse Position Modulation (Offset PPM) communication system. Novel work is carried out for applying Offset PPM over an optical communication channel theoretically and experimentally to examine the system performance.

An Offset PPM encoder and decoder were implemented to code Pulse Code Modulation (PCM) format into Offset PPM format and to decode back the Offset PPM to PCM. The first paradigm of implementation was implemented using electronic components.

A further investigation took place on the Offset PPM associated output. Computer programming and simulation using the VHSIC Hardware Description Language (VHDL) of this PPM code was considered and comparison with previous theoretical results presented. The received Offset PPM signal returned back to its original input PCM form without errors.

Successful VHDL and Field Programmable Gate Array (FPGA) implementation using Altera Quartus II of Offset PPM encoder and decoder as a single system has been presented in the study. An FPGA embedded Bit Error Rate (BER) test device has also been implemented for sensitivity measurements purposes and all the designs have been tested successfully with back-to-back testing. Results show that Offset PPM is an advantageous PPM code for optic communication. Furthermore, the system has achieved a very high data rate of 50 Mb/s without an optical communication set.

An optical communication system (transmitter/receiver) over POF was developed and the Offset PPM scheme was investigated through this optical channel. Results show that the Offset PPM sequence transferred through the optic system without being altered. In addition, this implementation is optimised PPM coding; the system is working perfectly with up to 10 Mb/s with  $10^{-12}$  BER based on the limitations of the optical communication set.

All the results and analyses indicate that Offset PPM is an ideal alternative to be considered for highly dispersive optical channels, and performance evaluation for higher bandwidths also favourably compares to existing coding schemes.

# **List of Contents**

| Abstra     | nct                                                  | III |

|------------|------------------------------------------------------|-----|

| List of    | Contents                                             | V   |

| List of    | Figures                                              | IX  |

|            | Tables                                               |     |

|            | Abbreviations                                        |     |

|            |                                                      |     |

|            | ntroduction                                          |     |

| 1.1        | Optical Communication Background                     |     |

| 1.2        | Features of Fibre Optic Communication Systems        |     |

| 1.         | 2.1 Advantages                                       | 4   |

| 1.         | 2.2 Disadvantages                                    | 6   |

| 1.3        | Aims and Objectives                                  | 8   |

| 1.4        | Contributions                                        | 9   |

| 1.5        | Organization of the Thesis                           | 10  |

| 2 Li       | iterature Review                                     | 12  |

| 2.1        | Introduction                                         | 12  |

| 2.2        | Coding Schemes in Optical Fibre Communication System | 12  |

| 2.3        | Timing Extraction and Synchronisation                | 25  |

| 2.         | 3.1 Phase Locked Loops (PLL)                         | 27  |

| 2.4        | Digital Communication Errors and Error Correction    | 29  |

| 2.         | 4.1 Maximum Likelihood Sequence Detection (MLSD)     | 30  |

| 2.5        | Non-Return-To-Zero and Return-To-Zero Formats        | 32  |

| 2.6        | (FPGA) and Microcontroller Comparison                | 33  |

| 2.7        | VHSIC Hardware Description Language (VHDL)           |     |

| 2.8        | Summary                                              | 36  |

| <b>3</b> O | ptoelectronics of Optical Fibre Communication System | 37  |

| 3.1        | Introduction                                         |     |

| 3.2        | Optical Transmitter                                  |     |

| 3.         | 2.1 Optical Source                                   |     |

|            | 2.2 Laser Diodes                                     |     |

|   | 3.2 | 2.3  | Light Emitting Diodes                                      | 39 |

|---|-----|------|------------------------------------------------------------|----|

|   | 3.3 | Op   | tical Receiver                                             | 40 |

|   | 3.3 | 3.1  | Common Types of Photodetector                              | 41 |

|   | 3.4 | Ph   | oto Amplifier                                              | 41 |

|   | 3.5 | Op   | tical Fibre                                                | 42 |

|   | 3.5 | 5.1  | Types of Optical Fibre                                     | 43 |

|   | 3.5 | 5.2  | Plastic Optic Fibre                                        | 45 |

|   | 3.5 | 5.3  | Glass Optic Fibre                                          | 46 |

|   | 3.6 | Su   | mmary                                                      | 47 |

| 4 | Of  | fset | PPM Theory                                                 | 48 |

|   | 4.1 | Int  | roduction                                                  | 48 |

|   | 4.2 | Co   | ding Scheme                                                | 50 |

|   | 4.3 | En   | ors affect Offset PPM                                      | 50 |

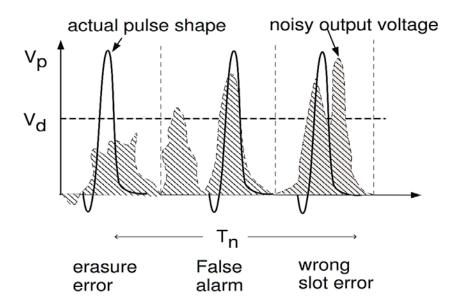

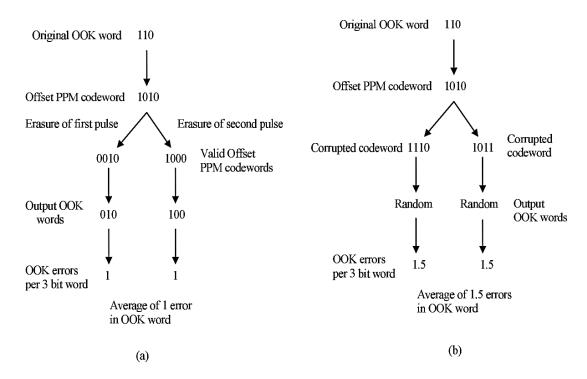

|   | 4.3 | 3.1  | Wrong slot errors                                          | 51 |

|   | 4.3 | 3.2  | Erasure errors                                             | 51 |

|   | 4.3 | 3.3  | False Alarm Errors                                         | 52 |

|   | 4.4 | Su   | mmary                                                      | 52 |

| 5 | Of  | fset | PPM Encoder and Decoder Design, Implementation and Testing | 53 |

|   | 5.1 | Int  | roduction                                                  | 53 |

|   | 5.2 | Pa   | rallel Offset PPM Encoder Design and Implementation        | 53 |

|   | 5.2 | 2.1  | Offset PPM Encoder Design                                  | 53 |

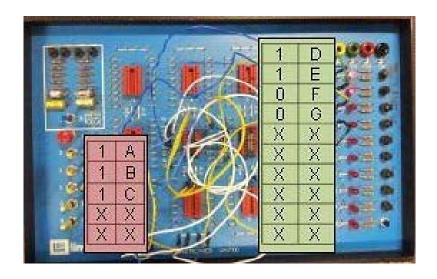

|   | 5.2 | 2.2  | Offset PPM Encoder Hardware Implementation                 | 57 |

|   | 5.2 | 2.3  | Encoder Hardware Implementation                            | 57 |

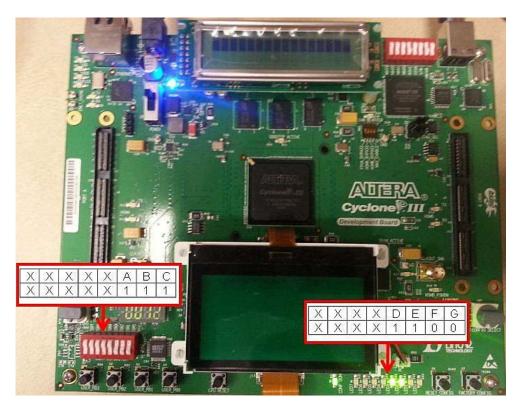

|   | 5.2 | 2.4  | Offset PPM Encoder FPGA Implementation                     | 58 |

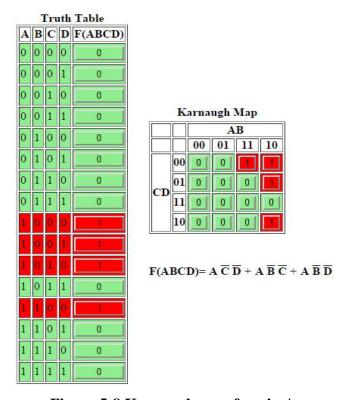

|   | 5.3 | Pa   | rallel Offset PPM Decoder Design and Implementation        | 59 |

|   | 5.3 | 3.1  | Offset PPM Decoder Design                                  | 59 |

|   | 5.3 | 3.2  | Offset PPM Decoder Hardware Implementation                 | 64 |

|   | 5.3 | 3.3  | Offset PPM Decoder Hardware Implementation                 | 65 |

|   | 5.3 | 3.4  | Decoder FPGA Implementation                                | 65 |

|   | 5.4 | Su   | mmary                                                      | 66 |

| 6 | VI  | HDL  | Source Code, Simulation, and Implementation of Offset PPM  | 67 |

|   |     |      | roduction                                                  | 67 |

|   | 6.2                                                      | VHDL and FPGA                                                                                                                                                                                                                                                                                                 | 0/                   |

|---|----------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

|   | 6.2                                                      | 2.1 VHDL                                                                                                                                                                                                                                                                                                      | 67                   |

|   | 6.2                                                      | 2.2 Field Programmable Gate Arrays (FPGA)                                                                                                                                                                                                                                                                     | 70                   |

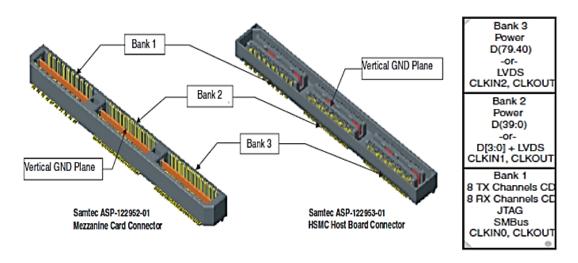

|   | 6.3                                                      | Cyclone III Development Board                                                                                                                                                                                                                                                                                 | 70                   |

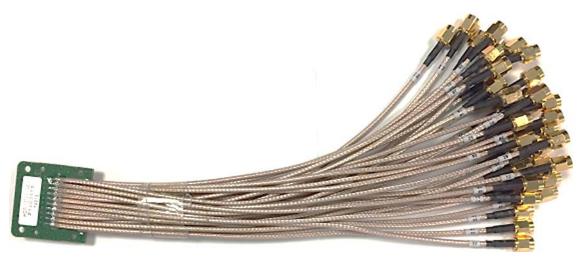

|   | 6.3                                                      | 3.1 SMA Breakout Cables                                                                                                                                                                                                                                                                                       | 71                   |

|   | 6.4                                                      | System Schematic                                                                                                                                                                                                                                                                                              | 73                   |

|   | 6.5                                                      | Offset PPM system Components                                                                                                                                                                                                                                                                                  | 74                   |

|   | 6.5                                                      | 5.1 Phase-locked Loop (PLL) Clock                                                                                                                                                                                                                                                                             | 74                   |

|   | 6.5                                                      | 5.2 Pseudo Random Binary Sequence (PRBS)                                                                                                                                                                                                                                                                      | 76                   |

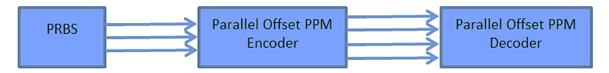

|   | 6.5                                                      | 5.3 Parallel Offset PPM Encoder                                                                                                                                                                                                                                                                               | 77                   |

|   | 6.5                                                      | 5.4 Parallel Offset PPM decoder                                                                                                                                                                                                                                                                               | 78                   |

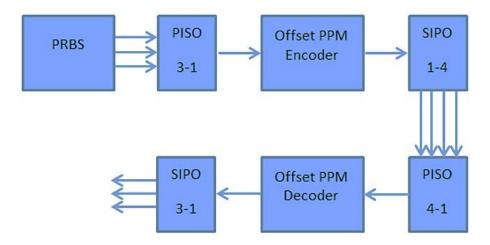

|   | 6.5                                                      | 5.5 Parallel Input Serial Output (PISO)                                                                                                                                                                                                                                                                       | 79                   |

|   | 6.5                                                      | 5.6 Serial Input Parallel Output (SIPO)                                                                                                                                                                                                                                                                       | 80                   |

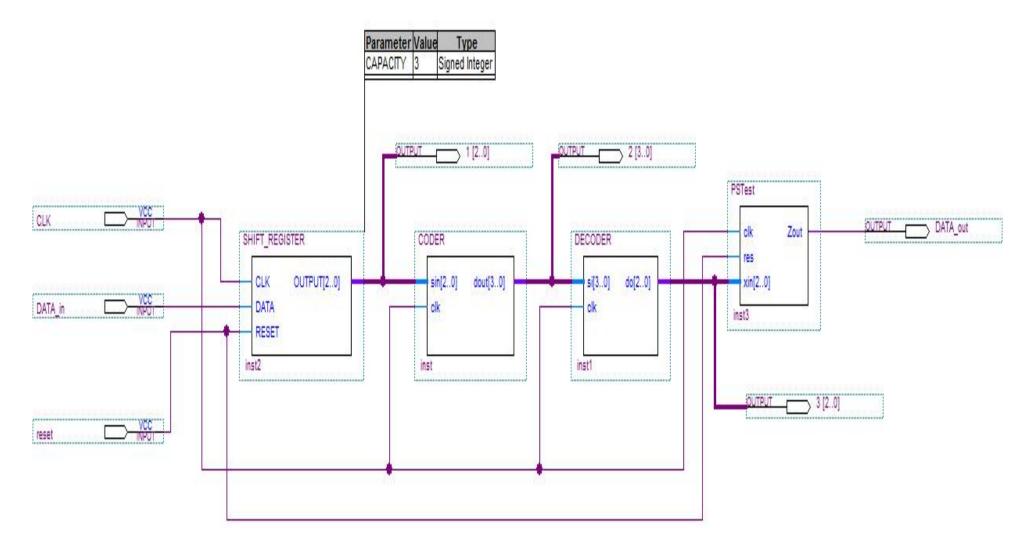

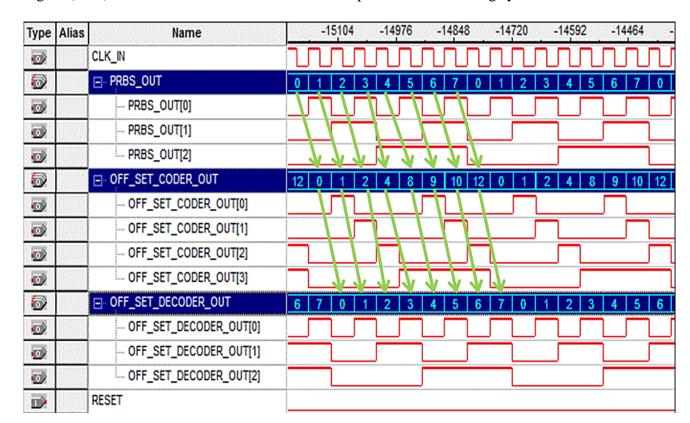

|   | 6.6                                                      | Parallel Offset PPM coding System Implementation                                                                                                                                                                                                                                                              | 80                   |

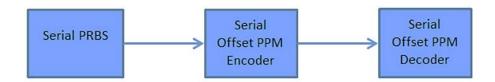

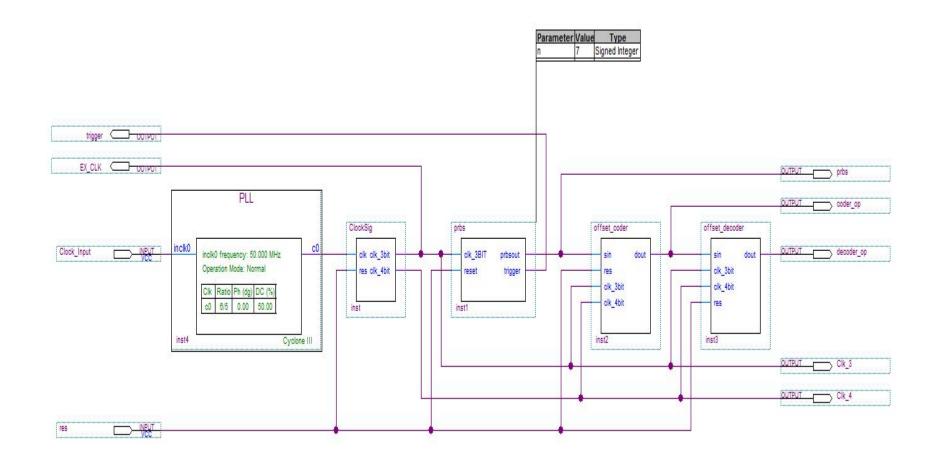

|   | 6.7                                                      | Serial Offset PPM Coding System Implementation                                                                                                                                                                                                                                                                | 82                   |

|   | 6.8                                                      | Summary                                                                                                                                                                                                                                                                                                       | 91                   |

| 7 | OI                                                       | otical Offset PPM Communication System                                                                                                                                                                                                                                                                        | 92                   |

|   | 7.1                                                      | Introduction                                                                                                                                                                                                                                                                                                  |                      |

|   | 7.2                                                      |                                                                                                                                                                                                                                                                                                               |                      |

|   | 1.4                                                      | Serial Set Offset PPM coding system with Optical Components and External PRBS                                                                                                                                                                                                                                 | 94                   |

|   | 7.2                                                      | Serial Set Offset PPM coding system with Optical Components and External PRBS  Experiment Hardware and Software Resources                                                                                                                                                                                     |                      |

|   |                                                          | Experiment Hardware and Software Resources                                                                                                                                                                                                                                                                    | 94                   |

|   | 7.3                                                      | Experiment Hardware and Software Resources                                                                                                                                                                                                                                                                    | 94<br>94             |

|   | 7.3<br>7.3<br>7.3                                        | Experiment Hardware and Software Resources                                                                                                                                                                                                                                                                    | 94<br>94<br>94       |

|   | 7.3<br>7.3<br>7.3<br>7.                                  | Experiment Hardware and Software Resources  3.1 FPGA & VHDL  3.2 Optical Fibre Communication System Components                                                                                                                                                                                                | 94<br>94<br>94       |

|   | 7.3<br>7.3<br>7.3<br>7.                                  | Experiment Hardware and Software Resources  3.1 FPGA & VHDL  3.2 Optical Fibre Communication System Components  3.2.1 Optical Transmitter                                                                                                                                                                     | 94949494             |

|   | 7.3<br>7.3<br>7.3<br>7.<br>7.                            | Experiment Hardware and Software Resources  3.1 FPGA & VHDL  3.2 Optical Fibre Communication System Components  3.2.1 Optical Transmitter  3.2.2 Optical Receiver                                                                                                                                             | 9494949497           |

|   | 7.3<br>7.3<br>7.<br>7.<br>7.<br>7.                       | Experiment Hardware and Software Resources  3.1 FPGA & VHDL  3.2 Optical Fibre Communication System Components  3.2.1 Optical Transmitter  3.2.2 Optical Receiver  3.2.3 Plastic Optical Fibre (POF)                                                                                                          | 949494979799         |

|   | 7.3<br>7.3<br>7.<br>7.<br>7.<br>7.                       | Experiment Hardware and Software Resources  3.1 FPGA & VHDL  3.2 Optical Fibre Communication System Components  3.2.1 Optical Transmitter  3.2.2 Optical Receiver  3.2.3 Plastic Optical Fibre (POF)  3.3 Voltage Comparator                                                                                  | 9494949799100        |

|   | 7.3<br>7.3<br>7.<br>7.<br>7.<br>7.<br>7.3                | Experiment Hardware and Software Resources  3.1 FPGA & VHDL  3.2 Optical Fibre Communication System Components  3.2.1 Optical Transmitter  3.2.2 Optical Receiver  3.2.3 Plastic Optical Fibre (POF)  3.3 Voltage Comparator  3.4 PRBS Generator  Implementation of Offset PPM System                         | 949497999799100      |

|   | 7.3<br>7.3<br>7.<br>7.<br>7.<br>7.3<br>7.3<br>7.4        | Experiment Hardware and Software Resources  3.1 FPGA & VHDL  3.2 Optical Fibre Communication System Components  3.2.1 Optical Transmitter  3.2.2 Optical Receiver  3.2.3 Plastic Optical Fibre (POF)  3.3 Voltage Comparator  3.4 PRBS Generator  Implementation of Offset PPM System  4.1 Simulation Results | 94949799100103104    |

|   | 7.3<br>7.3<br>7.<br>7.<br>7.<br>7.3<br>7.3<br>7.4<br>7.4 | Experiment Hardware and Software Resources  3.1 FPGA & VHDL  3.2 Optical Fibre Communication System Components  3.2.1 Optical Transmitter  3.2.2 Optical Receiver  3.2.3 Plastic Optical Fibre (POF)  3.3 Voltage Comparator  3.4 PRBS Generator  Implementation of Offset PPM System  4.1 Simulation Results | 94949799100103104109 |

| 8  | Co   | onclusions and future work              | 117 |

|----|------|-----------------------------------------|-----|

|    | 8.1  | Conclusions                             | 117 |

|    | 8.2  | Future Work                             | 118 |

| 9  | Ap   | ppendixes                               | 120 |

|    | 9.1  | VHDL codes                              | 120 |

|    | 9.2  | Optical transmitter/receiver data sheet | 128 |

|    | 9.3  | POF data sheet                          | 140 |

|    | 9.4  | Comparator data sheet                   | 150 |

| 10 | ) Re | eferences                               | 164 |

# **List of Figures**

| Figure 1-1 Schematic diagram of general communication system                              | 2  |

|-------------------------------------------------------------------------------------------|----|

| Figure 1-2 Schematic diagram of a fibre-optic system                                      | 3  |

| Figure 1-3 Typical digital fibre-optic link                                               | 4  |

| Figure 2-1 Pulse Position Modulation (Liu, 2002)                                          | 15 |

| Figure 2-2 Conversion of PCM to Multiple PPM double pulses per frame                      | 16 |

| Figure 2-3 Conversions of PCM data into DPPM (Middle trace) and DiPPM                     | 18 |

| Figure 2-4 Conversion of PCM data (top trace) into dicode (Middle trace)                  | 19 |

| Figure 2-5 Conversion of OOK data (top trace) into DuoPPM (bottom trace)                  | 20 |

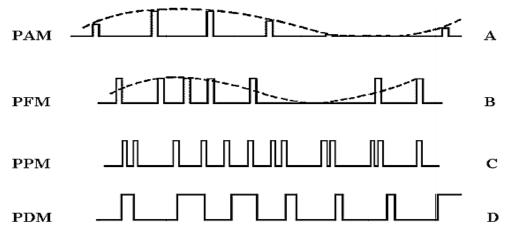

| Figure 2-6 PAM (A), PFM (B), PPM (C) and PDM (D)                                          | 21 |

| Figure 2-7 Pulse Code Modulation                                                          | 22 |

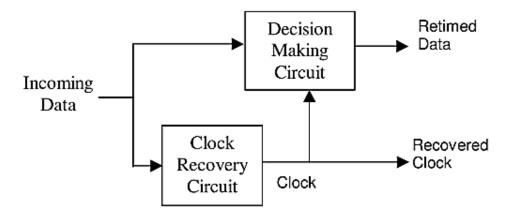

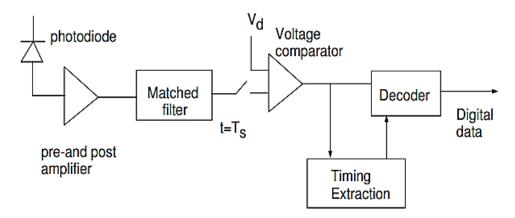

| Figure 2-8 Simplified block diagram of a digital receiver                                 | 28 |

| Figure 2-9 Generation of different types of error considering Gaussian type pulse shape   | 31 |

| Figure 2-10 Shown how (a) erasures and (b) false alarms affect the decoding of offset PPM | 32 |

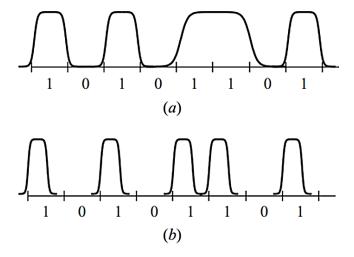

| Figure 2-11 (a) NRZ and (b) RZ bit patterns corresponding to the bit sequence 10101101    | 33 |

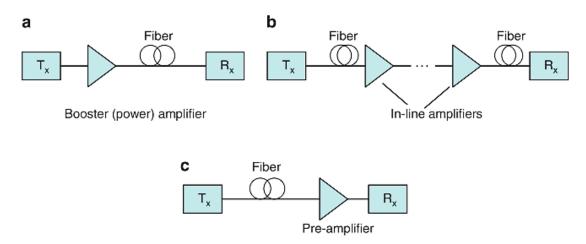

| Figure 3-1 Possible applications of optical amplifiers                                    | 42 |

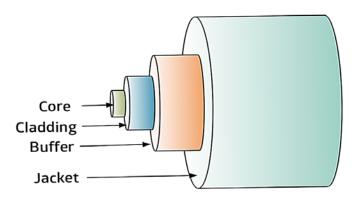

| Figure 3-2 Optical fibre cable structure                                                  | 43 |

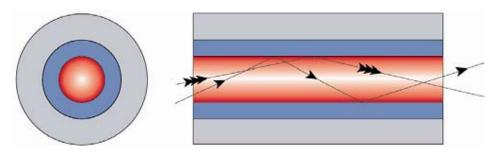

| Figure 3-3 Multimode fibre light propagation                                              | 44 |

| Figure 3-4 Single mode fibre light propagation                                            | 44 |

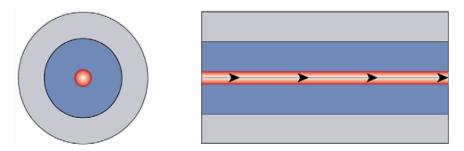

| Figure 3-5 Multimode and singlemode fibres layout                                         | 45 |

| Figure 4-1 Offset PPM coder and transmitter system (M. J. Sibley, 2011)                   | 49 |

| Figure 4-2 Schematic of an optical receiver system (M. J. Sibley, 2011)                   | 49 |

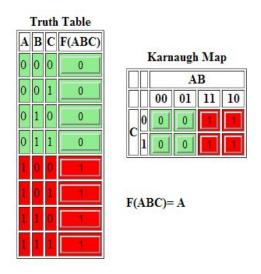

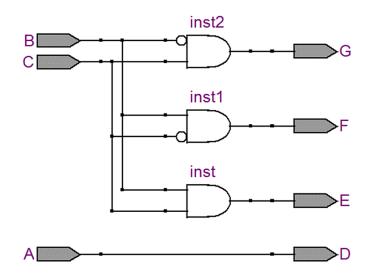

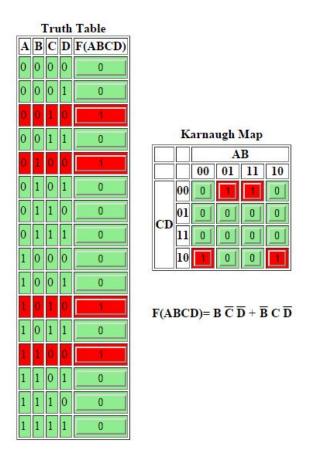

| Figure 5-1 Karnaugh map application for pin (D)                                           | 55 |

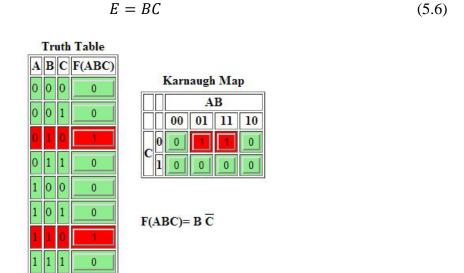

| Figure 5-2 Karnaugh map application for pin (E)                                           | 55 |

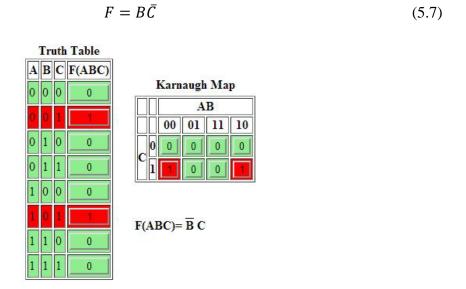

| Figure 5-3 Karnaugh map application for pin (F)                                 | 56 |

|---------------------------------------------------------------------------------|----|

| Figure 5-4 Karnaugh map application for pin (G)                                 | 56 |

| Figure 5-5 Offset PPM encoder Schematic                                         | 57 |

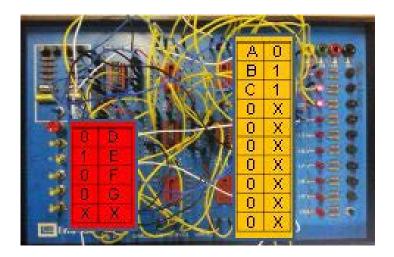

| Figure 5-6 Offset PPM encoder implementation using a Limrose board              | 58 |

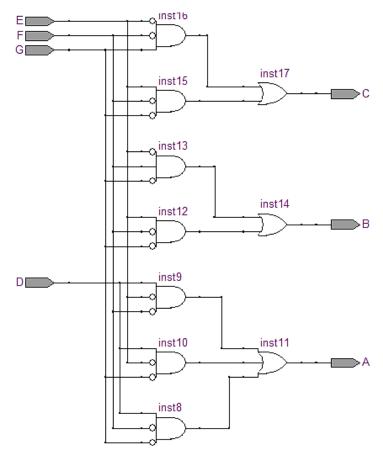

| Figure 5-7 FPGA hardware implementation for the Offset PPM encoder              | 59 |

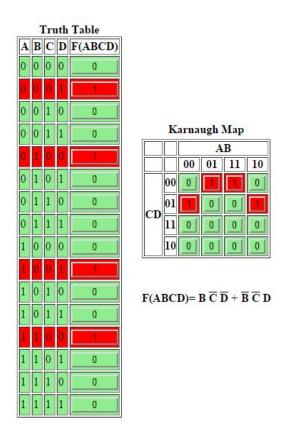

| Figure 5-8 Karnaugh map for pin A                                               | 61 |

| Figure 5-9 Karnaugh map for pin B                                               | 62 |

| Figure 5-10 Karnaugh map for pin C                                              | 63 |

| Figure 5-11 Offset PPM decoder schematic                                        | 64 |

| Figure 5-12 Offset PPM decoder implementation using a Limrose board             | 65 |

| Figure 5-13 FPGA implementation for the Offset PPM decoder                      | 66 |

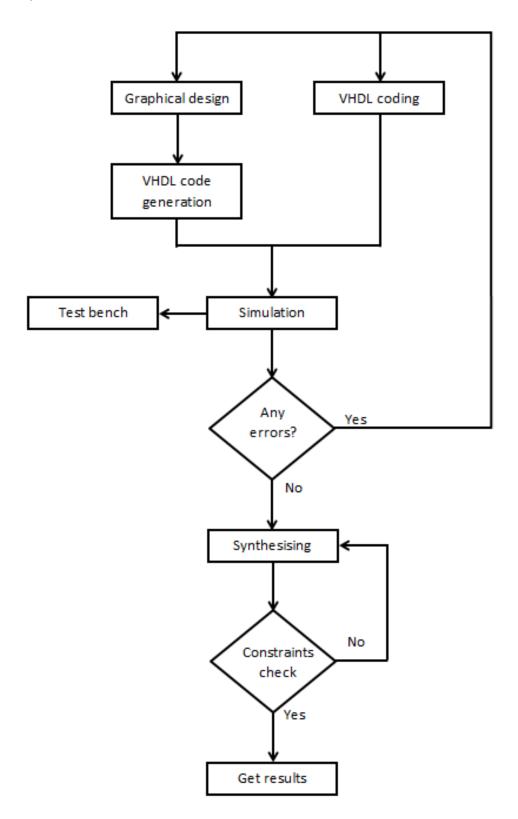

| Figure 6-1 VHDL Implementation flow chart                                       | 68 |

| Figure 6-2 Offset PPM VHDL code sequence                                        | 69 |

| Figure 6-3 Cyclone III FPGA                                                     | 71 |

| Figure 6-4 MC Connectors (Altera, 2015)                                         | 72 |

| Figure 6-5 SMA Breakout Cable                                                   | 73 |

| Figure 6-6 Block Diagram of Parallel Offset PPM coding                          | 73 |

| Figure 6-7 Block Diagram of First version of serial Offset PPM coding schematic | 74 |

| Figure 6-8 Block Diagram of Serial Offset PPM                                   | 74 |

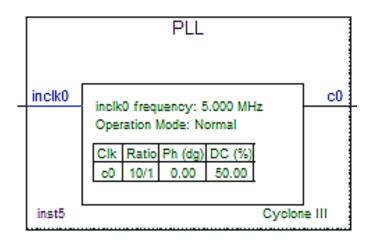

| Figure 6-9 Offset PPM PLL design for clocking requirements                      | 75 |

| Figure 6-10 PLL clock generation simulation result                              | 75 |

| Figure 6-11 Main section of the PRBS generator VHDL code                        | 76 |

| Figure 6-12 PRBS data generation in VHDL                                        | 76 |

| Figure 6-13 Main section Parallel Offset PPM Encoder VHDL source code           | 77 |

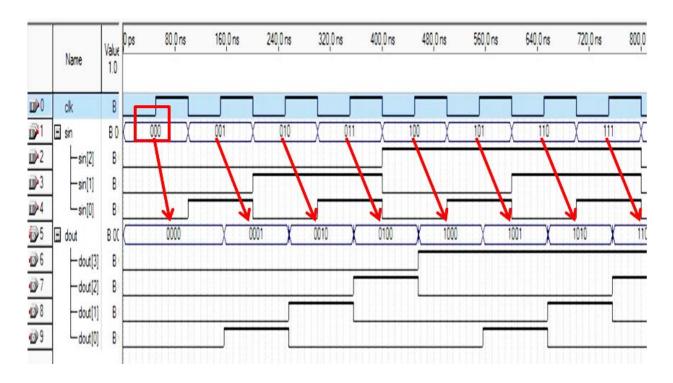

| Figure 6-14 Offset PPM encoder VHDL simulation results                          | 78 |

| Figure 6-15 Parallel Offset PPM decoder VHDL code                                | 78  |

|----------------------------------------------------------------------------------|-----|

| Figure 6-16 Offset PPM decoder VHDL simulation results                           | 79  |

| Figure 6-17 PISO top block view                                                  | 79  |

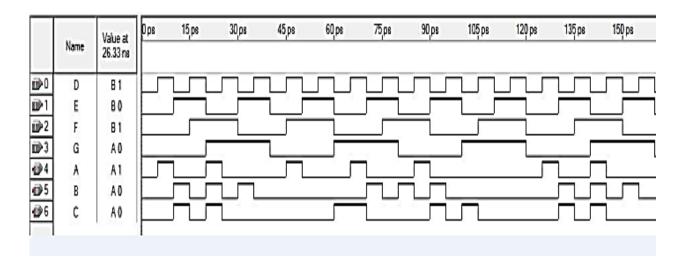

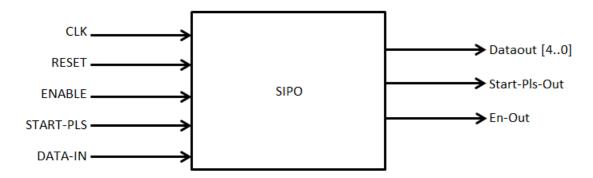

| Figure 6-18 SIPO top block view                                                  | 80  |

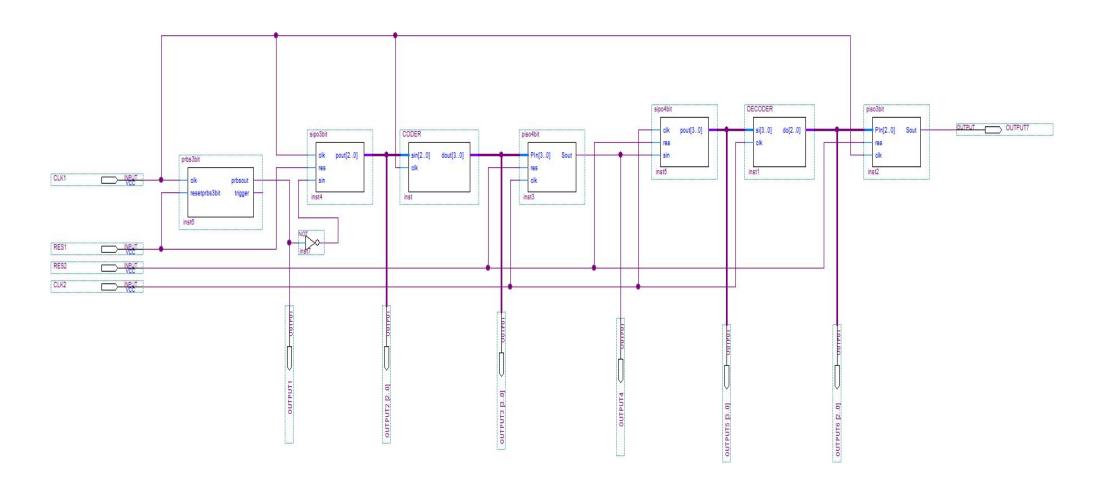

| Figure 6-19 Parallel Offset PPM                                                  | 81  |

| Figure 6-20 Real time waveform parallel Offset PPM                               | 82  |

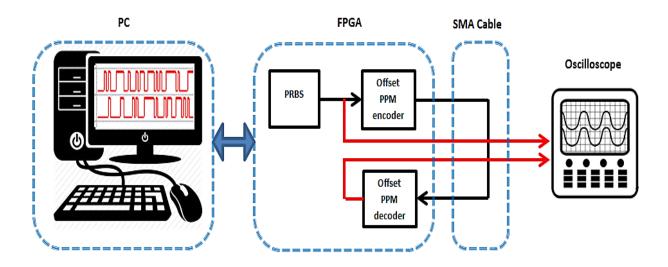

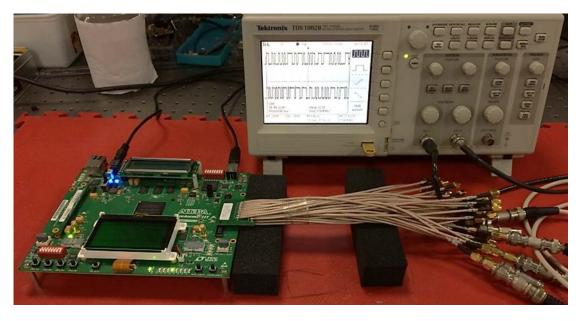

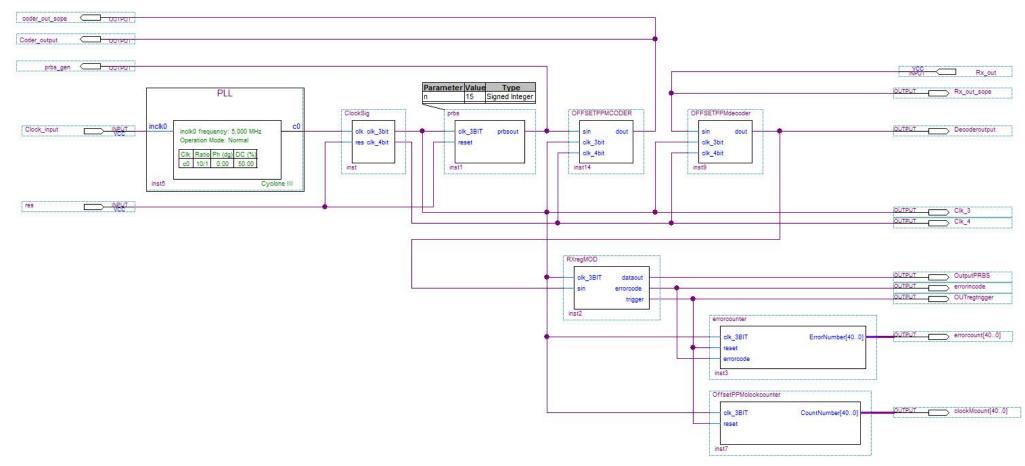

| Figure 6-21 Serial Offset PPM system layout                                      | 83  |

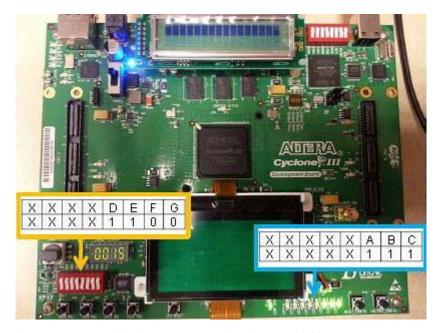

| Figure 6-22 Offset PPM system without optical fibre links                        | 83  |

| Figure 6-23 First version serial Offset PPM                                      | 85  |

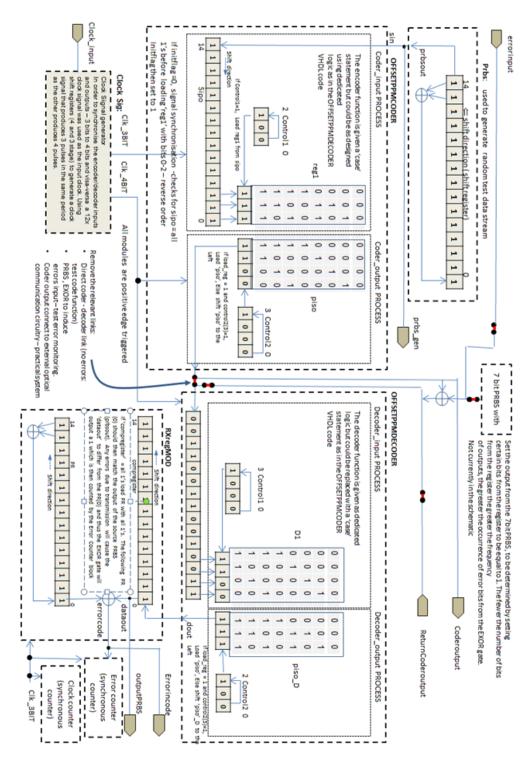

| Figure 6-24 Serial Offset PPM schematic diagram                                  | 86  |

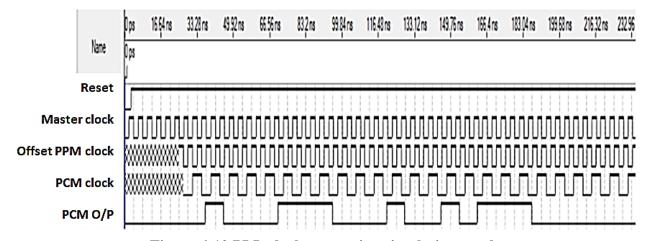

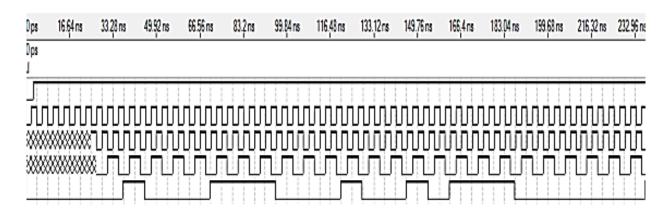

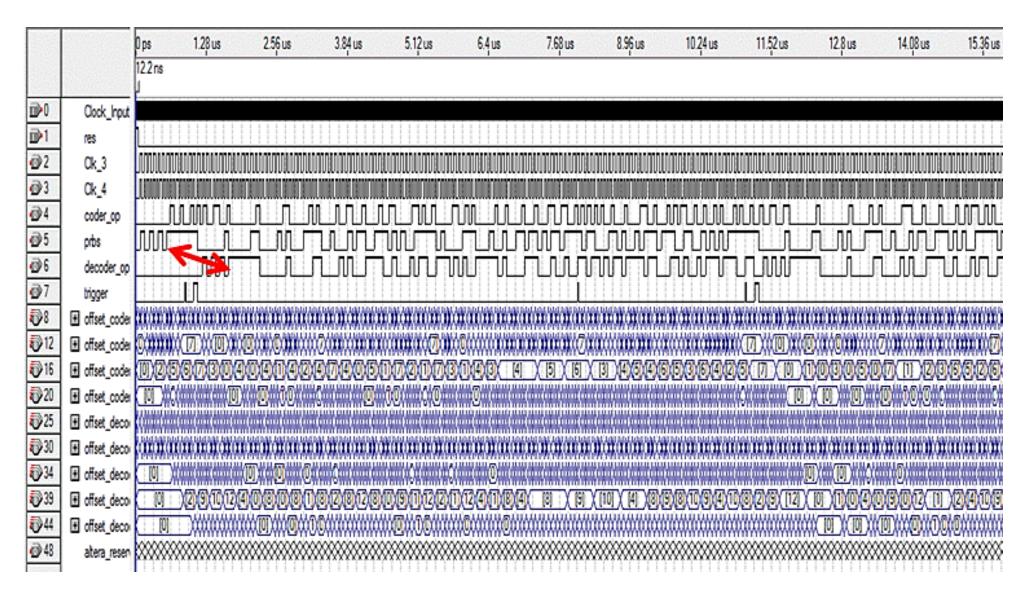

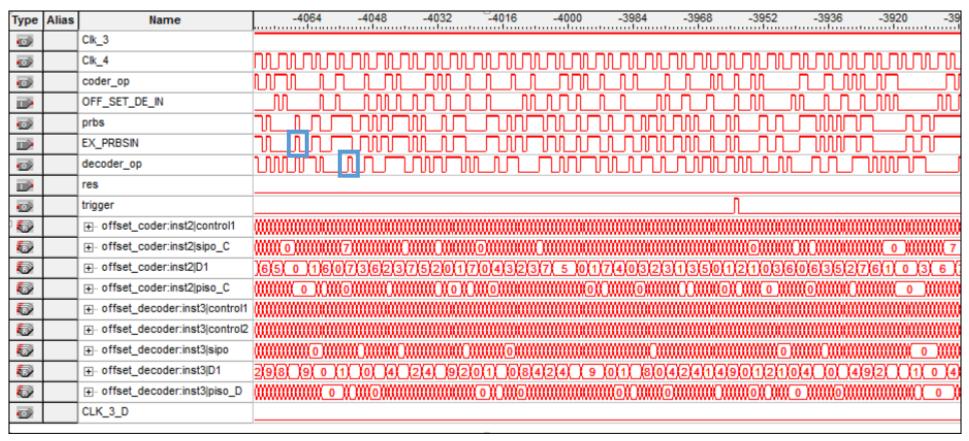

| Figure 6-25 Serial Offset PPM simulation.                                        | 88  |

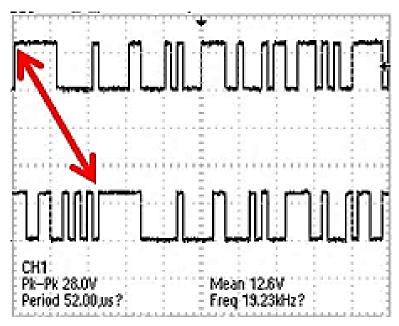

| Figure 6-26 Real time waveform serial Offset PPM                                 | 90  |

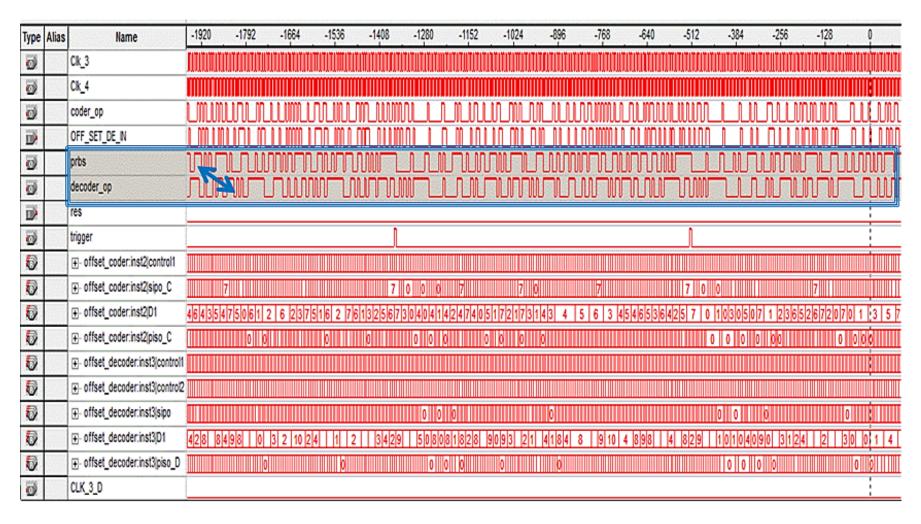

| Figure 6-27 PRBS output (top trace), Offset PPM decoder (bottom trace)           | 91  |

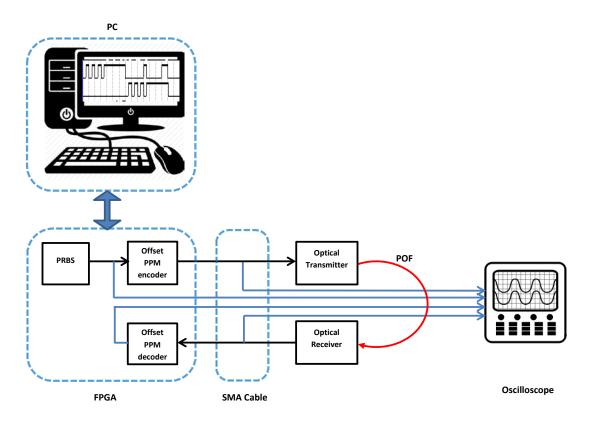

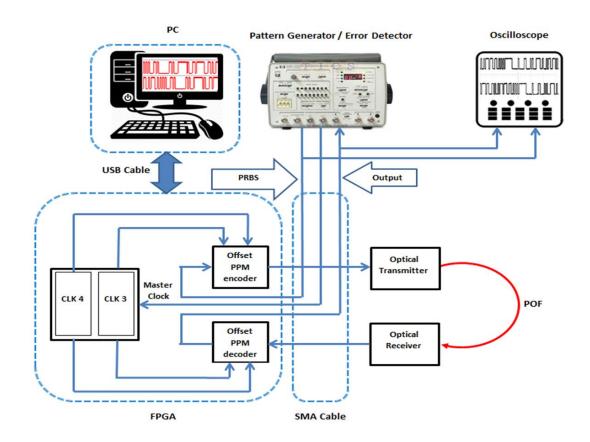

| Figure 7-1 Frame work of the full Offset communication system                    | 92  |

| Figure 7-2 Frame work of the full Offset communication system with external PRBS | 93  |

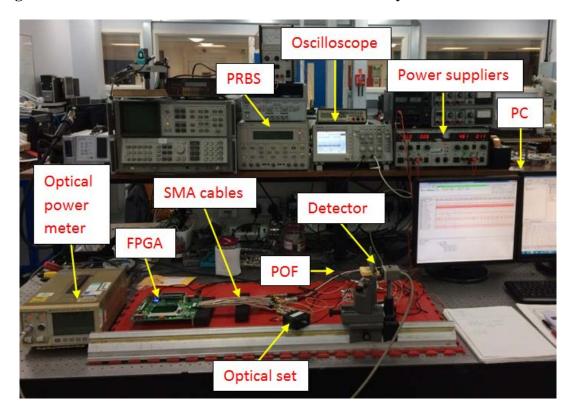

| Figure 7-3 Test bench setup                                                      | 93  |

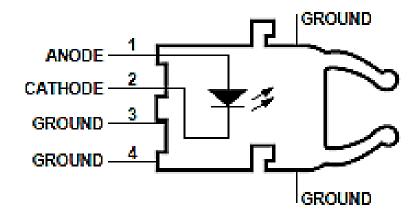

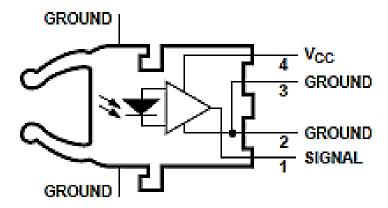

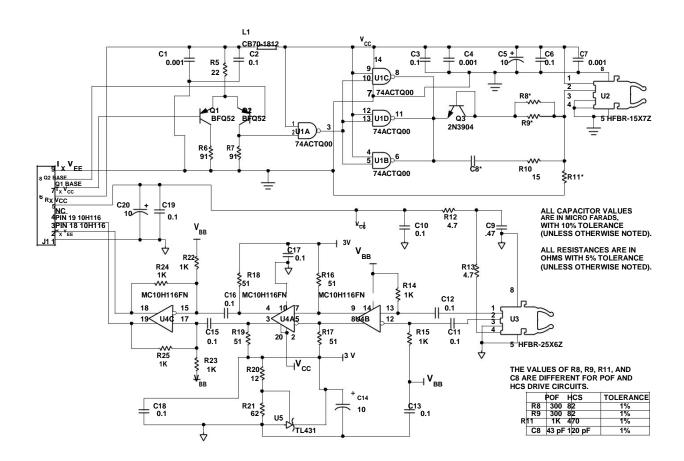

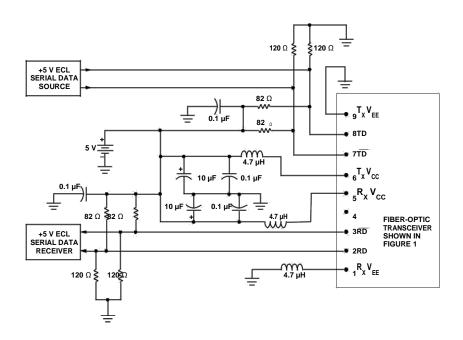

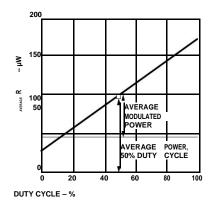

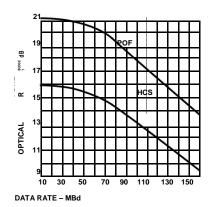

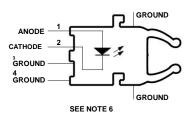

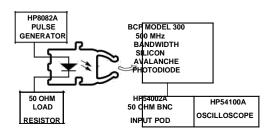

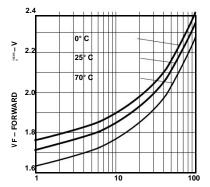

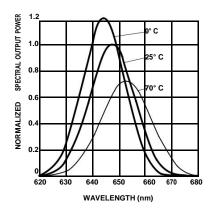

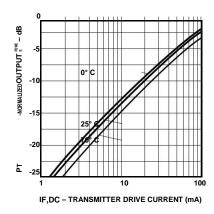

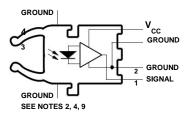

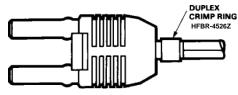

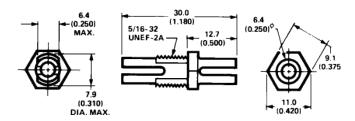

| Figure 7-4 Optical transmitter layouts (Appendix 9.2)                            | 96  |

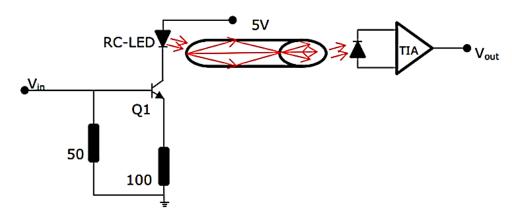

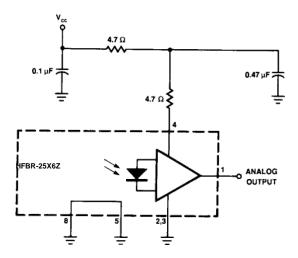

| Figure 7-5 Optical Transmitter Circuit                                           | 96  |

| Figure 7-6 Optical transmitter part                                              | 96  |

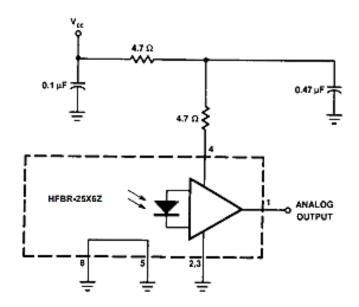

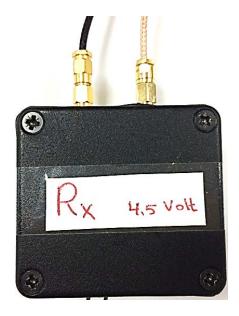

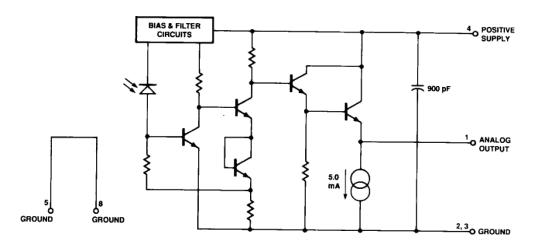

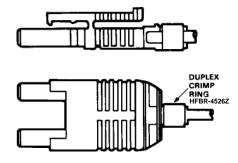

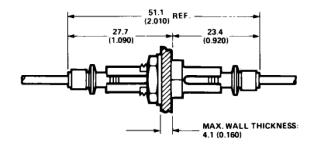

| Figure 7-7 Optical receiver layouts                                              | 98  |

| Figure 7-8 Power supply Circuit for Optical Receive (Appendix 9.2)               | 99  |

| Figure 7-9 Optical receiver part                                                 | 99  |

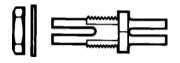

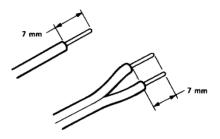

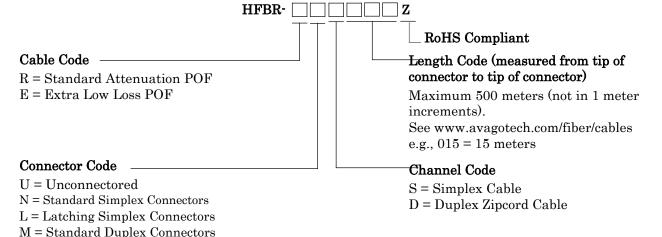

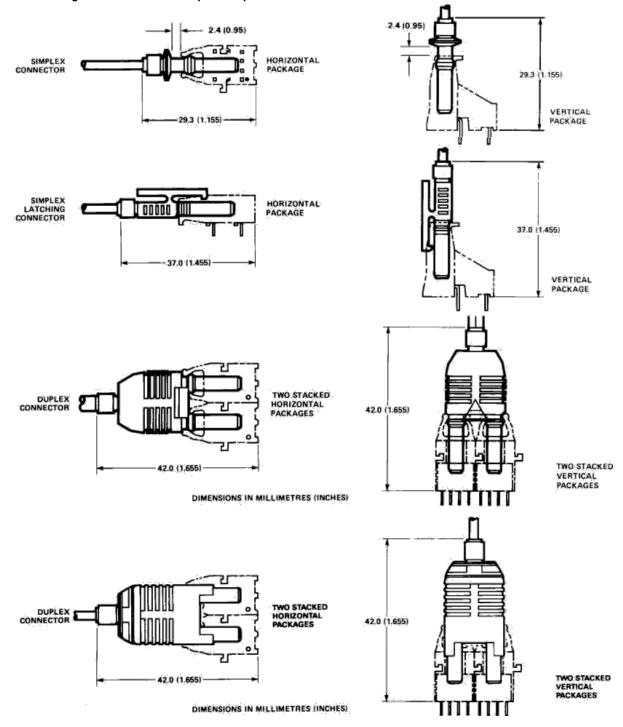

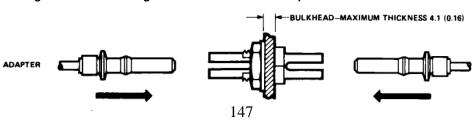

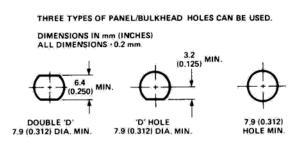

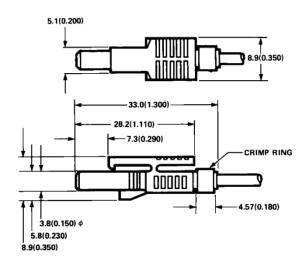

| Figure 7-10 HFBR-R optical fibre (Appendix 9.3)                                  | 100 |

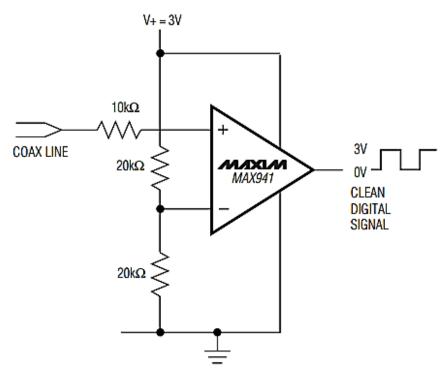

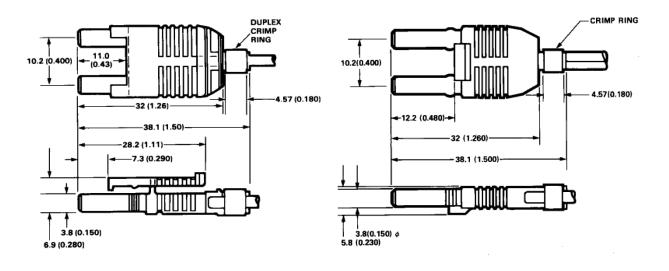

| Figure 7-11 Voltage comparator circuit (Appendix 9.4)                            | 102 |

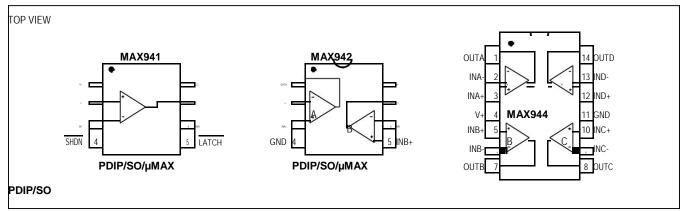

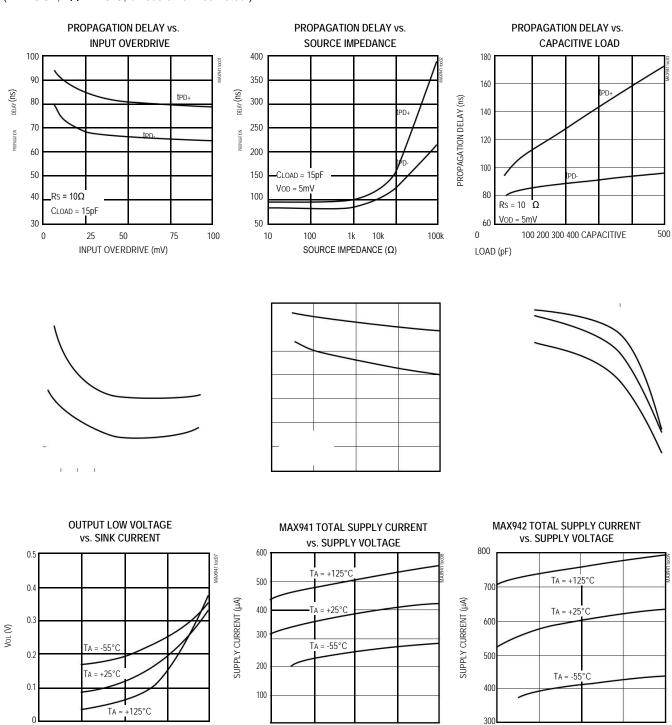

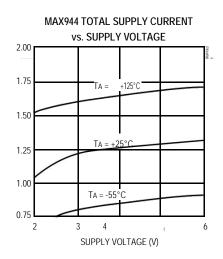

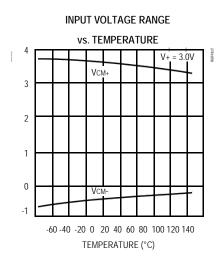

| Figure 7-12 MAX941 Pin configuration                                             | 102 |

| Figure 7-13 Voltage comparator part                                                  | 102 |

|--------------------------------------------------------------------------------------|-----|

| Figure 7-14 Voltage comparator Input/Output                                          | 103 |

| Figure 7-15 Hewlett-Packard HP 3780A PRBS generator                                  | 104 |

| Figure 7-16 Optical Offset PPM system design using Altera Quartus II v. 9.1 software | 106 |

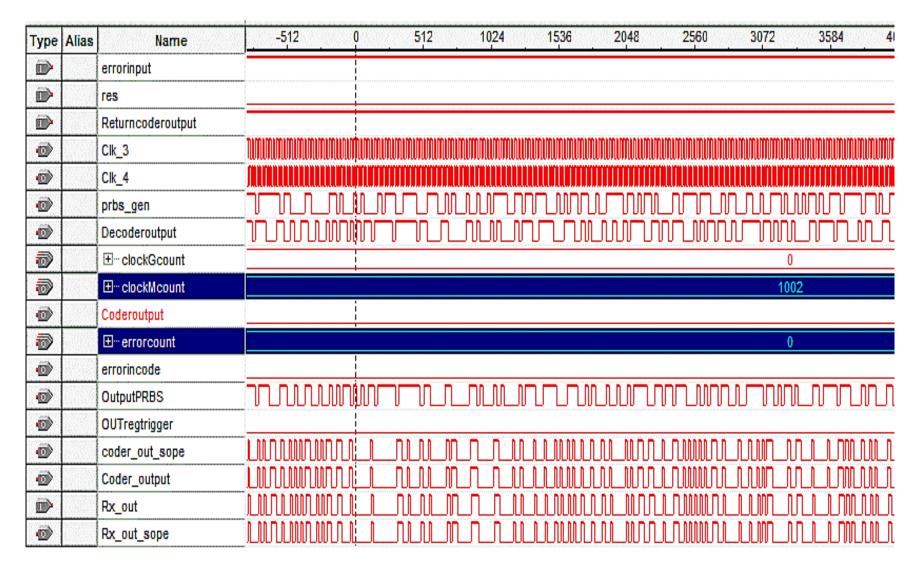

| Figure 7-17 Offset PPM system simulation results                                     | 108 |

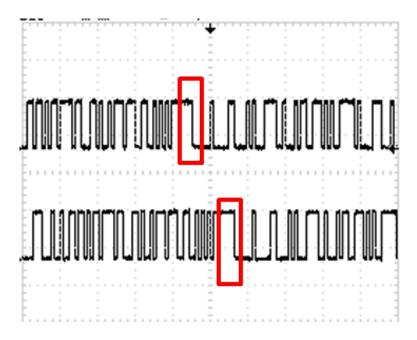

| Figure 7-18 External PRBS output waveform and Offset PPM decoder output              | 110 |

| Figure 7-19 PRBS waveform output and Offset PPM Decoder output                       | 111 |

| Figure 7-20 Minimum BER recorded                                                     | 113 |

| Figure 7-21 Digital transmission measurements and analysis based on FPGA             | 114 |

| Figure 7-22 Real time waveform output error and clock counters                       | 115 |

# **List of Tables**

| Table 2.1 DiPPM Symbol Alphabet                                                              | 19 |

|----------------------------------------------------------------------------------------------|----|

| Table 2.2 Generation of different types of coding from equivalent 3 bits of data             | 25 |

| Table 3.1 Typical specifications of plastic optical fibre used in communication applications | 46 |

| Table 4.1 Generating the offset pulse, the sign bit in offset PPM is shown in italics        | 49 |

| Table 5.1 Truth table of Offset PPM encoder                                                  | 54 |

| Table 5.2 Truth table for the Offset PPM Decoder                                             | 60 |

#### **List of Abbreviations**

ADC Analogue to Digital Converter

ADM Adaptive-Delta Modulation

ADPLL All Digital Phase Looked Loop

BER Bit Error Rate

CCD Charge Coupled Detectors

CCPPM Colour Coded PPM

CDR Clock and Data Recovery

CPLD Complex Programmable Logic Device

CVSDM Continuously Variable Slope Delta Modulation

DAC Digital to Analogue Converter

DCM Digital Clock Managers

DiPPM Dicode Pulse Position Modulation

DPLL Digital Phase Looked Loop

DPPM Digital Pulse Position Modulation

DuoPPM Duobinary Pulse Position Modulation

EM Electromagnetic

FPGA Field Programmable Gate Array

GaAsP Gallium Arsenide Phosphide

GaP Gallium Phosphide

GHz Giga Hertz

I/O Input/output

IEEE Institute of Electrical and Electronics Engineers

IFI Inter-frame Interference

ISI Inter-Symbol Interference

Km Kilometre

LD Laser Diode

LED Light Emitting Diode

LSI Large-Scale Integrate

MHz Mega Hertz

MLSD Maximum Likelihood Sequence Detection

mm Millimetre

MPPM Multiple Pulse Position Modulation

MSB Most Significant Bit

MSI Medium-Scale Integrated

nm Nanometre

NRZ Non Return-to-Zero

Offset PPM Offset Pulse Position Modulation

OOK On-Off Keying

OPPM Overlapping Pulse Position Modulation

PAM Pulse Amplitude Modulation

PC Personal Computer

PCM Pulse Code Modulation

PDM Pulse Density Modulation

PFM Pulse Frequency Modulation

PISO Parallel Input Serial Output

PLD Programmable Logic Device

PLL Phase Looked Loop

PMMA Polymethyl Methacrylate and Fluorinated Acrylic

POF Plastic Optical Fibre

PPM Pulse Position Modulation

PRBS Pseudo Random Binary Sequence

PWM Pulse Width Modulation

QPAM Quadrature Pulse Amplitude Modulation

RAM Random Access Memory

RZ Return-to-Zero

SIPO Serial Input Parallel Output

SNR Signal to Noise Ratio

SPLL Software Phase Looked Loop

SPPM Shortened Pulse Position Modulation

SSI Small-Scale Integrated

STA Signal Tap Analyser

TIR Total Internal Reflection

TTL Transistor-Transistor Logic

VHDL VHSIC Hardware Description Language

VHSIC Very High Speed Integrated Circuits

VLSI Very Large-Scale Integrated

WDM Wavelength-Division Multiplexing

$\Sigma \Delta M$  Sigma-delta

### 1 Introduction

#### 1.1 Optical Communication Background

Communication is defined as a process by which information is imparted or exchanged; a communication system facilitates the transmission of this information from a sender to a receiver. The elements of a communication system the hardware, carrier medium, etc. are generally determined by characteristics of the application in which it is to be used. For example, the information may need to be communicated over short distances (several kilometres) or between continents (in the order of thousands of kilometres).

Electromagnetic (EM) radiation, specifically with frequencies in the range from radio waves (megahertz), through microwave (in the order of gigahertz) to near infrared and visible light (several hundred terahertz) are often used as the carrier medium for communication. Communication systems employing the visible and near infra-red parts of the EM spectrum as carrier waves are referred to as 'light-wave', or 'optical' communication systems. The use of optical transmission was first made possible following the demonstration of laser light by Theodore Mainman in 1962. The following year, as reported by (Ghassemlooy & Popoola, 2010), a laser beam was first used to carry a television transmission. A further significant advance in optical communication systems occurred seven years later when high speed signal modulation was made possible by the production of a small scale semiconductor laser.

In the 1970's, the focus of optical transmission research was the development of fibre-optic communication systems. After its invention in the early part of that decade, interest in use of the fibre optic cable as a means of transmitting information rapidly grew on account of its very low signal loss. The high bandwidth and rapid transmission rate enabled by fibre-optic cable rapidly caused it to become widespread, and it has been employed globally in communication systems since the early 1980's, changing the nature of telecommunications beyond recognition. Such has been its

impact that it could be considered to have been one of the principal driving forces behind the information revolution (G. P. Agrawal, 2002).

The internet, digital television, computer networks and digital media amongst many other applications rely on the transfer of massive quantities of data. To date, only optical fibre offers sufficient bandwidth to transmit this data; without it, it is unlikely that such developments would have expanded to the extent that they have today. This situation is likely to remain for the foreseeable future; there is considerable demand for wireless technology, which offers many of the same benefits, but to be exploited fully, this is largely required to be connected to and compatible with fibre-optic communication systems (Dai, Wang, & Yang, 2012).

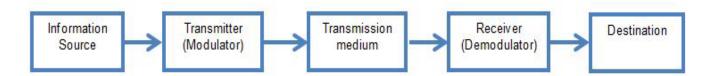

All communication systems comprise three components – a transmitter, a transmission medium and a receiver. Figure (1.1) shows a schematic diagram of such a system. The source is the entity that from which the information to be sent originates. The information must be converted into a form in which it can be carrier through the communication system; this conversion is performed by the transmitter, in a process known as modulation. The transmitter then passes the modulated information to the transmission medium, through which the information travels until it reaches the receiver, where it is converted back (demodulated) to a form that can be understood by the entity to whom the information is being relayed.

Figure 1-1 Schematic diagram of general communication system

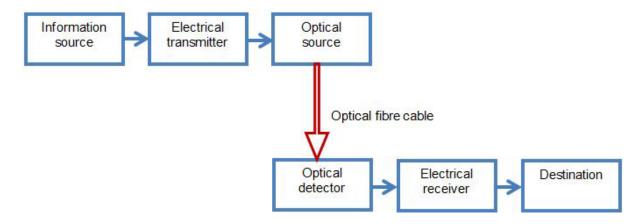

All fibre-optic communication systems comprise the same three fundamental components. In these systems, the transmitter is a light source, such as a Laser or a Light Emitting Diode (LED) and the optical fibre acts as the carrier, guiding the light signals from source to destination. The modulation in fibre-optic systems is performed by converting an electrical signal to light. One means of doing

this, 'digital' or 'direct' modulation, is analogous to the production of a Morse code signal, only optical rather than audible pulses are created. The pattern with which the electrical signal is switched on and off is reproduced in the light signals (DeCusatis & DeCusatis, 2010). Figure (1.2) shows a schematic of a fibre-optic system, in which the information from the source is passed to the transmitter. The modulation of the optical carrier is provided by this transmitter driving the optical source.

Figure 1-2 Schematic diagram of a fibre-optic system

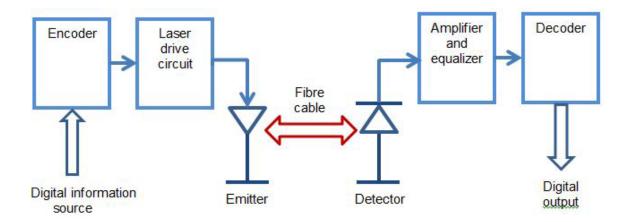

In figure (1.3), the more detailed components of a typical digital fibre-optic link are illustrated schematically. In this situation, the digital optical signal that enters the fibre-optic cable is created by the direct modulation of the semiconductor laser intensity with the encoded digital signal that has been input from the information source. At the receiving end, the signal is detected by a photodiode detector, which converts the optical signals into electrical signals, after which any signal processing that may be required is applied (for example, amplification or noise reduction) before the signal is decoded to pass the original information in the form of a digital signal to the receiver (Westbrook & Moodie, 1996).

Figure 1-3 Typical digital fibre-optic link

#### 1.2 Features of Fibre Optic Communication Systems

#### 1.2.1 Advantages

The principal alternative to optical fibre in communication systems is metal-based electrical cabling. There are many ways in which optical fibres are advantageous to electrical systems (Keiser, 2003), including the following:

#### • Transmission Over Long Distances: Lower Signal Degradation and Loss

Fibre-optic communication systems are associated with significantly lower signal loss than copper-based systems. The nature of signal transmission within fibre-optic cables minimizes signal attenuation and maintains the integrity of the signals; fibre-optic cable can carry signals over fifty times as far as copper cables before processing is required for performance to be enhanced.

#### • Future-Proofing for Bandwidth Expansion

As the required bandwidth necessitated by increased internet use and increasingly dataintensive applications expands, the need to increase the data capacity of systems will continue to grow. Within any given system, fibre-optic cables are by several orders of magnitude the most efficient means of transmitting signals. As financial and logistical constraints often necessitate the use of existing infrastructure when expanding systems (for example, installing cables in pre-existing cable runs), the high performance and small dimensions of fibre-optic cables make them the most effective and efficient means of future-proofing.

#### • Availability of Resources

Electrical cabling systems depend on large quantities of copper and aluminium, resources of which are finite. The principal raw material for fibre-optic cable is sand which is not only available in far greater abundance, but is also much cheaper than those metals. (Furthermore, the cost of metal cabling is likely to rise in the future as resources, adding to the benefits in the previous point.)

#### • Unaffected by Electromagnetic Interference

Fibre-optic cables are ideal for use where EM interference might affect the performance of copper-based cables. They are electrical insulators and, as such, are not affected by the impact of fields from other electrical cables, radio-frequency interference or more severe problems such as lightning strikes.

#### • Electrical Safety

Using light, rather than electrical signals, fibre-optic communication is safer in that there are considerably lower electrical safety hazards.

#### • Greater Data Security

Fibre-optic cables provide higher security than traditional metal cabling as the absence of magnetic fields prevents the external detection of the signals. This clearly makes fibre-optic communication systems the preferential option when data protection is vital; while data can be intercepted, it requires the cable to be spliced, which is almost impossible to do undetected. Fibre-optic cable is the most secure means of transmitted data at present.

#### Longevity

The fibre-optic cable hardware has greater longevity than copper-based cables as glass is not subject to corrosion or oxidation. Copper is more liable to be degraded by acids, moisture and toxic gases and other such conditions found in more challenging environments. Therefore, fibre-optic cable can be expected to last much longer than copper cable.

#### • Temperature Independence

The performance of metallic conductors is affected by changes in temperature (for example, the bandwidth is reduced by reductions in temperature). Fibre-optic cable is not impacted by temperature.

#### 1.2.2 Disadvantages

#### • Limited Applications

Unlike metal-based communication systems, fibre-optic systems cannot be easily used with mobile communication facilities. Their use is restricted to fixed installations, thereby limited their application.

#### • Low-Power Sources Limit Transmission Distance

In general, an advantage of fibre-optic communication systems is their ability to carry signals for long distances with relatively little degradation. However, most commonly used light sources for fibre-optic communication systems are very low-power devices, which limits this advantage for those systems requiring high rates of data transmission. While devices operating at higher power levels are available, their cost is such that using a number of repeater amplifiers is a cheaper means of transmitting the signal over long distances.

#### • Limited Modulation

There is less flexibility in the modulation of the light source compare to the modulation of metal-based transmission. However, this is, to some extent, mitigated by the ability to modulate the subcarrier signals using more advanced techniques before the signals are applied to the optical fibre systems.

#### • Greater Fragility

Unlike optical fibres, metal-based cables are a tried and tested technology, having been used for many decades. Although protected by the casing, the glass in optical fibres is fragile. Microscopic cracking may occur over time; vibration testing has been performed but cannot fully replicate the conditions faced over time and include the impact of the effects of aging and the physical conditions to which the cables are exposed.

#### • Higher Initial Cost

The cost of optical fibre itself is low, considering the bandwidth it is capable of carrying. However, the associated cost of interfacing with networks and other equipment necessitates a higher initial than metal-based communication systems.

#### • More Expensive Maintenance

The reliance on total internal reflection of fibre-optic cable necessitates the use of more specialist, expensive equipment and skilled labour for maintaining the infrastructure and repairing any damage that arises.

#### • Susceptibility to Nuclear Radiation

Ionizing radiation is known to darken glass; in optical fibres, this increases signal attenuation. As long as the dose to which the fibre is exposed is not too high, the attenuation decreases over time (in the order of decades). The speed and extent of attenuation loss are greater the harder the glass; harder glass also takes longer to recover.

#### 1.3 Aims and Objectives

The aim of this project is to design and subsequently implement in hardware the Offset Pulse Position Modulation (Offset PPM) technique, applied over a fibre-optic link. There are four intermediate objectives of the research; these are described below.

# • To implement the Offset PPM encoder/decoder and practically verify some of the theoretical models

No practical Offset PPM encoder/decoder has been constructed to date. Many PPM formats that have previously been proposed have advanced no further than the theoretical stage, if the Offset PPM is to become a reality, hardware Offset PPM encoder/decoder must be implemented to prove that the Offset PPM system can occur in real time. Therefore, this objective is to construct the Offset PPM encoder/decoder using low-cost components; this in itself takes it a step beyond most other PPM schemes.

#### • To confirm theoretical predictions with measurements

It is necessary to compare the output of the Offset PPM encoder/decoder with the predicted output. The results of this comparison with theory will verify both that the encoder generates correct Offset PPM sequences and that the decoder correctly decodes those sequences into Pulse Code Modulation (PCM).

# To Design and implement a complete Offset PPM communication system using an FPGA

As the Offset PPM encoder/decoder hardware use discrete component architecture and high frequencies, and in order to reduce the impact of internal and external interference, as well as distortions and delays, the Offset PPM encoder/decoder will be synthesized onto a Field Programmable Gate Array (FGPA).

#### • To confirm theoretical predictions with measurements (fibre optics).

The principal focus of this thesis is the investigation of the performance of the Offset PPM through optics. Therefore, an optical communication system was constructed; this system was used to determine the performance of the Offset PPM waveforms through Plastic Optical Fibre (POF). A clock sequence required in order for the PPM decoder to be able to decode the Offset PPM sequence into PCM format.

#### 1.4 Contributions

The main areas of original contribution are:

- ❖ The development of hardware implementation using electronic chips of the Offset PPM encoder and decoder, this shows that the Offset PPM scheme can be achieved for real time operation. Outcomes agree with theory.

- ❖ Established a computer programming using and ALTERA® Quartus II software to define the Offset PPM coding over optical channel is implemented and the outcome is simulated.

- Developed a VHSIC hardware description language (VHDL) source code for the Offset PPM system. A schematic and a full block description of the system are given.

- ❖ ALTERA® FPGA development board has been used to implement the VHDL designs for FPGA. It uses Cyclone® III series FPGA EP3C120F780. The complete design includes: FPGA clock control block, Phase-locked Loop (PLL) for clock generation and division, Pseudo Random Binary Sequence (PRBS) PCM data generation, Offset PPM encoder and decoder, and finally a Bit Error Rate Test (BERT) system which regenerates the original sent PRBS data sequence and uses logic gates to check if any errors have occurred by comparing the original sequence with the regenerated data sequence.

- ❖ An optical communication system (transmitter/receiver) design of the Offset PPM has been completed to operate over a highly dispersive POF link to use it with the Offset coding system.

- ❖ Established a practical implementation of the designed system by using ALTERA® Quartus II software, and Cyclone III Field Programmable Gate Array (FPGA) based DSP development board. The implementation of the optical system transceiver is done as well.

- ❖ Experimental tests have been performed in order to examine Offset PPM system performance in a real-time transmission link. Also to calculate the BER using HP 3780A Bit Error Rate Tester (BERT).

- ❖ Tested digital transmission measurement including BER was applied to Offset PPM optical communication system based on VHDL source code and Cyclone III Field Programmable Gate Array (FPGA). Software was used to simulate the system. The system has shown that it has the ability to detect and correct erasure and error symbols when they not overcome its limitations.

#### 1.5 Organization of the Thesis

The remaining chapters are briefly introduced in this section and each of the chapters is organized as follows:

Chapter 2 discusses the coding schemes in optical fibre communication system, their basics, advantages and disadvantages. Thereafter, a simple application of FPGA and VHDL was introduced.

**Chapter 3** tabulates the optical transmitter, optical receiver, optical amplifier, and the optical fibre. It reports different OFDM design kernels.

**Chapter 4** introduces the Offset PPM as a new technique of PPM. Afterwards, the digital errors that affect the Offset PPM are described.

**Chapter 5** reports the electronic design stage and implementation process of both the Offset PPM encoder and Offset PPM decoder.

**Chapter 6** introduces the Cyclone III development board and SMA Breakout Cable with the lists of features of the board and specific information. The VHDL circuits design for the Offset PPM encoder and decoder system. After that, the two main full implementations of Offset PPM system were defined.

**Chapter 7** explores the POF that is used as an optical channel, and describes the optical transmitter, optical receiver, and a voltage comparator. The practical design and implementation of the system were discussed.

Chapter 8 summarizes the conclusions of this study with some recommendations for future studies.

#### 2 Literature Review

#### 2.1 Introduction

This chapter reviews the current understanding of the fundamental results of coding and modulation that were used in optical communication. The PPM schemes have been discussed with more details in order to give a full vision of using these techniques. Moreover, the purpose of this chapter is to present the comparison between FPGA and Microcontroller. In the end of this chapter, the fundamental of VHDL software and its relationship with FPGA has been defined.

#### 2.2 Coding Schemes in Optical Fibre Communication System

There are a wide range of coding schemes used in optical fibre communication systems; some of them and their associated advantaged and disadvantages are discussed below.

#### On-Off Keying (OOK)

On-off keying, the most basic form of modulation, is cheap to implement and requires little power. The optical power is modulated according to the (binary) data input signal, and is not dependent on the presence of a carrier wave. Aside from its use in optical fibre communication systems, it is commonly utilised in remote control systems and in RF carrier waves (Babar et al., 2017).

#### • Digital Pulse Position Modulation (DPPM)

DPPM (Calvert, Sibley, & Unwin, 1988; R. Cryan, Unwin, Garrett, Sibley, & Calvert, 1990; I Garrett, 1983; Ian Garrett, 1983; Gol'dsteyn, 1980; Massarella & Sibley, 1992; M. J. Sibley, 1993) is a technique that offers superior sensitivity than OOK, albeit at the expense of higher bandwidth and line rate. In common with OOK, it is an inexpensive and uncomplicated scheme, the main motivation for its development being to increase transmission efficiency by better exploiting the available bandwidth available in optical fibre communication systems. The increase in data transfer

rate can be significant – for example, when using 64 slots and encoding 6 bits of data, the maximum rate is over ten times that achieved with OOK.

M bits of data are coded into a single pulse; this pulse occupies a time slot, of which there are 2<sup>M</sup> in a block. In order to reduce the impact of channel dispersion – which may cause Inter-frame Interference and Inter-Symbol Interference (IFI and ISI respectively) a guard interval of one or more empty time slots may be inserted at the end of a frame. While the increased data transfer rate is desirable, the increased bandwidth used by DPPM places extra demand on the processing electronics, restricting its use in some applications.

#### • Shortened Pulse Position Modulation (SPPM)

SPPM, described by (R. A. Cryan, 2010) is a coding M bits of OOK data into  $n = 1 + 2^{M-1}$  bits. The scheme was first suggested for use in the context of subsea wireless optical communication systems.

#### • Overlapping Pulse Position Modulation (OPPM)

A modification of DPPM, Overlapping Pulse Position Modulation (OPPM) is a scheme in which overlap between adjacent pulse positions is permitted Modulation (Calderbank & Georghiades, 1993; H. Shalaby, 1993; H. M. Shalaby, 1999). This concept enables a higher transmission rate than DPPM despite using a lower bandwidth, provides signals that are easily decoded and also has a relatively low cycle. However, these positive attributes are at the expense of a loss of orthogonally and, given that the frame length must vary according to the degree of overlap that occurs, the synchronization procedures are more restricted.

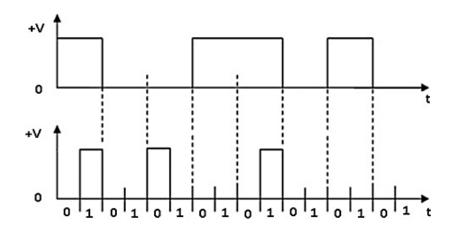

#### • Pulse Position Modulation

(Liu, 2002) presented pulse position modulation (PPM) as in figure (2.1), describing it as a method of encoding information in a signal through variation of pulse position. While the unmodulated

signal comprises a train of pulses whose amplitude, duration and frequency are all constant, their positions are changed during modulation to reflect the information that is being encoded. In PPM, the position of the pulse is modulated relative to its unmodulated relative to its unmodulated position. Digital pulse modulation results in an efficient system characterized by high security, robustness, integration, reliability and overall performance; the less Ko by noise, described by Ko (2001).

There is a trade-off between final line rate and the enhanced consumption of bandwidth that PPM achieves through the representation of m bits of data by a single pulse in PMM. PPM must transport the same quantity data as PCM in an identical time frame. In order to do this, for a PCM bit interval with a bit time of  $T_b$ , the time frame is  $mT_b$ , there are  $2^m$  PPM time slots. Therefore, to meet the requirement of the same data traffic flow, the PPM rate must be  $2^m / m$  faster than the PCM (H. M. Shalaby, 1999; M. J. Sibley, 1993, 2003, 2004; M. J. Sibley & Massarella, 1993; Zwillinger, 1988). The tolerance to the effect of noise from signal distortions and communication channels increases with the use of digital communication systems. Such systems are also very reliable as they are able to use powerful coding schemes to control errors and encryption algorithms to increase security. Analogue communication systems are less efficient than digital ones; PPM sacrifices bandwidth for a higher signal to noise ratio. It is vital that communication is performed using effective systems in order to retain the correct meanings of the messages being transferred. To lose these meanings between source and transmitter and receiver is to create serious problems, as all messages are different. For a communication system to be effective, the information source, its transmitter, the carried signals and the receiver must all be engaged; considered as a whole, these elements and the associated processes may be discrete, continuous or mixed.

Figure 2-1 Pulse Position Modulation (Liu, 2002)

#### • Multiple Pulse Position Modulation (MPPM)

First proposed as a viable means of increasing the efficiency of bandwidth usage in optical PPM (Sugiyama & Nosu, 1989), Multiple Pulse Position Modulation (MPPM) has also been investigated for dispersive optical channels (Nikolaidis & Sibley, 2007, 2010; M. Sibley, 2004). As demonstrated by Sugiyama and Nosu, MMPM optical pulses are, as shown in figure (2.2), transmitted in one single block in multiple pulses. Using this method, the same transmission efficiency is achieved but using approximately half the transmission bandwidth in optical PPM – that is, the band-utilization efficiency is approximately doubled. Sibley demonstrated the MPPM to be one of the most bandwidth-efficient PPM coding schemes in his analysis of MMPM operating over graded-index plastic optical fibre, producing a sensitivity equivalent to that of digital PPM but without the same bandwidth expansion. The MPPM scheme utilizes multiple pulses in a frame, their positions determined by the original PCM word.

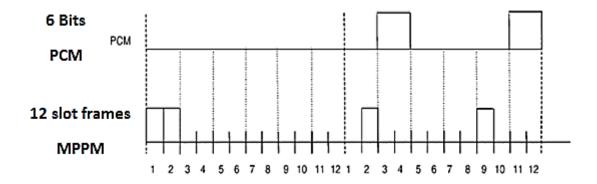

Figure 2-2 Conversion of PCM (top trace) to Multiple PPM double pulses per frame (Bottom trace)

In figure (2.2), (12/2) MPPM in which a 12-slot frames using two data pulses to code 6 bits of PCM is shown. In this example, linear mapping translates PCM 000000 to 1, 2 (that is, pulses in slots 1 and 2), whereas the PCM word 010001 translates to 2, 9. The line rate for this (12/2) code is twice the line rate of the PCM. Higher order codes will result in greater reductions, as shown by (Sugiyama & Nosu, 1989). For example, (15/4) cam code 10 bits of PCM; this results in a line rate 1.5 times that of the PCM line rate.

In addition, the error performance was analysed, the Maximum Likelihood Sequence Detection (MLSD) scheme as introduced, simplifying error performance prediction using bounds. The power of multiple PPM was found to be more efficient than digital PPM, as was its bandwidth utilization. MPPM showed a higher predicted sensitivity (0.58 bits per photon compared to 0.5 bits per photon respectively when operating at an error rate of 1 in 10<sup>9</sup>). As with previous coding schemes, MPPM was found to be susceptible to erasure, false alarm and wrong-slot errors. The causes of this may be attributable to optical pulse detection at the receiver, to dispersion of the photons trough the transmission channel or to both. The application of appropriate MLSD can increase the sensitivity of MPPM.

#### • Digital Pulse Position Modulation (DPPM)

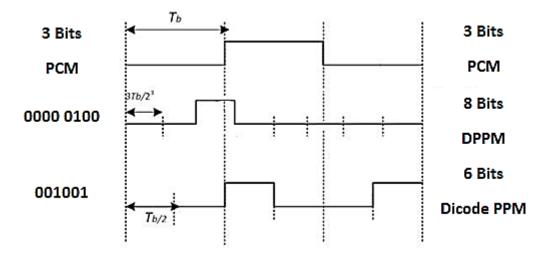

The digital PPM technique uses  $log_2M$  data bits mapped onto one of M possible symbols in each frame, such that N bits PCM is encoded by one pulse in one of M time slots (where,  $M=2^N$ ). Within each time slot, the single pulse has a constant power and is repeated every T seconds. It is then followed by M-1 empty slots. Each frame's length is equal to the length of the PCM time frame. The DPPM coding scheme is based on the position of each pulse within the symbol; Figure (2.3) shows the encoded pulse position related to the decimal value of each data bit. Inter-frame interference (IFI) may be eliminated by the insertion of a number of guard intervals to a PPM frame. This will also improve the performance of the system (R. Cryan et al., 1990; M. J. Sibley & Massarella, 1993). If  $T_b = 1/B$  represents the PCM bit time, B the original data rate and N the number of PCM bits, the digital PPM slot duration is given by:

$$T_s = \frac{N.T_b}{2^N} \tag{2.1}$$

Decoding of the received pulses and recovery of the PCM information is performed in the presence of both slot and symbol synchronization. The time at which the PPM pulses reach the crossing point is determined by a threshold signal detector; the arrival time may be influence by signal interference, as described by (M. J. Sibley & Massarella, 1993).

Figure 2-3 Conversions of PCM data (top trace) into DPPM (Middle trace) and DiPPM (Bottom Trace)

#### • Dicode Pulse Position Modulation

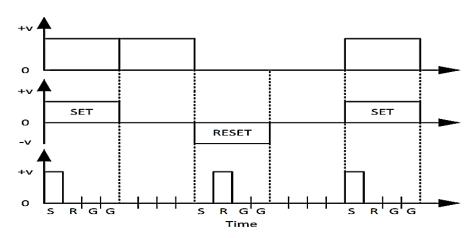

Dicode Pulse Position Modulation (DiPPM) is an appealing coding scheme in that both coding and implementation are straightforward. In the absence of a change in the PCM signal, a zero pulse is present, a logic one to logic zero data transition is coded by negative (-V) and a logic zero to logic one is coded by positive (+V) in the dicode technique. Four slots are used to code a single bit of PCM. However, two further signals are converted into two pulse positions in data frames – these are the SET and RESET signals as shown in figure (2.4). Should there be no data transition present, there is no pulse. A transition from zero to one result in a SET(S) pulse, while a transition from to one to zero results in a RESET(R) pulse (Al-Nedawe, 2014). When the PCM data is constant, no signal is transmitted (M. J. Sibley, 2003). As a single slot in PCM can be coded into a single S or R slot in DiPPM, the power requirement is lessened. As with other schemes, guard intervals can be inserted to the time slot to lessen the impact of ISI. DiPPM,  $T_s$  is expressed as follows:

$$T_s = \frac{T_b}{2 + gu} \tag{2.2}$$

Whereis the guard intervals. gund is the original data rate aB denotes the PCM bit time,  $T_b = 1/B$  Just two slots are used to transmit one bit of PCM in a zero-guard DiPPM. In this situation, the line rate becomes twice that of the original PCM; both the resultant speed and required bandwidth are lower than those of digital PPM (Sibley, 2003b).

Figure 2-4 Conversion of PCM data (top trace) into dicode (Middle trace)

Table (2.1) shows the four symbols in the DiPPM alphabet (S, R, and 2N for 00 and 11 transitions). A transmitted S pulse can be followed only by R or N, both having a probability of 1/2. The maximum DiPPM run could be R, nN and S if the coding of the original PCM line is such that the run of like symbols is limited to n.

**Table 2.1 DiPPM Symbol Alphabet**

| PCM | Probability | DiPPM    | Symbol |

|-----|-------------|----------|--------|

| 00  | 1/4         | No pulse | N      |

| 01  | 1/4         | SET      | S      |

| 10  | 1/4         | RESET    | R      |

| 11  | 1/4         | No pulse | N      |

According to this condition, the probability of the next pulse (R symbol) is unity – its presence is guaranteed at the end of a series of N symbols that is n symbols long. If the pulse originally transmitted is an R pulse, a similar situation can arise (R. Cryan & Unwin, 1993).

#### • Duobinary Pulse Position Modulation

The Duobinary Pulse Position Modulation (DuoPPM) signalling technique offers a significant reduction in bandwidth expansion in comparison to digital PPM, as the line rate is twice that of the original NRZ OOK data, as shown in figure (2.5) (Mostafa, Sibley, & Mather, 2014). In the scheme, a constant stream of data of logic 1 produces a pulse in slot 1 of the DuoPPM slot 1, which a constant stream of data of logic 0 produces on in slot 0. When the data is in transition from logic 1 to logic 0 and vice versa, no pulse is transmitted in the frame, as shown in figure (2.5). The nature of this scheme reduces the ISI, negating the need for guard slots; a new MLSD and correction technique ensure a particular error type can be wholly eliminated (Mostafa, 2015).

Figure 2-5 Conversion of OOK data (top trace) into DuoPPM (bottom trace)

### • Pulse Amplitude Modulation (PAM)

The sophistication of the fundamental pulse amplitude modulation (PAM) scheme, shown in the figure (2.6), in which the information is transmitted in the pulse amplitude – can be increased by utilizing more amplitude levels. For example, in Quadrature Pulse Amplitude Modulation (QPAM, or QAM), four amplitude levels can be used for each of four groups – each group contains two signal bits (00, 01, 10 and 11). Pulse-amplitude modulation is the basis of direct-sequence spread spectrum (DSS) (Mazzini, Traverso, & Nowell, 2017).

Figure 2-6 PAM (A), PFM (B), PPM (C) and PDM (D)

# • Pulse Density Modulation (PDM) or Pulse Width Modulation (PWM)

A means of converting analogue signals into digital signals, pulse density modulation (PDM) is a technique in which the relative pulse density is proportional to the magnitude of the input, analogue signal. Pulse-width modulation, PWM, is a special case of PDM that is often used in motor control as shown in figure (2.6) (Li, Fang, Chen, Wang, & Tang, 2017).

# Pulse Frequency Modulation (PFM)

Pulse frequency modulation (PFM) utilizes the modulating wave to frequency modulate a pulse-generating circuit by varying the repetition rate of fixed-duration pulses. (In this respect, it differs from PWM and PDM, in which the frequency remains constant but the width of square pulses is varied.) As an example, with a pulse rate of 800 pulses per second (p/s) for a signal voltage of 0 V, the pulse rate may step up to 900 p/s for maximum positive signal voltage and step down to 7000 p/s for maximum negative signal voltage. The PFM generation circuitry required for this method of modulation is complicated, requiring a stable, frequency modulated oscillator to drive a pulse generator. As a result, PFM is not extensively used as shown in figure (2.6).

#### • Pulse Code Modulation (PCM)

Illustrated in the figure (2.7), pulse code modulation (PCM) is a scheme used in the transmission of analogue data in binary form that is not dependent on the analogue waveform's complexity. Therefore, it is suitable for the transfer of all types of analogue data, including music, video, voice and telemetric data.

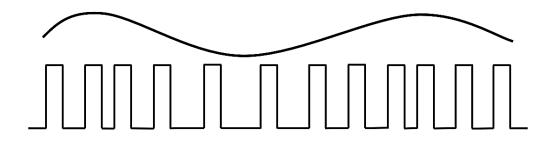

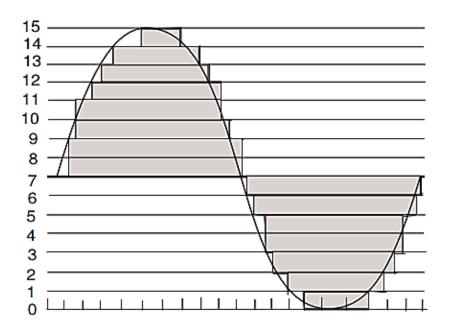

**Figure 2-7 Pulse Code Modulation**

At the transmitter, the amplitude of the analogue waveform is sampled at a regular frequency that is several times greater than the maximum frequency of the waveform (that is, the Nyquist rate) to form the PCM. The amplitude at each sampling point is quantized (that is, it is rounded to the nearest binary level) and represented by a binary word of at least two binary bits. To decode the PCM, a pulse code at the receiver converts these binary numbers into pulses with the same quantum levels as the levels in the modulator; the pulses are processed further to restore the analogue waveform. Adaptive Differential Pulse Code Modulation (ADPCM) is a technique for the conversion of analogue information or sound into binary information. ADPCM is defined by the International Telecommunication Union (ITU). Frequent samples of audio signals are taken and the values of the sampled audio modulation are expressed in binary terms, resulting in a lower bit rate,

enabling both digital and voice data to be sent simultaneously. Unlike PCM, on which ADPCM is a variation, only the difference between adjacent samples is transmitted. There are several applications of ADPCM, including the storage of information (such as image, text and code) on data storage media, sending audio on long-distance fibre-optic lines, digital cordless telephony and in radio/wireless local loops (Uddin, Ansari, & Naaz, 2016).

# • Sigma-delta modulation ( $\Sigma \Delta M$ )

Sigma-Delta modulation ( $\Sigma\Delta M$ ) is a technique utilized in encoding high resolution signals into lower resolution signals through pulse-density modulation and has become increasingly popular in electronic components recently. Examples of Sigma-Delta modulation applications are frequency synthesizers, motor controls, analogue-to-digital and digital-to-analogue convertors and switched mode power suppliers. Delta-Sigma modulation, first demonstrated in the early 1960's, can produce very high resolution when used in Analogue to Digital Converter (ADC) or Digital to Analogue Converter (DAC) circuits. However, although data conversion was one of its earliest and commonest uses being in data conversion, it has only been with more recent silicon-based technological developments that it has come into more widespread use as these have facilitated implementation on low-cost processes on digital integrated circuits (Zerek, Elfituri, & Emhimid, 2017).

# • Continuously Variable Slope Delta Modulation (CVSDM), also called Adaptive-Delta Modulation (ADM)

First proposed by (Greefkes & Riemens, 1970), Continuously Variable Slope Delta Modulation (CVSD, or CVSDM) is a method of voice coding and is a delta modulation with variable step size. That is, it is a special case of adaptive delta modulation. The technique encodes at 1 bit per sample – that is, audio sampled at 16 kHz is encoded at 16 bit/s. During the encoding process, the step size is continuously adapted. This has two benefits – increasing the step of quantization when the signal

changes rapidly avoids slope overload, while decreasing the step of quantization reduces granular noise when the signal is constant. A reference sample and step size is maintained by the encoder, to which each input sample is compared and the reference sample adjusted if the input sample varies in size from the reference. If the input sample is smaller than the reference sample, the encoder emits a 0 bit and subtracts the step size from the reference sample. Conversely, if the input sample is larger, the encoder emits a 1 bit, adding the step size to the reference sample. Furthermore, the previous N bits of the output are retained by the encoder in order to determine adjustments to the step size (typically 3 or 4 bits are retained). If the retains bits are all 0s or all 1s, the step size is doubled; otherwise, the step size is halved. For each input sample processed, the step size is adjusted. At the decoder, the adjustment process is reversed. That is, the step size is added or subtracted from the reference sample according to the bit stream. The reconstructed waveform comprises the sequence of adjusted reference samples; the step size is doubled or halved according to the same logic as was used in the encoder.

#### • Colour Coded PPM (CCPPM)

Davidson and Bayoumi first proposed colour coded PPM (CCPPM) in a number of publications (F. Davidson, 1985; F. Davidson & Bayoumi, 1987). Higher energy efficiency (in nats per average number of received photons per pulse) was found than in an ordinary PPM system using CCPPM, which utilizes an overlapping centre frequency for each individual PPM data slot. A further development of the technique combining laser diodes operated in different wavelengths with a pulse position modulated (PPM) format was considered by (R. M. Gagliardi & Kim, 1988). That is, they combined several laser diode sources into a single beam for digital PPM transmission, using a set of three individual system architectures. In one system, the PPM pulse comprised a number of optical frequencies, combined prior to the digital PPM modulator into a single PPM data pulse. In architecture, each optical wavelength was combined after PPM modulation. In their study, the

influences of the number of wavelengths involved, the PPM coding level, the optical Signal to Nosie Ratio (SNR) and losses associated with the beam optics on the performance on the data rate were compared. Table (2.2) show the Generation of different types of coding from equivalent 3 bits of data

Table 2.2 Generation of different types of coding from equivalent 3 bits of data

| OKK | Digital   | Differential | Digital PIM | DH-PIM  | Offset | SPPM   | MPPM   |

|-----|-----------|--------------|-------------|---------|--------|--------|--------|

|     | PPM       | PPM          |             |         | PPM    |        |        |

| 000 | 0000 0001 | 0000 0001    | 1           | 100     | 0000   | 0 0001 | 1 1000 |

| 001 | 0000 0010 | 0000 001     | 10          | 1000    | 0001   | 0 0010 | 1 0100 |

| 010 | 0000 0100 | 0000 01      | 100         | 1000 0  | 0010   | 0 0100 | 1 0010 |

| 011 | 0000 1000 | 0000 1       | 1000        | 1000 00 | 0100   | 0 1000 | 1 0001 |

| 100 | 0001 0000 | 0001         | 1 0000      | 1100 00 | 1000   | 1 0001 | 0 1100 |

| 101 | 0010 0000 | 001          | 10 0000     | 1100 0  | 1001   | 1 0010 | 0 1010 |

| 110 | 0100 0000 | 01           | 100 0000    | 1100    | 1010   | 1 0100 | 0 1001 |

| 111 | 1000 0000 | 1            | 1000 0000   | 110     | 1100   | 1 1000 | 0 1100 |

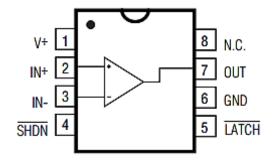

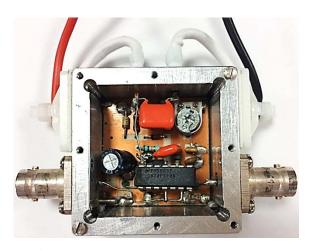

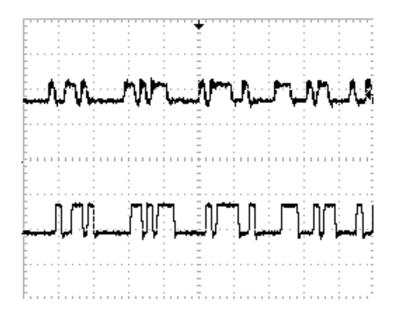

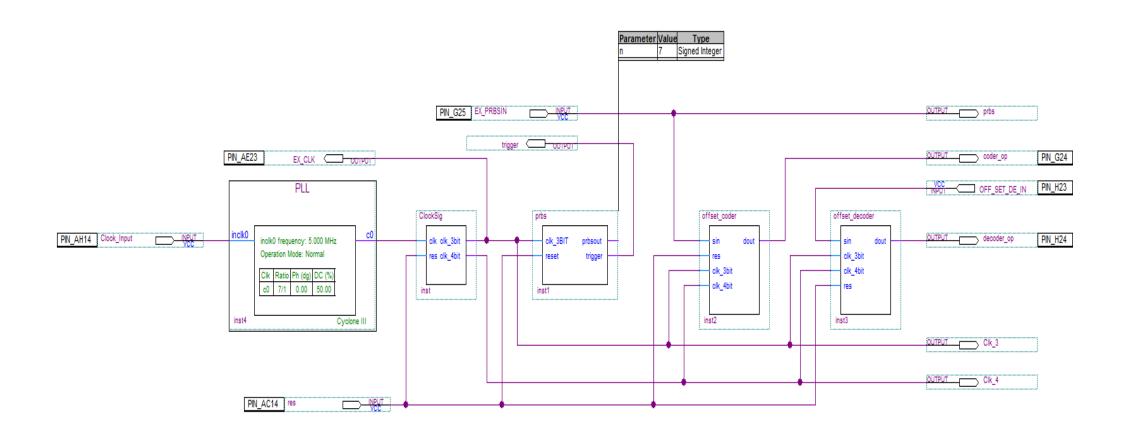

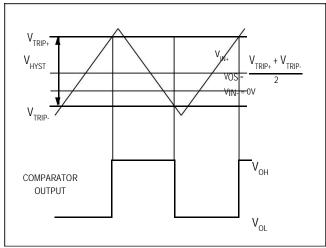

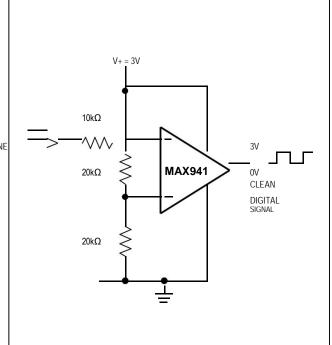

# 2.3 Timing Extraction and Synchronisation