#### **University of Huddersfield Repository**

Newall, Matthew

GPU cluster for acceleration of scientific and engineering applications in the context of higher education

#### **Original Citation**

Newall, Matthew (2015) GPU cluster for acceleration of scientific and engineering applications in the context of higher education. Masters thesis, University of Huddersfield.

This version is available at http://eprints.hud.ac.uk/id/eprint/23746/

The University Repository is a digital collection of the research output of the University, available on Open Access. Copyright and Moral Rights for the items on this site are retained by the individual author and/or other copyright owners. Users may access full items free of charge; copies of full text items generally can be reproduced, displayed or performed and given to third parties in any format or medium for personal research or study, educational or not-for-profit purposes without prior permission or charge, provided:

- The authors, title and full bibliographic details is credited in any copy;

- A hyperlink and/or URL is included for the original metadata page; and

- The content is not changed in any way.

For more information, including our policy and submission procedure, please contact the Repository Team at: E.mailbox@hud.ac.uk.

http://eprints.hud.ac.uk/

### GPU Cluster for Acceleration of Scientific and Engineering Applications in the Context of Higher Education

Author: Matthew NEWALL Supervisor: Dr Violeta HOLMES

A thesis submitted in fulfilment of the requirements for the degree of Masters By Research

> High Performance Computing School Of Computing and Engineering

> > February 2015

### Copyright Statement

- The author of this thesis (including any appendices and/or schedules to this thesis) owns any copyright in it (the Copyright) and s/he has given The University of Huddersfield the right to use such Copyright for any administrative, promotional, educational and/or teaching purposes.

- Copies of this thesis, either in full or in extracts, may be made only in accordance with the regulations of the University Library. Details of these regulations may be obtained from the Librarian. This page must form part of any such copies made.

- The ownership of any patents, designs, trade marks and any and all other intellectual property rights except for the Copyright (the Intellectual Property Rights) and any reproductions of copyright works, for example graphs and tables (Reproductions), which may be described in this thesis, may not be owned by the author and may be owned by third parties. Such Intellectual Property Rights and Reproductions cannot and must not be made available for use without the prior written permission of the owner(s) of the relevant intellectual Property Rights and/or Reproduction

### Abstract

Many fields of research now rely on High Performance Computing (HPC) systems which can process ever larger datasets, with increasing accuracy and speed. Many universities now provide a HPC service. Following the trend over the past few years of the worlds fastest supercomputers being accelerated using Graphical Processing Units (GPUs), there is a growing interest in the use of GPUs in Higher Education Institutions. The characteristics of GPUs make them excellently suited to any task exhibiting a high level of data parallelism. Recent developments in GPU technologies have focused on improving performance and integration in HPC, and for processing data other than display graphics.

To investigate the benefits such a system could have to the University of Huddersfield, a small GPU cluster has been deployed. The intention behind this thesis is to detail the deployment of the system and to demonstrate, through case studies, the required effort a potential user could expect in order to take advantage of it.

As a result of this work it can be demonstrated that even a modest GPU cluster can be of benefit to the University. The cluster is helping our researchers to analyse complex data using visualisation, and accelerating data processing.

### Acknowledgements

I would like first and foremost to thank my supervisor Violeta Holmes for her invaluable advice and support both day and night. Without her this project would not have been possible. I would also like to thank Paul Lunn from Birmingham City University for providing his software for the second case study, and for his contributions to publications based on this work. Thanks to Graeme Greaves from the Electron Microscopy Materials Analysis group at Huddersfield for providing data, And to Hussam Muhamedsaleh for allowing use of his software in the final case study. Finally i would like to thank my collegues Ibad Kureshi, Stephen Bonner and John Brennan for their technical and logistical assistance.

# Contents

| Сс  | oyright Statement                                                                                                                                                                                                                                                                                                                                                                                                                   | 1                                      |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| Ab  | stract                                                                                                                                                                                                                                                                                                                                                                                                                              | 2                                      |

| Ac  | nowledgements                                                                                                                                                                                                                                                                                                                                                                                                                       | 3                                      |

| Lis | t of Figures                                                                                                                                                                                                                                                                                                                                                                                                                        | 6                                      |

| Lis | t of Tables                                                                                                                                                                                                                                                                                                                                                                                                                         | 7                                      |

| Ab  | previations                                                                                                                                                                                                                                                                                                                                                                                                                         | 8                                      |

| 1   | Introduction and Background 1.1 Aims and Objectives                                                                                                                                                                                                                                                                                                                                                                                 |                                        |

| 2   | Literature Review         2.1 GPUs as general purpose processors         2.1.1 GPU Programming Frameworks         2.1.1.1 Nvidia CUDA         2.1.1.2 openCL         2.2         Obstacles to using GPUs for scientific calculations         2.3         Scientific applications of current GPU technology         2.4         HPC Systems which use GPUs         2.4.1 TITAN - Oak Ridge National Laboratory         2.4.2 Emerald | 15<br>15<br>16<br>17<br>18<br>19<br>20 |

| 3   | Vega GPU Cluster         3.1       The Microsoft Windows HPC Platform         3.2       Cluster Layout         3.3       Deployment         3.4       Testing                                                                                                                                                                                                                                                                       | 23<br>24                               |

| 4   | Platforms and Programming Environments for Scientific Data Visualisation         and Processing         4.1 Visualisation         4.2 Multi-Node parallelism                                                                                                                                                                                                                                                                        | <b>31</b><br>32                        |

|   | 4.3                                                                               | GPU Programming Framework                                                                                                                                                                                                    | 33                          |  |

|---|-----------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|--|

| 5 | 5.1<br>5.2                                                                        | e Study 1: Visualisation of large datasets         Electron Microscopy Data         Visit         Evaluation of Results                                                                                                      |                             |  |

| 6 | <b>CUD</b><br>6.1                                                                 | Study 2: Accelerated Processing of Radio Telescope Data Using         A         The SETIFFT software         6.1.1 Optimising CUDA performance         6.1.2 Using MPI to increase performance         Evaluation of Results | 42                          |  |

| 7 | <b>fero</b><br>7.1<br>7.2                                                         | e Study 3: CUDA Accelerated Analysis of Wavelength scanning Inter-<br>metry Data<br>The Interferometry Software                                                                                                              | <b>46</b><br>46<br>47<br>48 |  |

| 8 | Con                                                                               | clusion                                                                                                                                                                                                                      | 50                          |  |

| 9 | Furt                                                                              | her Work                                                                                                                                                                                                                     | 52                          |  |

| A | SILC                                                                              | OWRITE tool                                                                                                                                                                                                                  | 53                          |  |

| В | SET                                                                               | IFFT sonification code                                                                                                                                                                                                       | 58                          |  |

| С | Wavelength Scanning Interferometry Software 74                                    |                                                                                                                                                                                                                              |                             |  |

| D | GPU Cluster for Accelerated processing and Visualisation of Scientific<br>Data 90 |                                                                                                                                                                                                                              |                             |  |

| E | Deliv                                                                             | vering faster results through parallelisation and GPU acceleration                                                                                                                                                           | 97                          |  |

References

110

# **List of Figures**

| 2.1        | Architecture of the Nvidia GeForce 6800 GPU, showing pipelined design<br>with separate units for Vertex processing, Rasterization and Blending |          |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 2.2        | (Nvidia, 2006)                                                                                                                                 | 14       |

|            | eral purpose streaming processors (Lindholm et al., 2008)                                                                                      | 14       |

| 2.3        | A representation of the graphics pipeline as implemented on CUDA GPUs (Luebke and Humphreys, 2007)                                             | 15       |

| 3.1<br>3.2 | Current VEGA hardware layout and network topology                                                                                              | 24       |

| 3.3        | nostic tests pass 6. Checking CUDA functionality                                                                                               | 26<br>27 |

| 3.4        | Simple MPI test program, based loosely on the example from Matto-                                                                              | 21       |

|            | torang (2009)                                                                                                                                  | 28       |

| 3.5        | Output from MPI test program when run on all cores                                                                                             | 29       |

| 3.6        | GPU test programs included with CUDA toolkit (Nvidia, 2013a), from top to bottom: Device Query, Testing Aligned Types, Matrix Multiplication   | 30       |

| 5.1        | Visualisation method before Vislt                                                                                                              | 36       |

| 5.2<br>5.3 | Program flow for the SILOWRITE code                                                                                                            | 37       |

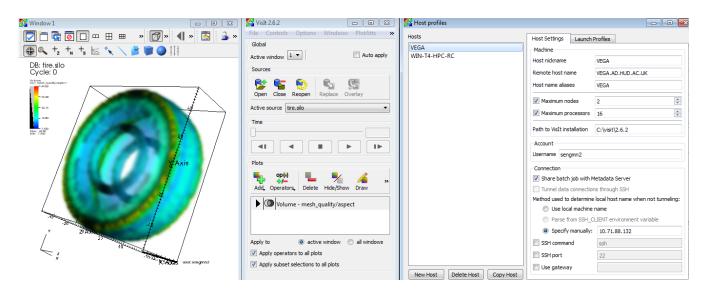

|            | sheet, 2D Mesh in Vis<br>It, 3D mesh in Vis<br>It, 3D contour mesh in Vis<br>It $% \mathcal{A} = \mathcal{A} = \mathcal{A} + \mathcal{A}$      | 38       |

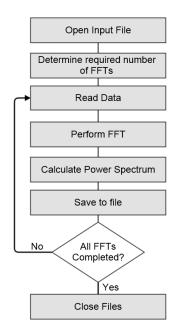

| 6.1        | Program flow of the SETIFFT software                                                                                                           | 40       |

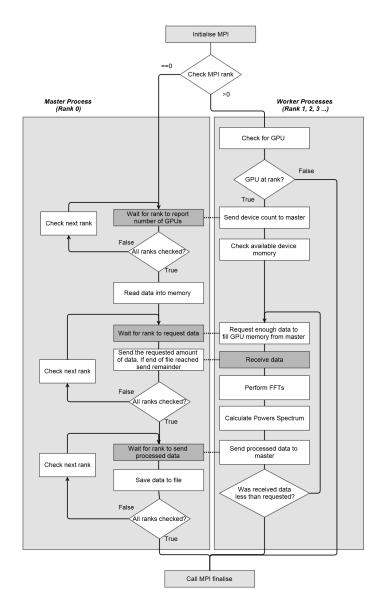

| 6.2        | Program flow of the initial MPI program                                                                                                        | 43       |

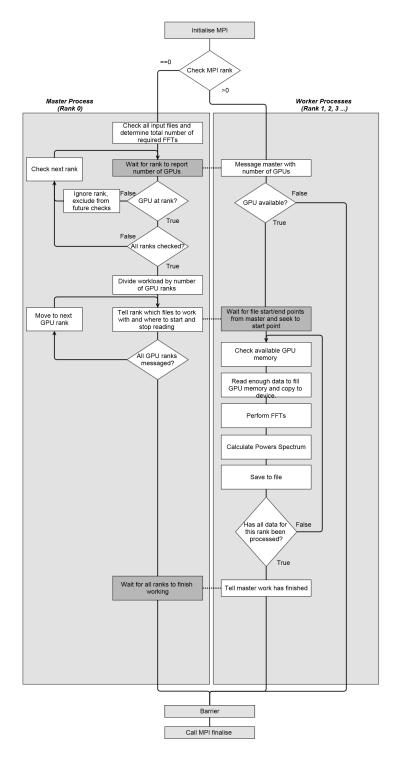

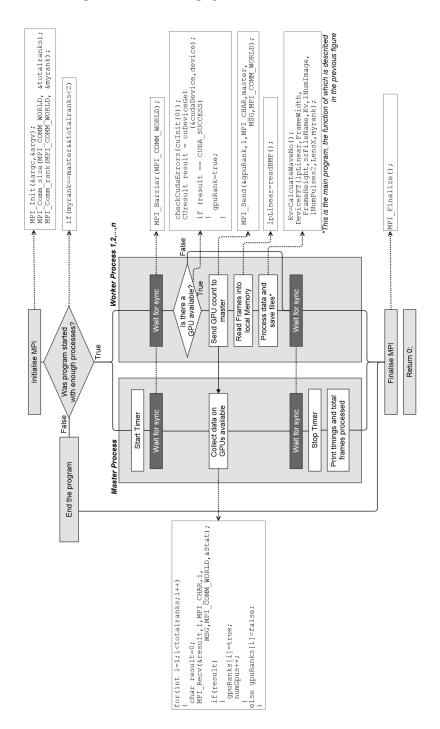

| 6.3        | Program flow of the final MPI version                                                                                                          | 44       |

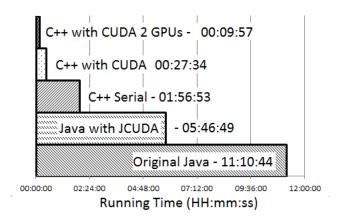

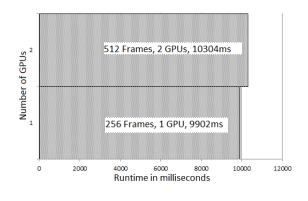

| 6.4        | Total running times of each version                                                                                                            | 45       |

| 7.1        | Program flow for the original CUDA code                                                                                                        | 47       |

| 7.2        | Program flow for the MPI version using multiple GPUs                                                                                           | 48       |

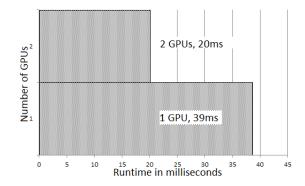

| 7.3        | Total running times for each version                                                                                                           |          |

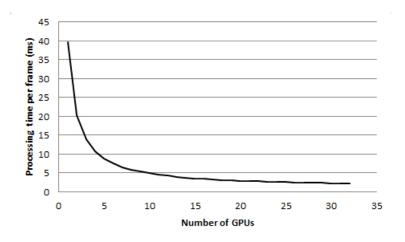

| 7.4        | Representative per-frame processing time                                                                                                       | 49       |

|            |                                                                                                                                                |          |

# **List of Tables**

| 3.1 | Hardware available for VEGA                                           | 23 |

|-----|-----------------------------------------------------------------------|----|

| 6.1 | Timings for original JAVA program                                     | 40 |

| 6.2 | Timings for Java program with wrapped CUDA functions                  | 41 |

| 6.3 | Timings for C++ with serial FFT                                       | 41 |

| 6.4 | Timings for C++ with CUFFT                                            | 41 |

| 6.5 | Timings for C++ with CUFFT and MPI, running on multiple GPUs          | 42 |

| 6.6 | Timings for C++ with CUFFT and MPI, running on multiple GPUs          | 42 |

| 6.7 | Read/write time for the MPI software when reading from different num- |    |

|     | bers of files                                                         | 45 |

# **Abbreviations**

| GPU  | Graphics Processing Unit            |  |  |

|------|-------------------------------------|--|--|

| HPC  | High Performance Computing          |  |  |

| AD   | Active Directory                    |  |  |

| QGG  | QueensGate Grid                     |  |  |

| CUDA | Compute Unified Device Architecture |  |  |

| MPI  | Message Passing Interface           |  |  |

| API  | Application Programming Interface   |  |  |

| CFD  | Computational Fluid Dynamics        |  |  |

|      |                                     |  |  |

### **Chapter 1**

## Introduction and Background

High Performance computing systems are now well established as an essential tool for research and analysis in Higher Education. A High Performance computing system is one which uses multiple computers to carry out one task, through parallel processing. Many Universities have some kind of HPC provision. At the University of Huddersfield a number of HPC systems have been deployed for the use of researchers and students (Kureshi, 2010). These systems are used regularly for tasks such as large CFD simulations, running MPI software, image rendering and more. However, the fastest computer HPC systems now include Graphic Processing Units (GPU) (Top500, 2013a). This research is attempting to answer the following questions

- Why do we need an alternative to CPU systems for scientific processing

- Why are GPUs so suited to this task

- What issues would be faced in deploying a GPU system.

- How would such a system support research in a Higher Education institution such as the University of Huddersfield.

Aside from the university of Huddersfield, many HE institutions have some kind of HPC system. However, while GPUs are seeing widespread adoption in research and scientific institutions, they still remain comparatively rare in HE.

#### 1.1 Aims and Objectives

The overall goal of this project was to investigate the viability of a GPU cluster to compliment the HPC provision available at the University of Huddersfield. The key objectives for success were:

- Investigate the application of GPU technologies in HPC systems.

- Evaluate existing GPU systems in the context of Higher Education to support scientific research.

- Deploy a GPU cluster within a HE institutional grid.

- Investigate different platforms and programming environments for the purpose of highly parallel task and data processing and visualisation.

- Evaluate the suitability of the GPU cluster using representative case studies.

- Propose possible future developments of the system to accelerate HE scientific research.

The final outcome of this project was considered to be a functional GPU cluster, successfully integrated as part of the HPC provision at the university, justified through a number of case studies.

#### 1.2 Methodology

In order investigate how best to achieve the project aims and objectives, a comprehensive literature review was conducted, A GPU cluster was deployed and integrated into the campus grid, and case studies were carried out to evaluate its usefulness in supporting the visualisation and processing of data.

The result of this study is presented in this thesis and is organised as outlined below:

Chapter 2: Investigate existing HPC sytems, the use of GPUs in such systems and studies on existing GPU clusters, Cluster Middlewares, GPU programming models and software.

- Chapter 3: Design and deployment of a GPU cluster is described.

- Chapter 4: Outlines a selection of appropriate software, platforms, and programming environments for visualisation and processing of data, based on the literature.

- Chapter 5,6, and 7: Presents the results of testing the usefulness and suitability of the cluster through three representative case studies.

- Chapter 8 and 9: Evaluate the outcomes of the project and propose future developments.

### **Chapter 2**

### **Literature Review**

#### 2.1 GPUs as general purpose processors

There have been numerous efforts up to this point to use GPUs as general purpose processors. An important concept to bear in mind when establishing the suitability of an algorithm or program for processing on a GPU is arithmetic intensity, which as stated by Harris (2005), is the ratio of computation to bandwidth. This is significant as computational speed currently increases more rapidly than communication speed, so memory access latency will negate potential computational speedup. Problems with a high arithmetic intensity are those which exhibit a high level of data parallelism, and have minimal dependency between data points.

Fung and Mann (2005) present an API, OpenVIDIA, which allows a user to leverage GPUs to perform computer vision and Image processing tasks. The API uses openGL to interact with the GPUs. In an image processing or filtering operation, the filters are written as shaders in Cg (described in the paper as "fragment programs"), "to apply these fragment programs to input images, the input images are initialized as textures and then mapped to quadrilaterals." (Fung and Mann, 2005, chap. 3.1). The architecture of the GPU allows each pixel to be processed in parallel providing a significant speed boost. The same paper describes an implementation of a computer vision algorithm which uses the full pipeline of the GPU, a Hough Transform. An edge detection is performed on the GPU as a filter operation. The coordinates of these edge pixels are then fed back to the GPU as an array of vertices, these vertices are further processed

on the GPU through its hardware projection matrix, which has been programmed to perform the Hough Transform (Fung and Mann, 2005, chap. 3.2).

Efforts have also been made to abstract the process of GPU acceleration to high level operations. Tarditi et al. (2006) describe Accelerator; "a system that uses data parallelism to program GPUs". Accelerator allows programmers to accelerate suitable parts of their code using GPU accelerated functions, without exposing any aspect of the GPU. Unlike the traditional approach, which would involve compiling the data-parallel parts of the program as shader programs in native code, Acellerator compiles GPU parts of the code on the fly at runtime. Using this software Tarditi et al. (2006) were able to demonstrate an acceleration of up to 18 times over native C code running on a CPU. While it does not match the performance of hand written GPU code, its simplicity of use makes it an important step towards accessible GPU acceleration.

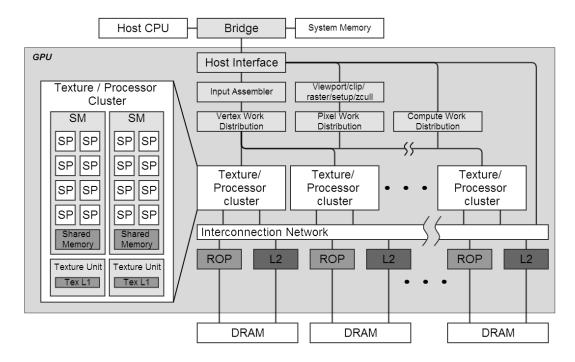

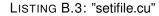

As the use of GPUs as accelerators became increasingly common, GPU manufacturers started to change the design of their units accordingly. Fig. 2.1 Shows the architecture of the Nvidia GeForce GPU; it is a design highly specialised to graphics with hardware designed to fulfil specific parts of the graphics pipeline, as was the case most GPUs up to this point. As can be seen in Fung and Mann (2005, chap. 3.2), and Tarditi et al. (2006, chap. 3.1), programming GPUs required determining which part of the graphics pipeline was best suited to the problem, and could require vastly different approaches depending on which part of the GPU was targeted. To use the full pipeline often meant numerous copies to and from host memory as it was not possible to utilise the internal transports on the GPU.

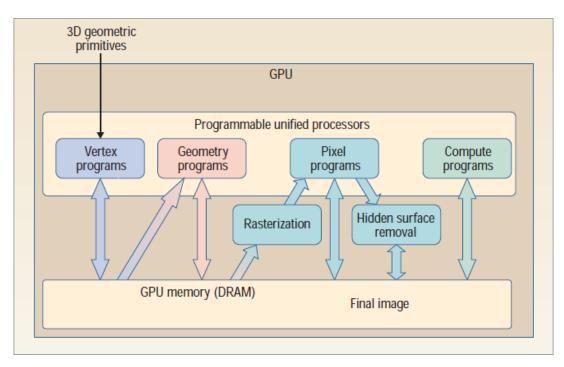

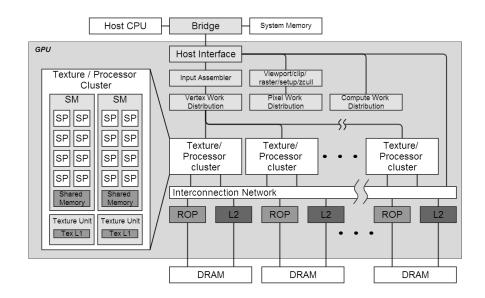

This changed with the Nvidia GeForce 8800, which was the first card based on the propriety compute unified device architecture (CUDA). As can be seen in Fig. 2.2, CUDA devices replace the hardware pipeline with high numbers of 'stream processors'. As seen in Fig. 2.3, most of the pipeline is now implemented on the stream processors. This makes CUDA GPUs much more easily programmable than was previously possible.

FIGURE 2.1: Architecture of the Nvidia GeForce 6800 GPU, showing pipelined design with separate units for Vertex processing, Rasterization and Blending (Nvidia, 2006)

FIGURE 2.2: Architecture of the Nvidia TESLA GPU, showing unified design with general purpose streaming processors (Lindholm et al., 2008)

FIGURE 2.3: A representation of the graphics pipeline as implemented on CUDA GPUs (Luebke and Humphreys, 2007)

#### 2.1.1 GPU Programming Frameworks

#### 2.1.1.1 Nvidia CUDA

As well as the CUDA platform itself, Nvidia actively develop a programming model for its GeForce, Quadro and Tesla processors. It is highly scalable and will run on an arbitrary number of processors without the need to recompile. This is required because of the vast and varying number of processor cores in modern GPUs (Nvidia, 2008). As observed by Garland et al. (2008), the CUDA framework allows a programmer to use the massively multi-threaded nature of GPUs for a wide range of highly parallel problems. While this was possible previously, using graphics APIs, CUDA relieves the programmer of the requirement of intimate knowledge of the target hardware. Additionally, it removes the daunting task of having to negotiate a complicated and unfamiliar language, as was previously the case when targeting different parts of the graphics pipeline. All of this allows the programmer to instead "focus on the important issues of parallelism - how to craft efficient parallel algorithms" (Garland et al., 2008, chap. 2).

CUDA programs consist of two parts;

• The host program - This can be one or multiple threads, running on the CPU

Parallel kernels - CUDA kernels are scalar sequential programs which execute on the GPU. These sequential programs operate on a grid of thread blocks, and must be able to be execute independently.

As an example, consider the loop in Listing. 1.1 The code iterates over a grid of data and performs the function at each point one at a time. The parallel version in listing. 1.2 performs the same function, but rather than looping through, each point is processed essentially simultaneously. (Garland et al., 2008)

```

void serial_function (int n, float a, float *x, float *y)

{

for (int i = 0; i<n; i++)

y[i] = a*x[i] + y[i];

}

//perform on 1M elements

serial_function(4096*256, 2.0, x, y);</pre>

```

LISTING 2.1: A standard C function

```

void gpu_function (int n, float a, float *x, float *y)

{

int i = blockIdx.x*blockDim.x + threadIdx.x;

if (i<n) y[i] = a*x[i] + y[i];

}

//perform on 1M elements

gpu_function<<4096, 256>>(n, 2.0, x, y);

```

LISTING 2.2: The same function as might be written for execution on a CUDA supported GPUNvidia (2013a)

#### 2.1.1.2 openCL

OpenCL is a parallel programming standard, with notable contributors such as Apple, ARM, AMD, Samsung and NVidia. It allows programs to take advantage of a very diverse array of processing devices such as GPUs CPUs DSPs and FPGAs. The standard is open source and provides mechanisms for hardware vendors to add access to hardware specific features (Nvidia, 2013d). Listing 2.3 shows and example of the previously shown GPU function as expressed in openCL.

```

float gpu_function (float a, float *x, float *y)

{

return y = a*x + y;

}

kernel void function(global write_only y, global a, global x)

{

int i=get_global_id(0);

y[i]=gpu_function(2.0, x[i], y[i]);

}

```

LISTING 2.3: An example of a functiuon as might be written for OpenCL

#### 2.2 Obstacles to using GPUs for scientific calculations

There are a number of caveats which must be kept in mind when using GPUs for calculations for which they were not designed. Graphics processing is highly tolerant to small errors so GPUs have not traditionally included error checking and correcting (ECC) memory systems. Scientific calculations, on the other hand, are highly sensitive to error. In response to this uncertainty, Haque and Pande (2010) have investigated the implications of using GPUs with non-ECC memory in non graphics calculations.By running a memory test program on more than 50,000 GPUs from the Folding@Home project, it was demonstrated that there is a statistically significant probability of transient errors occurring in GPU memory.

However, in response to the requirements of the scientific research community, GPU manufacturers have developed architectures specifically designed for general purpose processing.

Nvidia Fermi is one such architecture, developed from the start to be well suited for GPGPU purposes. It is described in detail in its whitepaper (P.Glaskowsky, 2009). Fermi finally introduces ECC memory protection for DRAM, as well as shared memories, L1 and L2 cache, and register files. Another notable improvement is double precision floating point performance, which was less important for graphics processing (which typically consists of single precision, 32 bit calculations), but very important for scientific calculations.

Even with ECC RAM there may be other precautions required when considering floating point accuracy on GPUs. While Nvidia GPUs with compute capability 2.0 and higher (Tesla M series and onwards) are compliant with the same IEEE 754 standard as CPUs for double precision floating point operations, Whitehead and Fit-florea (2011) suggest that there may be further precautions required to ensure accuracy when using Nvidia GPUs. There are fundamental differences in rounding modes on GPUs when compared to x86. as described in Whitehead and Fit-florea (2011, chap. 4.7) "rounding modes are encoded within each floating poin instruction instead of dynamically using a floating point control word". Unlike CPUs, There is no mechanism to indicate overflowed or underflowed calculations, or calculations with inexact logic. This implications of this are discussed later in the paper; while it is possible to produce the best floating point result for simple math operations, problems arise with more complex functions. While the same input will yeild the same results in an individual IEEE 754 compliant operation, differences in the potential sequencing of operations in GPUs, compared to CPUs, may mean differences in numerical results, even in newer hardware.

The authors offer some recommendations to ensure accuracy and performance; taking advantage of CUDA library functions (which have been written with these caveats in mind), careful comparison of results, and knowledge of the capabilities of the specific GPU being used.

#### 2.3 Scientific applications of current GPU technology

GPUs have found use in a wide variety of fields. Cardenas-Montes et al. (2014) Describe their efforts at performing an accurate calculation of cosmic shear using GPUs. Cosmic shear describes the distortion of the observed shapes of distant galaxies as their light passes through gravitational potential, a phenomenon known as gravitational lensing. According to Cardenas-Montes et al. (2014), measuring cosmic shear allows the mass distribution causing the distortion to be derived. This ultimately allows the measurement of the accelerated expansion of the universe.

This calculation is highly computationally intensive, fitting with  $O(N^2)$ , and it is suggested that all previous attempts used a simplified approach to allow the calculation to be completed in a reasonable timeframe, at the cost of precision.

The code is written for an Nvidia Tesla c1070 card, which is a Fermi architecture card. When compared to the same calculation performed on the CPU, the new GPU code represents a 68-fold speed increase. While this shows that GPUs are very powerful if you have the right problem, it also highlights the importance of well considered memory management when constructing GPU programs. The authors demonstrated that the best performance could only be achieved after tuning copy patterns, chunk size, and cache utilization.

Anthopoulos et al. (2013) offer an improved GPU acellerated cell-list approach. Celllists are important in the field of molecular dynamics as they are used to show atomic interactions within a given radius. Again, not only is this problem highly computationally expensive, but it is not trivial to parallelise.

The authors benchmarked their improved algorithm extensively both for speed, an accuracy compared to the same algorithm when run on a CPU. Total runtime is measured as well as each discrete part of the process, this allows more detailed anaysis of where the best performace gains are, and which areas perhaps require further optimisation. To test accuracy it was deemed an unfair test to directly compare CPU and GPU results due to the differences in rounding methods on both as mentioned earlier. Instead, double precision results from the CPU code were cast to single then back to double precision to remove the need to presume rounding error in non-GPU code. Accuracy in this case is measured as deviation from the CPU results, and is shown to be accurate to four significant figures.

#### 2.4 HPC Systems which use GPUs

A look at the top500 supercomputer list shows suggests that GPUs are now widely used in high performance computing. Two of the machines in the top 10 use GPU accelerators, Titan and Emerald, both use Nvidia K20 devices. Titan currently holds the number 2 spot. In addition, GPU clusters are seeing increasing use in academic institutions. Emerald, currently one of the largest GPU clusters in Europe (e-infrastructure South, 2013), is shared between STFC and a number of universities.

#### 2.4.1 TITAN - Oak Ridge National Laboratory

Titan has a peak performance of 17.59 PetaFlops, and was once Number one in the Top500 supercomputer sites (Top500, 2013b), as of November 2013 it is still number 2. It has 18,658 nodes, standard ones "each with a 16 core AMD opteron 6274 processor and an Nvidia tesla K20 GPU" (ORNL, 2011b) as well as over 700 Terra-bytes of memory. Titan demonstrates well the space and power efficiency of GPUs, as despite occupying the same space as its predecessor, Jaguar, and only using marginally more power, Titan outperforms Jaguar by a factor of 10 (1.75 PFlops for Jaguar as compared to 17.59 for Titan) owing to the fact that it has a much higher ratio of GPUs to CPUs.

Researchers working with ORNL (2011a) put extensive consideration, in the years before Titan was completed, into appropriate software which would be able to take full advantage of Titans then unique configuration. A selection of 6 codes was made, all from different scientific disciplines. These codes were then adapted to allow them to use the system to its full capability. These efforts highlight the importance of an awareness of the capabilities of specific hardware within a GPU cluster. Poor planning and lack of consideration of memory capacity and throughput, particularly in a GPU, can have a drastic effect on the performance of software.

Some of the problems Titan is used to solve include: Nanoscale materials analysis, to aid development of new magnets to improve designs of motors and generators; detailed modelling of the combustion of fossil fuels with the aim of improving the efficiency of internal combustion engines, and to reduce their impact on the environment; and detailed atmospheric modelling, to further climate change research.

#### 2.4.2 Emerald

Emerald has a capacity of 114 TerraFlops and includes 372 Nvidia Tesla processors. Each node has 2 6-core Intel Xeon X5650 processors and either 3 or 8 Tesla M2090s (e-infrastructure South, 2013). The system is used by the STFC and universities of e-Infrastructure South consortium (Oxford University, 2013). Emerald serves as a good indicator that there is demand for GPU accelerated clusters within Higher Education. The literature shows that there is high demand and utilisation of GPUs in a wide range of scientific disciplines. Some valuable information regarding designing GPU clusters, developing GPU codes, testing and benchmarking is available and will be put to use in guiding our own efforts.

### **Chapter 3**

# **Vega GPU Cluster**

Investigation into existing GPU systems currently being used to accelerate scientific computation has demonstrated a significant speedup of simulations, modelling and visualisation. In order to evaluate the benefit such a system could have for research at the university of Huddersfield it was necessary to deploy a small GPU cluster. This chapter details the assembly, installation and testing of this system. The cluster is integrated into the University campus network and is accessible internally by students and staff. The Microsoft Windows HPC server software was used to deploy the GPU cluster.

#### 3.1 The Microsoft Windows HPC Platform

Microsoft provides tools to allow deploying and managing a cluster using Microsoft Windows Server. Microsoft (2014c) detail the deployment of a complete HPC system using Microsoft tools.

GPU graphics and compute drivers are widely available for Windows systems (Nvidia, 2013c). Windows HPC cluster manager provides a mechanism to include drivers with operating system images, to simplify the deployment process. In addition, Microsoft also provides a number of tools to aid in testing and benchmarking a windows HPC cluster (Micorsoft, 2014). The Message Passing Interface (MPI) is a standard for cross process communication designed for parallel compute systems. The MPI system included with Windows HPC deployments, MSMPI, is Microsofts implimentation of the

MPI-2 standard (Microsoft, 2014a). It is compatible with MPICH2, which makes porting MPI code from other platforms, such as Linux, relatively simple.

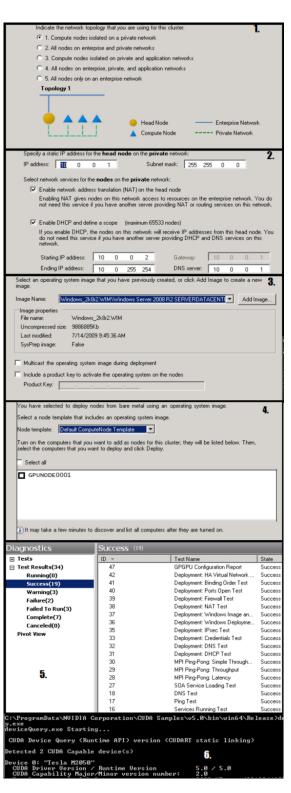

#### 3.2 Cluster Layout

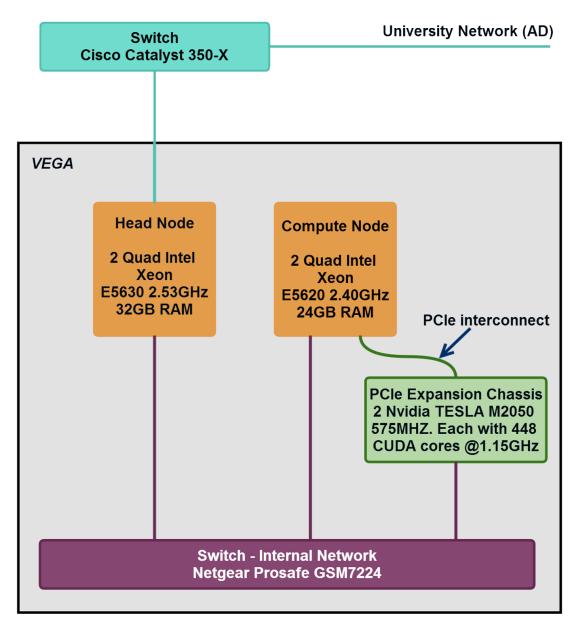

The following hardware was available for the deployment:

| Item                                                                | Description                                                                                                                                                                                        |

|---------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Netgear ProSafe GSM7224                                             | 24 port Gigabit network switch                                                                                                                                                                     |

| Dell Poweredge R410                                                 | 1x Quad core octo-thread Xeon E 5630<br>CPU running at 2.53 GHz, 32 GB RAM.                                                                                                                        |

| Dell Poweredge C6100                                                | 4 node chassis currently with 2 nodes<br>installed. each with the following spec:<br>2x Quad core octo-thread Xeon E5620<br>CPUs, running at 2.4GHz, 24 GB RAM,<br>and approx 400GB local storage. |

| Dell Poweredge C410x PCIe Ex-<br>pansion Chassis + 1 interface card | This chassis can host up to 16 GPUs and<br>is connected to a compute node using a<br>PCIe interface card (Dell, 2014)                                                                              |

| 2x Nvidia Tesla M1020 GPUs                                          | These are FERMI architecture cards with 448 processor cores running at 1.15 GHz, with 3GB of ECC GDDR5 RAM with a clock speed of 1.546 (Nvidia, 2013e)                                             |

TABLE 3.1: Hardware available for VEGA

As the Poweredge C6100 is a four node chassis, it was selected to act as compute node. There is only a single PCIe interface card available so initially there is only a single compute node, with the option of adding more in the future. The Poweredge R410 acts as head node.

In line with Microsoft suggestions, the head node has 2 NICs installed (Microsoft, 2014c). One is connected to the University network, the other is connected to a Gigabit switch, which is used to communicate internally with the compute nodes. This topology is illustrated in Table. 3.1.

FIGURE 3.1: Current VEGA hardware layout and network topology.

#### 3.3 Deployment

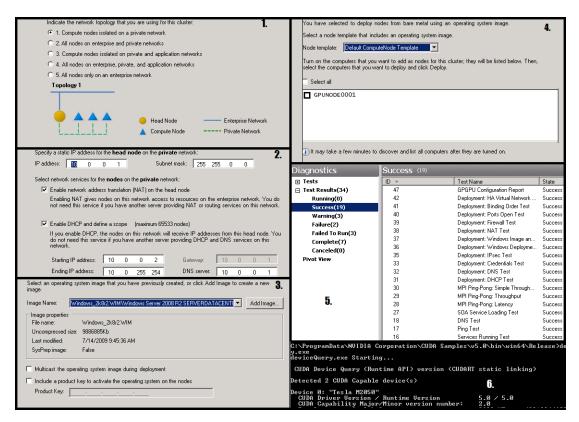

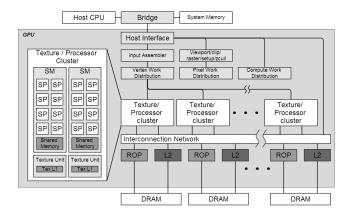

Initially, all hardware was tested to ensure it was viable. According to the deployment procedure outlined by Microsoft (2014c), was to install Windows Server 2008r2, which is a standard procedure. Once installed, the Head node is connected to the university network and then added to Active Directory by specifying the domain name. At this point the following steps are performed to deploy the GPU cluster:

• Microsoft HPC Pack is installed on the head node.

- The head node is attached to the private Gigabit switch.

- Compute nodes are deployed by first connecting them to the Private network then booting to PXE. The Windows HPC software will then load an operating system and required middleware over the network. This differs from the procedure offered by Microsoft (2014c), which suggests attaching nodes which have already been configured with windows server and HPC pack. As the nodes did not already have Windows installed, it was deemed much simpler to have the head node push out preconfigured system images to the compute node.

- Finally, drivers for the TESLA cards are installed on the compute node directly (Nvidia, 2013c).

A summary of the deployment steps required to deploy the GPU cluster, VEGA, can be seen in Fig. 3.2.

#### 3.4 Testing

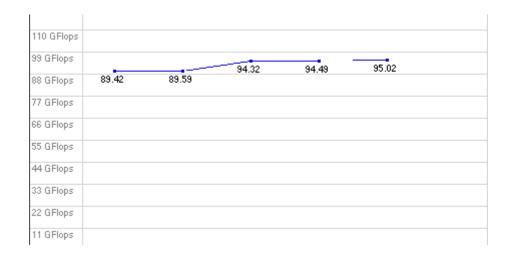

The Windows HPC cluster manager includes a number of diagnostic tests to verify cluster deployment. All relevant tests when run on VEGA passed without any problems. The standard measure of performance of HPC systems, and the test used to measure systems for inclusion in the top500, is the LINPACK benchmark. The benchmark consists of "a dense system of linear equations" (Jack Dongarra and Stewart, 2013), and the ability of a system to process these is used as a measure of peak performance. The parallel implementation of LINPACK is known as High Performance LINPACK (HPL). Microsoft provides a self-tuning HPL utility, Lizard, to benchmark Windows clusters, the results and final tuned parameters of this can be seen in Fig. 3.3. This however does not include the extra performance provided by the GPUs, figures from Nvidia state that peak theoretical performance of each M2050 is 1.03 TFLOPS (Nvidia, 2013e).

More in depth tests were carried out to assess MPI and CUDA Functionality. A simple program, the source for which can be seen in Listing 3.4, was written to test MPI functionality. As seen in Fig. 3.5 MPI is fully functional on the cluster. After installing the CUDA toolkit (Nvidia, 2013b) a number of CUDA accelerated test programs are available. Fig. 3.6 shows a number of these running successfully.

FIGURE 3.2: Key steps when deploying VEGA: 1. Selecting Network Topology 2. Configuring NAT and DHCP to allow compute nodes to access outside network 3. Creating a system image for compute nodes 4. Finding bare metal machines to deploy as compute nodes 5. Checking relevant diagnostic tests pass 6. Checking CUDA functionality

Windows was chosen as the operating system to allow familiarity with users, and easy integration with the existing active directory network. In addition, running Windows allows the option of adding the cluster to the backburner render system in use at the university.

However, CUDA is also available for Linux. Were it required, necessary drivers are available to allow the same functionality, using a cluster middleware such as OSCAR or Warewulf (ORNL, 2005), (LBL, 2014).

Although cluster integrity was confirmed using test codes and benchmarking utilities, it was necessary to examine programming models and environments to allow users to develop new parallel code and parallelise existing serial codes.

| Parameter                              | Ν     | NB    | PMAP | Р             | Q         | Threshold |

|----------------------------------------|-------|-------|------|---------------|-----------|-----------|

| Final Value                            | 44992 | 304   | 0    | 2             | 12        | 16        |

| Parameter                              | PFACT | NBMIN | NDIV | RFACT         | BCast     | Depth     |

| Final Value                            | 0     | 4     | 8    | 2             | 1         | 1         |

| Parameter                              | SWAP  | L1    | U    | Equilibration | Alignment |           |

| Final Value                            | 2     | 0     | 0    | 0             | 16        |           |

| CPU only performance = 95.02 GIGAFLOPS |       |       |      |               |           |           |

FIGURE 3.3: Tuning HPL parameters using Lizard

```

#include "stdafx.h"

#include <iostream>

#include "mpi.h"

#include<Winsock2.h>

#pragma comment(lib , "Ws2_32.lib")

using namespace std;

int main(int argc, char* argv[])

{

int nTasks, rank;

MPI_Init(&argc,&argv);

MPI_Comm_size(MPI_COMM_WORLD,&nTasks);

MPI_Comm_rank(MPI_COMM_WORLD,&rank);

char hname[128] = "";

WSADATA wsaData;

\texttt{WSAStartup}(\texttt{MAKEWORD}(2\,,\ 2)\,,\ \texttt{&wsaData})\,;

gethostname(hname, sizeof(hname));

WSACleanup();

printf ("Number of threads = %d, My rank = %d\n, My Host = %s", nTasks, rank, hname)\leftrightarrow

;

MPI_Finalize();

return 0;

}

```

LISTING 3.4: Simple MPI test program, based loosely on the example from Mattotorang (2009)

```

Number of threads = 24, My rank = 10

, My Host = GPUNODE0001

Number of threads = 24, My rank = 13

, My Host = GPUNODE0001

Number of threads = 24, My rank = 4

, My Host = GPUNODE0001

Number of threads = 24, My rank = 3

, My Host = GPUNODE0001

Number of threads = 24, My rank = 16

, My Host = VEGA

Number of threads = 24, My rank = 0

, My Host = GPUNODE0001

Number of threads = 24, My rank = 11

, My Host = GPUNODE0001

Number of threads = 24, My rank = 23

, My Host = VEGA

Number of threads = 24, My rank = 2

, My Host = GPUNODE0001

Number of threads = 24, My rank = 7

, My Host = GPUNODE0001

Number of threads = 24, My rank = 14

, My Host = GPUNODE0001

Number of threads = 24, My rank = 6

, My Host = GPUNODE0001

Number of threads = 24, My rank = 15

, My Host = GPUNODE0001

Number of threads = 24, My rank = 5

, My Host = GPUNODE0001

Number of threads = 24, My rank = 9

, My Host = GPUNODE0001

Number of threads = 24, My rank = 1

, My Host = GPUNODE0001

Number of threads = 24, My rank = 21

, My Host = VEGA

Number of threads = 24, My rank = 12

, My Host = GPUNODE0001

Number of threads = 24, My rank = 8

My Host = GPUNODE0001

Number of threads = 24, My rank = 22

, My Host = VEGA

Number of threads = 24, My rank = 20

, My Host = VEGA

Number of threads = 24, My rank = 19

, My Host = VEGA

Number of threads = 24, My rank = 18

, My Host = VEGA

Number of threads = 24, My rank = 17

, My Host = VEGA

```

FIGURE 3.5: Output from MPI test program when run on all cores

```

Detected 2 CUDA Capable device(s)

steeted 2 CODM Capable device(s)

suice 0: "Tesla M2050"

CUDA Driver Version / Runtime Version

CUDA Capability Major/Minor version number:

Total anount of global memory:

(14) Multiprocessors, ( 32) CUDA Cores/MP:

GPU Clock rate:

Memory Clock rate:

Memory Bus Width:

L2 Cache Size:

Maximum Texture Dimension Size (x,y,z)

D=(2048, 2048, 2048)

Maximum Layered 1D Texture Size, (num) layers

Total anount of constant memory:

Total anount of shared memory per block:

Total number of registers available per block:

Warp size:

5.5 / 5.5

2.0

2688 MBytes (2818244608 bytes)

448 CUDA Cores

1147 MHz (1.15 GHz)

1546 Mhz

384-bit

786432 bytes

1D=(65536), 2D=(65536, 65535),

1D=(16384), 2048 layers

2D=(16384, 16384), 2048 layers

65536 bytes

49152 bytes

32768

Total number of registers available per block: 32768

Warp size:

Maxinum number of threads per multiprocessor: 1536

Maxinum number of threads per block: 1024

Max dimension size of a thread block (x,y,z): (1024, 1024, 64)

Max dimension size of a grid size (x,y,z): (65535, 65535)

Maxinum menory pitch: 2147483647 bytes

Texture alignment: 512 bytes

Concurrent copy and kernel execution: Yes with 2 copy engine(s)

Run time limit on kernels: No

Support host page-locked menory mapping: Yes

Alignment requirement for Surfaces: Yes

Device has ECC support: Enabled

CUDA Device Driver Mode (TCC or WDDM): TCC (Tesla Compute Cluster

Yes

Enabled

TCC (Tesla Compute Cluster Driv

pr)

Device supports Unified Addressing (UUA): Yes

Device PCI Bus ID / PCI location ID: 13 / Ø

Compute Mode:

< Exclusive (only one host thread in one process is able to use ::cudaSetDe

vice() with this device) >

vice 1: "Tesla M2050"

CUDA Driver Version / Runtime Version

CODA Driver Version / Runtime Version 5.5 / 5

[Tesla M2050] has 14 MP(s) x 32 (Cores/MP) = 448 (Cores)

> Compute scaling value = 1.00

> Memory Size = 49999872

Allocating memory...

Generating host input data array...

Uploading input data to GPU memory...

Testing misaligned types...

uint8...

Avg. time. 2.20405

5.5 / 5.5

uint8...

Avg. time: 2.234354 ms / Copy throughput: 20.840925 GB/s.

TEST OK

RGBA8...

Avg. time: 1.075146 ms / Copy throughput: 43.311323 GB/s.

TEST OK

132...

Avg. time: 1.212484 ms / Copy throughput: 38.405448 GB/s.

TEST OK

LA32...

Avg. time: 1.094878 ms / Copy throughput: 42.530758 GB/s.

TEST OK

RGB32...

Avg. time: 2.094896 ms / Copy throughput: 22.228315 GB/s.

TEST OK

RGBA32_2...

Avg. time: 1.102998 ms / Copy throughput: 42.217677 GB/s.

TEST OK

RGBA32_2...

[Matrix Multiply CUBLAS] - Starting...

GPU Device 0: "Tesla M2050" with compute capability 2.0

MatrixA(320,640), MatrixB(320,640), MatrixC(320,640)

Computing result using CUBLAS...done.

Performance= 491.03 GFlop/s, Time= 0.267 msec, Size= 131072000 Ops

Computing result using host CPU...done.

Comparing CUBLAS Matrix Multiply with CPU results: PASS

```

FIGURE 3.6: GPU test programs included with CUDA toolkit (Nvidia, 2013a), from top to bottom: Device Query, Testing Aligned Types, Matrix Multiplication

### **Chapter 4**

# Platforms and Programming Environments for Scientific Data Visualisation and Processing

There is a need to develop parallel programming environments to aid software development for parallel computer architectures. However, other than those already outlined in chapter 2, there are still few mature parallel programming environments. Perhaps more important is the absence of tools and IDEs that allow for simple debugging and testing of parallel software with the ease and reliability of those established for traditional serial programs. This is particularly true for software designed to make use of accelerators. While debugging and development tools do exist for accelerators such as GPUs, they are platform specific (for example Nvidia Nsight (Nvidia, 2014)) meaning that developing parallel software for heterogeneous systems remains a comparatively convoluted process.

This is an active area of research and calls for publications in this area regularly appear with significant funding interest from research councils, as in 2020 (2013). This chapter covers the environments selected for use on VEGA, based on the findings in Chapter 2, with particular focus on systems that support visualisation of scientific data, and multi-node parallelisation with GPU acceleration.

#### 4.1 Visualisation

Visualisation of scientific data is not a novel concept. Matlab is used extensively to plot 2D and 3D images. Similarly, CFD and MD packages such as ANSYS (INC, 2014) and DL\_POLY (STFC, 2014) provide inbuilt software for visualisation of processed data. When evaluating the available visualisation software for deployment on VEGA, Vislt, a parallel visualisation tool, was chosen for its focus on parallel processing using MPI, as well as GPU accelerated rendering. In addition, it boasts compatibility with a vast range of CAD, CFD, MD, graphing and mathematics software (LLNL, 2013). Vislt is highly flaxible in the data it can display, thanks to software functions which allow data to be structured appropriately programatically, in C or FORTRAN.

#### 4.2 Multi-Node parallelism

An integral part of any HPC system is a mechanism to allow programs to utilise multiple CPU cores which do not necessarily occupy the same host node. MPI has proven itself over the past couple of decades in this regard and has become a standard used in the vast majority of HPC deployments. MPI supports a wide selection of programming languages such as C++ and and Java (Forum', 2014). Some key concepts to consider when using MPI; Communicators, Point to Point operations, and Broadcast and Collection. Communicators are used to group MPI processes related to the same task. Most MPI operations must specify a communicator, this ensures that the operation only effects those processes which are in the same communicator (for example MPI\_COMM\_WORLD). Point to Point operations, such as MPI\_Send and MPI\_Recv, are used to send data from one rank to another in a one to one relationship. Broadcast and Collection operations such as MPI\_Bcast and MPI\_Scatter are one to many or many to one operations, and are useful for dividing data among processes, and then collecting after processing.

There are a number of distributions which comply with the MPI standard. MPICH is the (MPICH, 2014) is perhaps one of the most widely used. Most HPC clusters will offer a choice of MPI version. Some other options are Open MPI and MSMPI. MSMPI is an MPI version distributed by Microsoft. It is fully MPICH compatible and is tightly integrated with the Windows HPC job scheduler, the scheduler used in VEGA, allowing simple submission of MPI tasks to the cluster. This close integration makes MSMPI particularly suited for Multi-node parallel software when Windows HPC is used (Microsoft, 2014b).

Options other than MPI include OpenMP which allows "multi platform shared memory parallel programming" (Board, 2013). This offers some flexibility when developing parallel software. The programming experience is very similar to that of using MPI, with the added benefit of shared memory. Parallel Virtual Machine (PVM) is an approach which aggregates discrete systems which do not necessarily need to have the same hardware or operating system. PVM allows a heterogenous cluster of machines to appear as a single virtual machine (ORNL, 2009).

#### 4.3 GPU Programming Framework

The two main GPU programming frameworks remain Nvidia CUDA and OpenCL, although more are gaining traction, such as C++ AMP, in development at Microsoft. A number of studies, such as those carried out by (Karimi et al., 2010), and (Fang et al., 2011) have shown that the in many cases, CUDA is able to outperform OpenCL when both are given the same task. This, coupled with the Nvidia hardware available in VEGA and existing familiarity with Nvidia tools, are all factors contributing to the choice to use CUDA for GPU processing. Some important things to bear in mind when developing CUDA software is effective memory management, as well as device management. When using GPUs to process data, the most efficient use of the device is if all cores are occupied. This requires that the host program can stream enough data. This does not necessarily mean filling GPU memory, as depending on the task being executed on each GPU core, a smaller data stream may be enough make full use of the hardware. Minimising copy operations will also help towards efficient use of the hardware. For example if a process loop (eg a matrix multiplication) only uses a half of the available CUDA cores, then organising into batches, so that two data ranges are processed simultaneously, will reduce time spent copying to and from the device. Also important to consider is the fact that devices can only be controlled by a single host thread at a time,

# Platforms and Programming Environments for Scientific Data Visualisation and Processing

so programs which use multiple GPUs must take care to check which GPU is being requested to avoid crashing.

The challenge of parallel programming is a problem that is yet to be addressed fully. The approach taken as part of this research is outlined in the following section in the form of three case studies. The first two of these case studies were published in the proceedings of the Science and Information conference 2014 (Newall et al., 2014). In addition, the final two studies were published as a chapter in in the Springer series book, Studies in Computational intelligence. These publications can be seen in appendices D and E respectively.

# Case Study 1: Visualisation of large datasets

As models and datasets become larger and more complex, new systems are required to enable useful analysis. To support the need of researchers at the University, it was deemed necessary to deploy a visualisation tool which could work with large or complex datasets.

To this end, and existing software, Vislt, was obtained and installed on VEGA. Vislt is a software developed by the Lawrence Livermore National Laboratory (LLNL), described as "Parralel, Interactive, Visualisation" (LLNL, 2013). It is specifically designed to utilise HPC resources to enable interactive simulation of terrascale datasets, and supports GPU accelerated rendering.

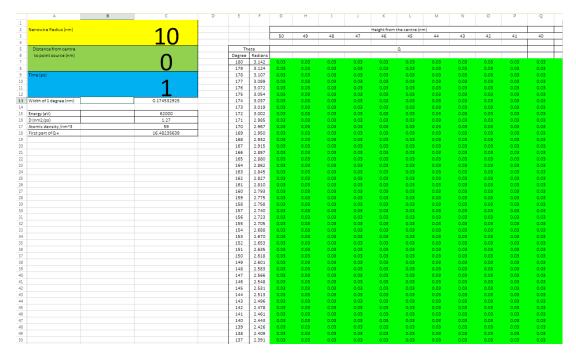

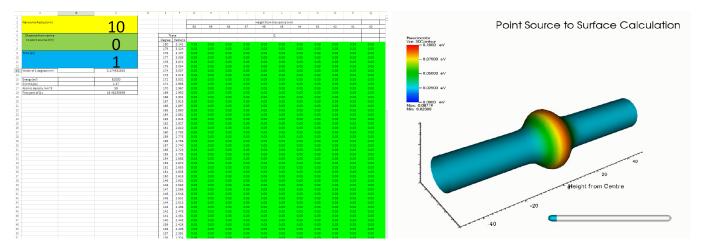

#### 5.1 Electron Microscopy Data

The Electron Microscope Materials Analysis group (EMMA) at the university, is tasked with "the interaction of energetic particles with matter" (EMMA, 2014). The research carried out in this area generates large volumes of data, both through experimentation and simulation. One simulation in particular was of interest as the visualisation methods being employed at the time, a large colour coded spreadsheet, were not deemed adequate. The data in question is an array of cells, the value of each representing the energy of a point on a cylinder, and the values change over time. The spreadsheet that was in use was unwieldy and cannot all be seen at once as seen in Fig 5.1. This made proper analysis difficult, ideally the data would be shown as points on an actual cylinder as a 3D contour. For these reasons the data was deemed a good candidate for case study.

FIGURE 5.1: Visualisation method before VisIt

#### 5.2 Vislt

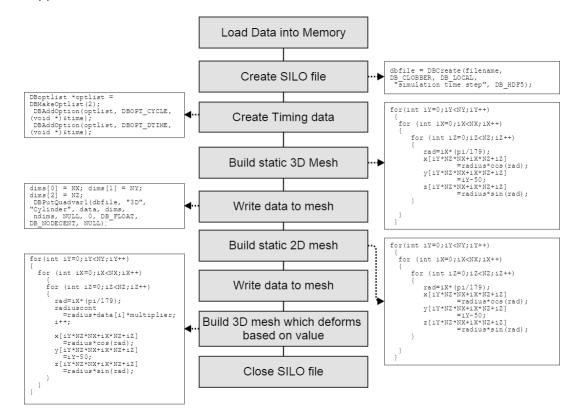

Visit displays data that is defined on 2D or 3D meshes, this presents a challenge; The electron microscopy data is simply a comma delimited list of values. The solution was to build a software tool to format this data, and save it to an appropriate file format. The SILO library was developed by LLNL fo use with Vislt in situations such as this, and allows production of data meshes programmatically (LLNL, 2010). Following the recommendations in the SILO users guide, the software was built uses standard SILO functions to save the data in 3 different formats:

- A 2D mesh where the data is represented by colour (similar to the function of the original spreadsheet)

- A 3D Mesh representing a cylinder (also colour coded)

and finally a 3D mesh which deforms based on the value of each point over time (contour).

Fig. 5.2 shows a summary of important parts of the program, full listings can be seen in appendix 1.

FIGURE 5.2: Program flow for the SILOWRITE code

#### 5.3 Evaluation of Results

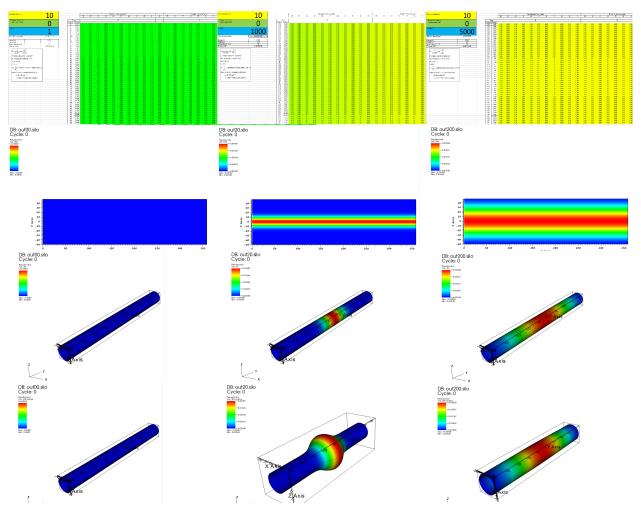

Fig. 5.3 Shows a few images of each visualisation method at different time steps. The final 3D contour model fulfils the original requirements of the project and allows real time interactive analysis of the simulation data. The main advantage of this model is that all the data for each time step can be seen at once. The animation can be easily saved to video.

Although Vislt is designed for visualisation scientific data, unless the data is already formatted to fit one of the file types that Vislt supports, it is necessary to pre-process the data from often a large repository to structured data suitable for visualisation. This

FIGURE 5.3: Comparison of Visualisation methods, from top to bottom: Original spreadsheet, 2D Mesh in Vislt, 3D mesh in Vislt, 3D contour mesh in Vislt

illustrates that visualisation of raw scientific data is not a straight forward process, and that the main effort is still the responsibility of a software engineer.

# Case Study 2: Accelerated Processing of Radio Telescope Data Using CUDA

The Serch for Extra Terrestrial Intelligence (SETI) is a group whos mission is to serch for non earth signals from space, in the hopes of locating intelligence. One of the main aspects of this endevour, is the analysis of vast amounts of radio telescope data. There have been numerous projects which have intended to accelerate this process such as processing the data into images to speed up human analysis of the data, even allowing enthusisasts at home to look through the data. But it is a time consuming task, even with these methods the data is being collected faster than it can be analysed so more efficient methods are required. To this end, the SonicSETI project has started sonifying the data. Sonification is a process whereby a stream of data is converted into sound. Studies have shown that sonified data can be reviewed by humans at a much greater rate than visual anaylsis, and patterns are much more descernable from background noise (Kramer, 1993). Perhaps the most prominent example of sonification is that of the Geiger counter, which uses audible clicks which increase in frequency as radiation levels increase. While the sonified data may be much easier to analyse, processing the data is a time consuming proesss in itself, so investigation was started into the potential benefits of GPU acceleration.

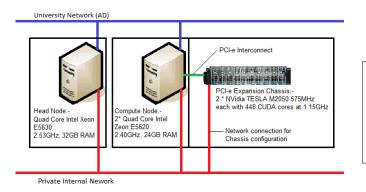

#### 6.1 The SETIFFT software

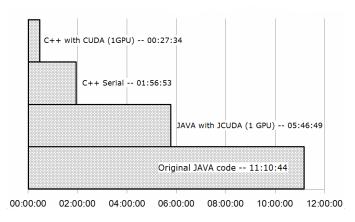

In order to sonify the data, a piece of software was written in JAVA by Paul Lunn for the Sonic SETI project. Fig. 6.1 shows the program logic. In order to asses which parts of the software would best benefit from acceleration, different sections of the code were timed, these timings can be seen in Table 6.1. In each test, the software performs 244 FFTs using a 2GB file as input, measurements are averaged over 10 separate runs.

FIGURE 6.1: Program flow of the SETIFFT software

| Action                   | Time Taken (Ms)    |

|--------------------------|--------------------|

| Read data                | 3713182 (1:01:53)  |

| Perform FFT              | 4491666 (1:13:52)  |

| Calculate Power Spectrum | 477218 (0:07:57)   |

| Save to File             | 1344062 (0:22:24)  |

| Total run time           | 10026326 (2:47:06) |

TABLE 6.1: Timings for original JAVA program

Timings showed that the program spent most of its time reading in data and performing the FFT. As each FFT takes over a minute, and the full datasets can require over 500 FFTs, the first step was to replace the serial FFT with a parallel, GPU accelerated one. The Nvidia CUFFT library fits this purpose, and there exist JAVA wrappers for its functions (CUFFT is C). Using this library, FFT precessing time was successfully reduced by over 30 times, as seen in Table 6.2

| Action                   | Time Taken (Ms)    |

|--------------------------|--------------------|

| Read data                | 3801657 (01:03:22) |

| Perform FFT              | 916464 (00:15:16)  |

| Calculate Power Spectrum | 483007 (00:08:03)  |

| Save to File             | 1404548 (0:23:25)  |

| Total Run Time           | 5711437 (1:35:11)  |

TABLE 6.2: Timings for Java program with wrapped CUDA functions

In order to improve read and write time, and to make better use of CUDA functions, the program was rewitten in C++, first with a serial FFT as seen in table 6.3, then with CUFFT as seen in table 6.4.

| Action                   | Time Taken (Ms)   |

|--------------------------|-------------------|

| Read data                | 29686 (0:00:27)   |

| Perform FFT              | 1541246 (0:25:41) |

| Calculate Power Spectrum | 56436 (0:00:56)   |

| Save to File             | 29686 (0:00:30)   |

| Total Run Time           | 1810008 (0:30:10) |

TABLE 6.3: Timings for C++ with serial FFT

| Action                   | Time Taken (Ms) |

|--------------------------|-----------------|

| Read data                | 17344           |

| Perform FFT              | 90720           |

| Calculate Power Spectrum | 70781           |

| Save to File             | 17344           |

| Total run time           | 277674          |

TABLE 6.4: Timings for C++ with CUFFT

#### 6.1.1 Optimising CUDA performance

The original software, as well as initial CUDA versions, read enough data to perform a single FFT, process it, and write to file. However this is an inefficient use of GPU memory. Each element in the complex array used to process the data is 16 bytes in size, and FFT size is 8388608. Accounting for the output array, the 3GB on the Tesla cards can hold enough data to process 10 FFTs for each copy operation. Table 6.5 shows timings for memory copy and FFT execution time.

| Batch size | Copy operations | Time (Ms)       |

|------------|-----------------|-----------------|

| Single FFT | 488             | 90720 (0:01:31) |

| 5 FFTs     | 98              | 36225 (0:00:36) |

| 10 FFTs    | 50              | 27313 (0:00:27) |

TABLE 6.5: Timings for C++ with CUFFT and MPI, running on multiple GPUs

Making these changes decreased FFT processing time for a 2GB file by 63.4 seconds, an improvement of over 69%.

#### 6.1.2 Using MPI to increase performance

To utilise the second GPU in the system, and to allow the program to scale to even larger systems, the program was modified to implement MPI. Fig. 6.2 shows the program structure of the initial version. Files are read and written by the master process rank, and data is sent to and from the worker ranks using MPI.

This initial MPI version was successful in reducing actual processing time, but the large MPI data transfers added significant overhead, in excess of any performance gained in processing. The solution was to make use of the shared storage available on VEGA to remove the need for large MPI send/recieve operations. Fig. 6.3 shows the structure of the final version of the software. Rather than data being sent to each rank using MPI functions, each rank opens the relevant file directly. In this version MPI messages are only used to tell the workers which files to open and where to start and stop reading.

Table. 6.6 shows timings for the final code. Each rank processes a share of the data, and are timed simultaneously, hence two timings for each section of the program.

| Action                   | Time Taken (Ms)(rank 0) | Time Taken (rank 1) |

|--------------------------|-------------------------|---------------------|

| Read data                | 118043                  | 145642              |

| Perform FFT              | 12310                   | 12570               |

| Calculate Power Spectrum | 40271                   | 40304               |

| Save to File             | 118043                  | 145642              |

| Total run time           | 249777                  |                     |

TABLE 6.6: Timings for C++ with CUFFT and MPI, running on multiple GPUs

FIGURE 6.2: Program flow of the initial MPI program

#### 6.2 Evaluation of Results

It can be seen that read/write time is increased in the MPI version compared to the single process. This is because each process is accessing the same file simultaneously. Table 6.7 shows times when the program is run with two files from the dataset. As the datasets are often larger than 8GB, they are split into 2GB files (SETI, 2013a), so this would not be outside the normal use of the software.

When each process is able to work on a separate file, read/write time is similar to the time taken when working on a single file, even though double the amount of data is being processed. During normal operation, the only time multiple process ranks would

FIGURE 6.3: Program flow of the final MPI version

access the same file would be if there were an odd number of input files. Were the software to be developed further it may be worthwhile to factor for this by ensuring that the final file in an odd numbered set is only processed by one rank.

| Files | Total FFTs | Read/Write time |

|-------|------------|-----------------|

| 1     | 244        | 145642          |

| 2     | 488        | 145816          |

TABLE 6.7: Read/write time for the MPI software when reading from different numbers of files

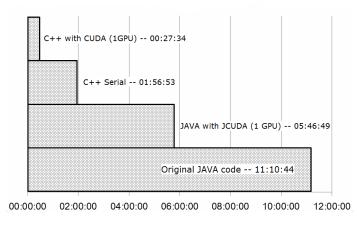

Figure 6.4 compares total running times of each significant version of the software, running with a full dataset 5GB in size (split into 2GB files). Through parallelisation (using both CUDA and MPI) and optimisation it has been possible to significantly accelerate the process of sonifying the radio telescope data.

FIGURE 6.4: Total running times of each version

The primary implication of this is that the rate at which the data can be analysed is greatly increased, and the time between any potential discoveries is decreased. This case study is evidence that simply using more powerful hardware will not always bring proportional performance improvements without efficient and sustainably designed software.

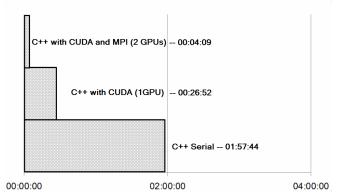

# Case Study 3: CUDA Accelerated Analysis of Wavelength scanning Interferometry Data

Optical interferometry is a widely used surface metrology technique. Wavelength scanning interferometry developments have been made that allow the process to be immune to environmental noise using phase compensation. However this compensation as well as data analysis processes limit performance, and hamper efforts to inspect this data as the measurement takes place. The paper Muhamedsalih et al. (2012) details a method which uses CUDA to accelerate this process with a single GPU. However, while the results were promising, it wass still not possible to achieve the real time analysis that was desired.

#### 7.1 The Interferometry Software

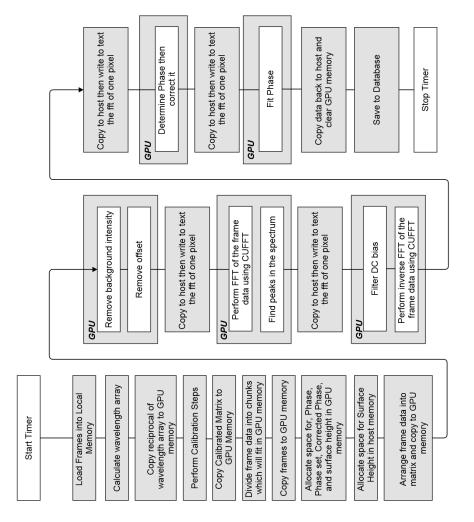

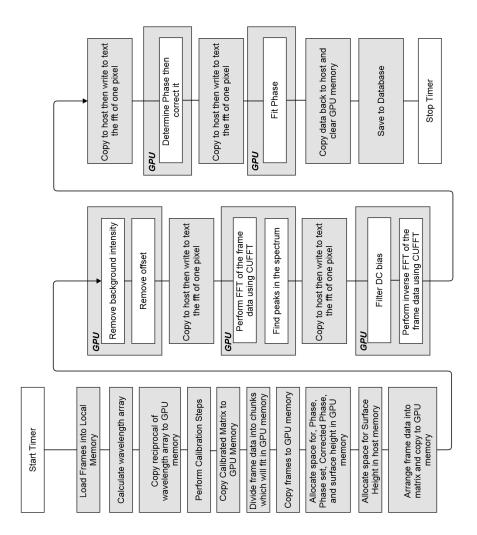

The original CUDA program loads a set of bitmap frames, and the noise cancellation is calibrated by loading a matrix which has been processed by MATLAB. After calibration the data is processed through an FFT algorithm, and all data is saved to disk. Fig. 7.1 shows a summary of the function of the program. As with the work carried out in the previous case study, GPU acceleration comes in the form of a parallel FFT algorithm, CUFFT, as well as a few other mathematical operations.

FIGURE 7.1: Program flow for the original CUDA code

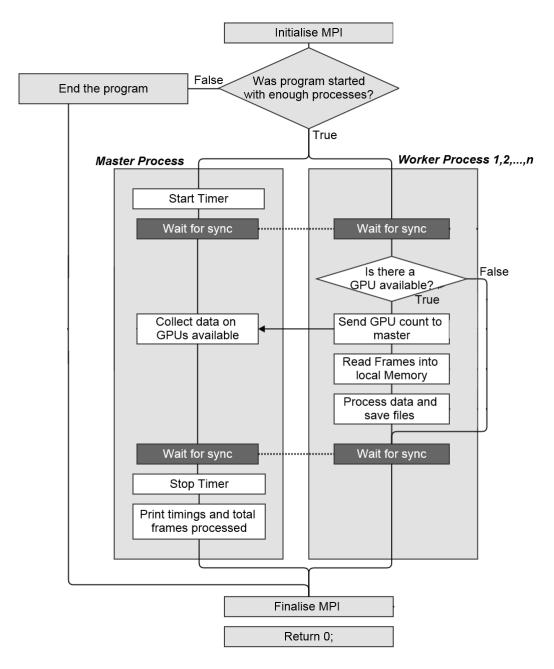

#### 7.2 Improving Performance Using MPI

Using the lessons learned in the previous study, the program was modified to allow it to use multiple GPUs. After including the necessary MPI libraries the program was modified in a way which results in a structure closely resembling the original program, but which is duplicated over multiple processes which can each claim its own GPU. The intended outcome of this modification is a doubling of the total throughput, to allow the processed data to analysed closer to real-time. The modified program structure is shown in Fig. 7.2.

FIGURE 7.2: Program flow for the MPI version using multiple GPUs

#### 7.3 Evaluation of Results

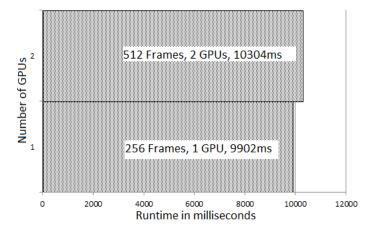

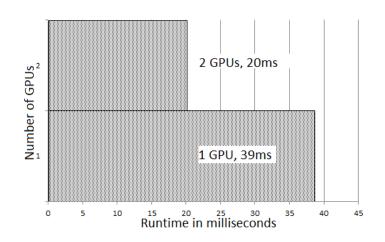

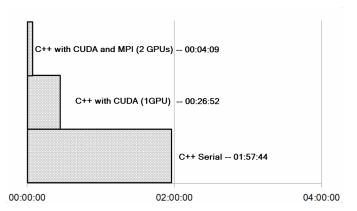

The graph in Fig. 7.3 shows total running times for both the original software and the MPI version. It is important to note that in this graph the MPI version is processing double the amount of data with only a small increase in running time. By dividing the running time by the number of frames processes we can calculate a representative per-frame processing time for each version, this is shown in 7.4.

48

FIGURE 7.3: Total running times for each version

FIGURE 7.4: Representative per-frame processing time

# Conclusion

Existing GPU clusters were evaluated, with a focus on the Higher Education context and scientific research. This research allowed informed decisions regarding the deployment of our own system, and lead to the deployment of VEGA, a small GPU cluster integrated into to campus network forming part of the institutional grid. With this system in place it was possible to investigate and evaluate different platforms and programming environments to support the goal of highly parallel task and data processing. Using case studies the suitability of the GPU cluster was evaluated. The first case study showed that useful visualisation of seemingly abstract data could be achieved using the appropriate platforms, and enabled a level of analysis previously not possible for this data. By using the CUDA GPU programming model, as well as MPI, significant performance gains were possible, both for sonification of radio telescope data, and analysis of wavelength scanning interferometry data. While the initial objective was to use CUDA with Java and C++ to accelerate applications using multi-core GPU devices, It has been possible to achieve even greater performance gains though implementation of multisystem MPI code, to allow multiple GPUs to process data. Not only will the CUDA implimentations scale automatically to larger, faster GPUs, but MPI allows scaling to multi node GPU clusters.

The project has shown that even a modest investment in GPU systems would assist research in higher education institution, as with a comparatively small physical and energy footprint, data processing has been accelerated to levels comparable to a much larger HPC cluster.

It has become evident through the work carried out that the major obstacle in achieving potential speed up using GPU technology is lack of parallel platforms for creating, debugging and tenting parallel programs. To make effective use of a GPU cluster implies a greater effort on the part of the software author, compared to other HPC programming. Future investment in integrated and development environments is necessary to enable better utilisation of the existing GPU hardware. These are issues included as part of the EPSRC E-Infrastructure roadmap and Software and an infrastructure strategy (EPSRC, 2014a). There were a number of calls from the EPSRC council related to Software of the Future which will attempt address these issues (EPSRC, 2014b).

# **Further Work**

The case studies detailed here have been designed to scale to much larger systems through using MPI. Running the software on larger systems will allow the efficiency and performance of the software to be assessed, giving opportunity to discover bottlenecks and develop more concrete methods for software design on GPU clusters.